## Design of Multi Modulation Scheme for Software Defined Radio using FPGA

G. Vishnuvardhan Rao, A.Mohammed Abbas, S. Palanivel

Abstract- Undersized satellites are bringing a critical part in spaceship missions on account of their cheap, minute in size, less weight. All the more no of little satellites are flying together can resolve complex missions, e.g., Data trade, high exactness in route. A raising number of satellites activity on lower earth circle for complex missions abuse the SDR for correspondence in light of its consistency and flexibility. This paper shows a total programming characterized radio (SDR) model for entomb satellite interchanges (ISCs) and recreation on a Xilinx ISE programming utilizing verilog HDL. The proposed SDR baseband segment for transmitter has an a lesser measure of intensity use, separately, which is proper for low power little satellite frameworks. Programming Defined Radio (SDR) has been one of the new methods which lessens the equipment multifaceted nature and furthermore change the route for conventional remote correspondence frameworks work. Planning a multi-tweak plans framework in term of FPGA makes it adaptable and reusable. This task introduces the plan of baseband handling segment of Software Defined Radio utilizing QPSK, BPSK and encoding plan utilizing Hamming code.

Index Terms-Software defined radio (SDR), Programmable Gate array (FPGA), Low Density Parity Check (LDPC) code, Inter Satellite Communication (ISC)

#### INTRODUCTION

The advancement in data innovation and the rising essential of Very Large Scale Integration concerns have result in a fast advance of various decrease calculations techniques. Low power utilization and littler space region unit some of the essential crucial criteria for the DSP frameworks and superior systems.DSP frameworks have less insusceptible to the module resiliences and ecological changes and the dynamic scope of the framework can be improved by gliding point number juggling. Programming Defined Radio is cost productive and effectively changed what can be utilized in every single radio standard. Programming radio is a term instituted to demonstrate the move from advanced radio to multiband multimode programming characterized radios. The SDR is a radio correspondence framework, which gives programming control to an assortment of regulation strategy, sifting, wideband or narrowband tasks, spread range procedures and waveform prerequisites and so on.

Revised Manuscript Received on December 30, 2019.

\* Correspondence Author

G.Vishnuvardhan Rao, Department of Electronics and Communication Engineering, Vel Tech Multi Tech Dr.Rangarajan Dr.Sakunthala Engineering College, Chennai, India

Mohammed Abbas, Department of Electronics Communication Engineering, Vel Tech Multi Tech Dr.Rangarajan Dr.Sakunthala Engineering College, Chennai, India

S.Palanivel, Department of Electronics and Communication Engineering, Vel Tech Multi Tech Dr.Rangarajan Dr.Sakunthala Engineering College, Chennai, India

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/)

The utilization of FPGA makes SDR as adaptable and reconfigurable with less calculation and less power expending.

#### A. ProblemIdentification

Most radios are hardware defined with little software control. Previously, radio technologies were developed with static architecture. They are fixed in function for mostly consumer items for broadcast reception. It can be easily replaced. Digital radio systems substituted Analog radio systems for various efficient levels such as domestic and commercial spaces. Since existing analog circuits are limited cross functionality and distortion in the signal can be resolved through physical intervention. Thus, it cannot be employed for all analog circuits (i.e.) multiwaveform standards. On the other hand, low cost comparatively efficient solution multimode, multi-band and/or multi-functional wireless devices that can be enhanced using software upgrades in communication systems with the help of software defined radio technology. Problems identified- High dynamic power dissipation, Low bit rate.

#### B. Proposed System

Software defined radio empower us to manufacture reconfigurable and interoperable radios that can be overhauled for future advances. Structuring a multiadjustment plans framework in term of FPGA makes it adaptable and reusable. The proposed structure is baseband preparing unit of Software Defined Radio utilizing twofold stage move keying and quadrature stage move keying tweak procedure and encoding plan utilizing hamming code. The primary favourable circumstances of this framework are its uses less power, Low zone, straightforward and proficient.

#### II. SDRTRANSMITTER AND RECEIVER

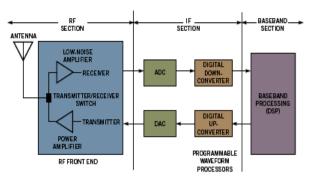

The assorted variety of tweak procedures are Capable of covering generous recurrence range and executing programming. The significant inheritance frameworks necessities are meet by wide-band or limited band activity, interchanges security Functions. Framework programming must be talented of applying new or substitute modules for extra usefulness or bug fixes without supplanting total arrangement of programming. The modules present in the SDR engineering are independent radio wire framework, broadband separating, speaker, down converters, A/Dchange, converters, D/A transformation

Fig.1. SDR architecture of transmitterand receiver system model

## III. DESIGN STRATEGIES AND RELATED ALGORITHMS

#### A. Hamming Code Encoder

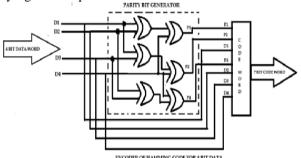

Hamming code is useful for every discovery and revision of blunder blessing inside the got data. This code utilizes numerous equality bits and that we have to put these equality bits inside the places of forces of two. The least estimation of 'k' for which the accompanying connection is right (legitimate) is only the necessary number of equality bits. $2k \ge n + k + 12k \ge n + k + 1$  Where, 'n'the assortment of bits inside the PC code (information)'k' is the measure of equality bits. Accordingly, the measure of bits inside the playing code is proficient n + k.

Fig.3.Hamming Code Encoder

### **B.** Decoding Strategies

In the decoder circuit, code word is applied as info. At that point check bits square measure created by the checker bit generator to discover the equality bits. These check bits finds the mistake inside the code word by recommends that of decoder circuit.

The yield of the decoder allows a demultiplexer that square measure associated with the information code words. On the off chance that no blunder happens, at that point the select line of demultiplexer streams the info structure line I0 and the I1 is set to rationale '1' So from the rationale OR door we will get the data. Presently on the off chance that a mistake happens, at that point the select line of the demultiplexer streams the code word from line I1 and I0 is set to rationale '0'. In this manner transforming thebits, the mistake bit is remedied and along these lines we can get the blunder free information.

#### C. Modulation Technique

This area depicts about the two regulation strategies utilized. BPSK-The adjustment of BPSK is finished utilizing an equalization modulator, which increases the two sign applied at the information. For a zero double information, the area are 0° and for a high information, the segment inversion is of 180°. The yield sine wave of the modulator will be yield wave of the modulator are the immediate info bearer or the reversed (180° segment moved) input transporter, which is an element of the information signal. QPSK-This is the area move scratching procedure during which the undulation bearer takes four segment inversions like 0°, 90°, 180°, and 270°. If this sort of strategies are

# like 0°, 90°, 180°, and 270°. If this sort of strategies are additionally broadened, PSK should be possible by eight or sixteen qualities moreover, contingent on the necessity.

#### D. Hardware Resources

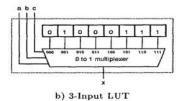

Fundamentally, the LUT complex calculations will be calculated well in advance and its result will be stored, whenever application need it will retrieve the data back. By maintaining the results in the LUT, when the application requires the values, instead of having to do the calculations, it can just refer to the LUT it; avoiding the calculations. LUT are widely used in complex applications speech and image processing, device modeling, because they are considerably decreasing the processing time. With regards to combinatory rationale, it is reality table.

The way FPGAs commonly execute combinatorial rationale is with LUTs, and when the FPGA gets designed, it just fills in the table yield esteems, which are known as the "LUT-Mask", and is physically made out of SRAM bits. A two input LUT (lookup table) is can be represented generically like this:

Fig. 4 Look-Up-Table

For a two-information AND door, The LUT is really actualized utilizing a blend of the SRAM bits and a Here the bits over the best 0 1 0 1 11 one speaks to the yield of the truth table for this LUT. The three contributions to the MUX on the left a, b, and c select the fitting yield esteem.

For a two-information AND entryway, The LUT is really actualized utilizing a plan of the SRAM bits and a Here the bits over the main 0 1 0 1 11 one speaks to the yield of the truth table for this LUT. The three contributions to the MUX on the left a, b, and c select the proper yield esteem.

Fig.5.Mux LUT

#### IV. IMPLEMENTATION AND RESULTS

The proposed SDR baseband handling unit for transmitter devours an intensity of about 0.014 W, which is appropriate for power-constrained little satellite frameworks Algorithms and parameters of each square are enhanced targeting lessening equipment asset use

#### A.Test Platform

This section tells about how to integrate and run the communication system model. Here, the FPGA is connected with the host computer through the Ethernet cable.

Fig.6.Fpga Platform Used In This Model

| Device Utilization Summary             |      |           |             |        |   |

|----------------------------------------|------|-----------|-------------|--------|---|

| Slice Logic Utilization                | Used | Available | Utilization | Note(s | ) |

| Number of Slice Registers              | 42   | 11,440    | 1%          |        |   |

| Number used as Flip Flops              | 42   |           |             |        |   |

| Number used as Latches                 | 0    |           |             |        |   |

| Number used as Latch-thrus             | 0    |           |             |        |   |

| Number used as AND/OR logics           | 0    |           |             |        |   |

| Number of Slice LUTs                   | 44   | 5,720     | 1%          |        |   |

| Number used as logic                   | 43   | 5,720     | 1%          |        |   |

| Number using O6 output only            | 19   |           |             |        |   |

| Number using O5 output only            | 7    |           |             |        |   |

| Number using O5 and O6                 | 17   |           |             |        |   |

| Number used as ROM                     | 0    |           |             |        |   |

| Number used as Memory                  | 0    | 1,440     | 0%          |        |   |

| Number used exclusively as route-thrus | 1    |           |             |        |   |

| Number with same-slice register load   | 0    |           |             |        |   |

| Number with same-slice carry load      | 1    |           |             |        |   |

| Number with other load                 | 0    |           |             |        |   |

| Number of occupied Slices              | 17   | 1,430     | 1%          |        |   |

| Number of MUXCYs used                  | 16   | 2,860     | 1%          |        |   |

| Number of LUT Flip Flop pairs used     | 50   |           |             |        |   |

| Number with an unused Flip Flop        | 20   | 50        | 40%         |        |   |

| Number with an unused LUT              | 6    | 50        | 12%         |        |   |

Table 1.Fpga Hardware Resources Utilization For The Transmitter And Receiver

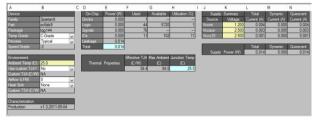

#### A.Power Analysis

The below mentioned table illustrates the power consumed by the prototype. A FPGA power estimation shows that the baseband section of transmitter consumed about 0.014W

Table 2.Power Analysis Of Transmitted Signal

#### V. CONCLUSION

The proposed baseband area of transmitter for SDR is completely adaptable, dependable and appropriate for low power satellites system.SDR configuration utilizing an ongoing headway in FPGAs, called Partial Reconfiguration (PR).PR shifts sure segment of FPGA, while the rest continues working. It furthermore diminishes the whole equipment use and in this manner the office. The diverse gathering strategy partner distinctive sign procedure application from an outside memory unit might be stacked into FPGA PR modules though the contrary segments of FPGA doing a consistent information processing. Usage of SDR diminishes thehardware use. For future upgrade, both the transmitter and recipient are executed on a FPGA utilizing SDR module utilizing other higher request tweak strategies with an effective showing over the air transmission.

#### REFERENCES

- "Implementing PSK MODEMs on FPGA using Partial Reconfiguration" Archana M. Lalge, Anjali Srivastava, Sheetal U.Bhandari ,P.C.C.O.E, Savitribai Phule Pune University ,International Conference on Computing Communication Control and Automation 2015.

- KavyashreeD, Umeshraddy "SDR IMPLEMENTATION OF QPSK MODEM WITH AWGN", International Journal of Scientific & Engineering Research Volume 8, Issue 5, May-2017.

- "Power consumption reduction in a SDR based wireless communication system using partial reconfigurable FPGA", International Journal of VLSI design & Communication Systems (VLSICS) ,, Neenu Joseph, Dr. P Nirmal Kumar Vol.3, No.2, April 2012.

- "Design and Hardware Implementation of Reconfigurable Nano Satellite Communication System Using FPGA Based SDR for FM/FSK Demodulation and BPSK Modulation" Dr.Sheeba Rani J , Vidhya P, Nivin R , International conference on communication and networks 2016