# Performance Examination of SEPIC Based Hybrid Cascaded Single-Phase Multilevel Inverter

## Arunprasath R, Vijayakumar D, Rathinakumar M, Meikandasivam S, Kirubakaran A

Abstract: In the present scenario, reduced part count(RPC) multilevel inverters are become popular compared to traditional multilevel inverters(MLIs). This is mainly due to reduced size and cost and alleviates the issues of more passive components, flying capacitor voltage balancing issues and the requirement of complex switching schemes. Also, the RPC is getting attraction for various industrial and transportation applications. Therefore, in this paper, a novel 17 level inverter is proposed by cascading MLIs with the reduced part count. The complete operation, switching schemes and output are presented to evolve the performance under steady-state conditions using MATLAB software.

Keywords : Multilevel inverter, DC-DC boost converter, sinusoidal pulse width modulation (SPWM);

#### I. INTRODUCTION

Renewable power generation is getting popularity for distributed generations due to their benefits of reduced system installation cost and environmentally friendly nature. However, interfacing renewable energy sources demand suitable power conditioner. Single state DC/AC converter becomes popular and higher efficiency[1-5]. However, regulation in supply is critical, so these leads to develop an intermediate boost converter to enhance the voltage gain. However, increasing voltage gain can be achieved at high duty cycle leads to more looses which degrade the efficiency of the system. Recently, MLIs are promising for power generation using renewable applications with the reduced part count. Whereas the use of conventional MLIs demands more clamping diodes, flying capacitor, voltage balancing issues and more complex in control for higher level[5-9]. In this context, RPC-MLIs are getting popularity to enhance the output levels with a better quality of output voltage waveforms. The various RPC-MLIs are described in the

Revised Manuscript Received on December 30, 2019.

\* Correspondence Author

\*Arunprasath R, research scholar, SCSVMV University, Kanchipuram, India. Email: prasatheee2003@gmail.com

Vijayakumar D, chool of Electrical Engineering, VIT University, Vellore, India.

Meikandasivam S, School of Electrical Engineering, VIT University, Vellore, India. Email: vijayakumar.d@vit.ac.in, meikandasivam.s@vit.ac.in Rathinakumar M, Department of Electrical Engineering, SCSVMV

University, Kanchipuram, India. Email: rathinamari@rediffmail.com Kimbakanan A. Donattmant of Electrical Engineering, NIT Waranad

**Kirubakaran A**, Department of Electrical Engineering, NIT Warangal, India, <u>kiruba81@nitw.ac.in</u>

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC BY-NC-ND license (<u>http://creativecommons.org/licenses/by-nc-nd/4.0/</u>)

literature [10] is for seven-level operations only. Increasing level with lower switches will enhance the performance of the system. Therefore, in this paper performance evaluation of a novel cascaded multilevel inverter is considered for the study using MATLAB software. The proposed model is capable of 17 level generation with the reduced part count. a front end boost converter is also used to balance the dc-link and the simulation results are given for steady-state conditions.

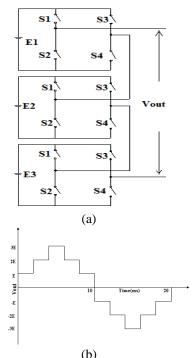

#### II. CASCADED H-BRIDGE MULTILEVEL INVERTER

Cascaded H-Bridge (CHB) is the most popular one among conventional MLIs. Whereas Diode-clamped and Flying capacitor MLIs have the problem for increase level. CHB is the best model for increased level of generations. It is capable to generate 2N+1 level for cascading of N modules. However, it demands identical dc sources for each H-Bridge circuits and more semiconductor devices for more output levels. Fig.1 depicts the seven-level CHB and its expected output voltage waveform.

Retrieval Number: B2288129219/2019©BEIESP DOI: 10.35940/ijeat.B2288.129219 Journal Website: <u>www.ijeat.org</u>

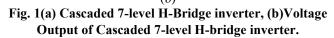

## A. Novel H-Bridge Inverter

A novel H-bridge inverter is developed by connecting a bidirectional semiconductor device with diodes in between the H-bridge and the DC input. The single unit is capable to produce 5 level AC output. The foremost advantage of the novel H-bridge inverter compared to a conventional CHB MLIs is the reduction of the number of semiconductor devices. For a CHB multilevel inverter to generate a 5 level AC output, 8 switches are required. This results in increased efficiency and reliability of the system and reduced in device count.

Fig. 2. Novel H-Bride inverter

Table 1: Switching Pattern of Novel H-bridge

| Output<br>voltage | K   | A1  | A2  | B1  | B2  |

|-------------------|-----|-----|-----|-----|-----|

| 2E                | off | on  | off | off | on  |

| E                 | on  | off | off | off | on  |

| 0                 | off | off | on  | off | on  |

| -E                | on  | off | off | on  | off |

| -2E               | off | off | on  | on  | off |

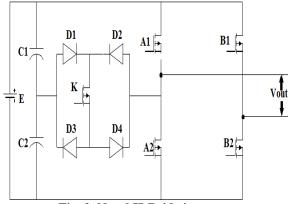

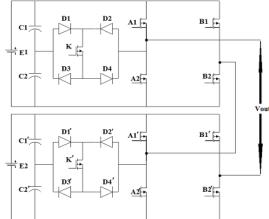

## **B.** Cascaded Novel H-Bridge

Here two novel H-bridge circuits are wired to produce various output levels such as 9, 13, and 17 by varying the magnitude of the input DC sources with reduced device count is the foremost advantage of this configuration. The different combinations for the output level generations are depicted in tables 1-5.

Fig.3 Cascaded Novel H-Bridge-Bridge inverter

Table 2: Voltage ratio of H-Bridge and Voltage levels can

| be obtained |    |                |  |

|-------------|----|----------------|--|

| E1          | E2 | Voltage Output |  |

Е 0 Е 2E 0 2E Е 2E 3E 4E 2E 2E Е 4E 5E 2E 4E 6E -2E -4E -6E -4E -E -5E -2E -2E -4E -E -2E -3E -2E -2E 0 -E 0 0 0 0 0

Table 3: Voltage in each level of both novel H-bridge for 9 level inverter.

| E1 | E2 | LEVELS |  |  |  |

|----|----|--------|--|--|--|

| Е  | Е  | 9      |  |  |  |

| Е  | 2E | 13     |  |  |  |

| E  | 3E | 17     |  |  |  |

| E  | 4E | 21     |  |  |  |

| E  | 5E | 25     |  |  |  |

Table 4: Voltage in each level of both novel H-bridge for **13** level inverter

| 13 level inverter. |     |                |  |  |  |

|--------------------|-----|----------------|--|--|--|

| E1                 | E2  | Voltage Output |  |  |  |

| Е                  | 0   | Е              |  |  |  |

| 2E                 | 0   | 2E             |  |  |  |

| 0                  | 3E  | 3E             |  |  |  |

| Е                  | 3E  | 4E             |  |  |  |

| 2E                 | 3E  | 5E             |  |  |  |

| 0                  | 6E  | 6E             |  |  |  |

| Е                  | 6E  | 7E             |  |  |  |

| 2E                 | 6E  | 8E             |  |  |  |

| -2E                | -6E | -8E            |  |  |  |

| -E                 | -6E | -7E            |  |  |  |

| 0                  | -6E | -6E            |  |  |  |

| -2E                | -3E | -5E            |  |  |  |

| -E                 | -3E | -4E            |  |  |  |

| 0                  | -3E | -3E            |  |  |  |

| -2E                | 0   | -2E            |  |  |  |

| -Е                 | 0   | -E             |  |  |  |

| 0                  | 0   | 0              |  |  |  |

Table 5: Voltage in each level of both novel H-bridge for 17 level inverter

| E1         | E2  | Voltage Output |  |  |  |

|------------|-----|----------------|--|--|--|

| Е          | 0   | Е              |  |  |  |

| Е          | E   | 2E             |  |  |  |

| Е          | 2E  | 3E             |  |  |  |

| 2E         | 2E  | 4E             |  |  |  |

| -2E        | -2E | -4E            |  |  |  |

| <b>-</b> E | -2E | -3E            |  |  |  |

| <b>-</b> E | -E  | -2E            |  |  |  |

| <b>-</b> E | 0   | -Е             |  |  |  |

| 0          | 0   | 0              |  |  |  |

## C. Sepic Converter

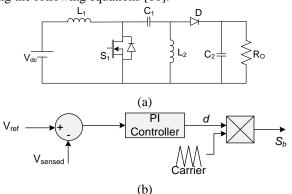

In this study, the sepic converter is taken as front end converter to regulate the desired primary voltage and simple control scheme is built using PI converter are shown in Fig. 4 (a) and (b). Generally, it consists of a simple inductor and capacitors and one semiconductor device. Sepic is capable to boost the desired voltage from the input by sensing the voltage. The selection of design parameters is computed using the following equations [10].

Fig. 4 (a) Sepic converter, (b) Closed loop scheme

$$\frac{V_o}{V_{in}} = \frac{D}{(1-D)} \tag{1}$$

$$L = \frac{DV_{in}}{f_s \Delta I_L} \tag{2}$$

$$C = \frac{DV_{dc}}{Rf_s \Delta V_C} \tag{3}$$

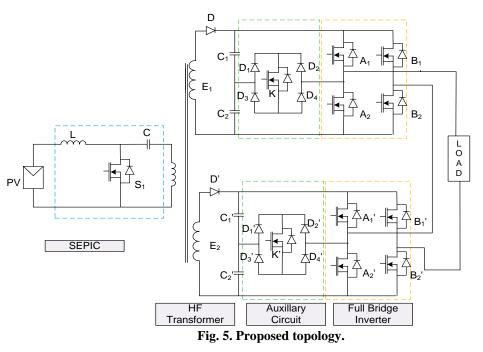

# **D.** Proposed Topology

Fig. 5 shows the proposed topology using a sepic converter as front end converter with two cascaded five-level t-type inverters with the auxiliary circuit. The proposed circuit is capable for maximum 25 level output by proper selection of the input voltages using a multi-winding transformer with proper turns ratio selection. The single unit of five-level t-type inverter can produce 2E to -2E level with intermediate steps of E, 0 and -E voltage levels. Whereas the cascaded circuit is capable to produce 25 levels for a different combination of input voltages as discussed above.

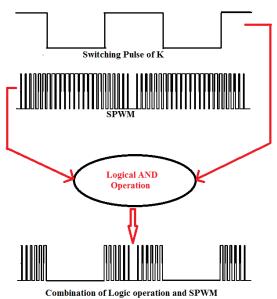

## E. PWM Technique

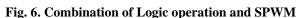

A simple sinusoidal pulse width modulation scheme( PWM) is used for the production of the various signal of the semiconductor devices. Sine PWM is simplest among the other PWM of State vector PWM, and Selective Harmonic Elimination PWM technique. It requires n-1 carrier signals to produce n-level output waveforms. To limit the number of carriers, a new PWM technique using carriers have been presented in this paper. This implemented jointly with a single carrier with digital encoding methods.

Logical operation is implemented using various gates circuit to produce the pulses for all the semiconductor devices. For example, one t-type converter takes 5 level operation with the voltage levels of 2E, E,-E, -2E for both the units 8 samples of voltage can be produced. so three signals of 50Hz, 100Hz, and 200Hz are used such as A, B, and C is as follows. Here A, B and C are the various inputs of the encoder and P1 to P8 are the output of the encoder.

BUDEACION BUDEAC

Retrieval Number: B2288129219 /2019©BEIESP DOI: 10.35940/ijeat.B2288.129219 Journal Website: <u>www.ijeat.org</u>

| Α  | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

|----|---|---|---|---|---|---|---|---|

| В  | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| С  | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| P1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| P2 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| P3 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| P4 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| P5 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| P6 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| P7 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| P8 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Table 6: 3\*8 Encoder characteristic table

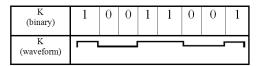

Let us take K switch of 5 level inverter. The switching sequence follows

If we perform logical OR operation of P1, P4, P5, P8 (refer table), we can get above Switching sequence for switch K. Likewise switching sequence for A1, A2, B1 and B2 are generated.

From Fig. 6 it can be observed that after the performance of logical operations, an AND operation is performed between the obtained switching sequence and the sinusoidal pulse width modulated signals to obtain the pulse width modulated signal for the switch K. similarly PWM signals for switches A1, A2, B1 and B2 can be attained.

## **III. SIMULATION RESULTS**

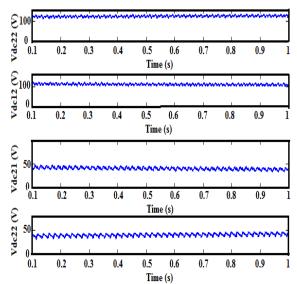

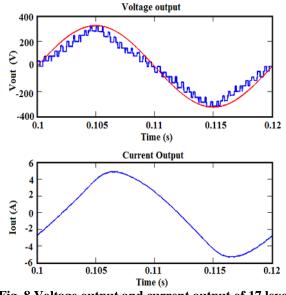

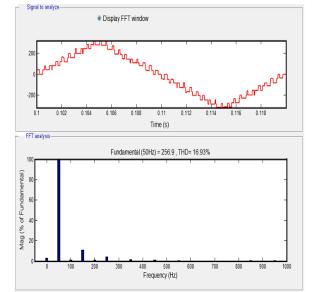

In this study, the performance of the proposed sepic based t-type inverter is verified in MATLAB software for a resistive load of 1 kVA. The various parameter selected for the study is given in Table 7. Fig. 7 depicts the dc-link voltage of the t-type converter is well regulated by the sepic converter by adjusting the duty cycle separately, as per the desired value. Fig. 8 depicts the measured 17level output voltage waveform and their corresponding load current. To

Retrieval Number: B2288129219/2019©BEIESP DOI: 10.35940/ijeat.B2288.129219 Journal Website: <u>www.ijeat.org</u> calculate the total harmonic distortion, FFT analysis is carried out and the measured THD of the simulated 17 level output voltage waveform is around 16.93% which is very lower compared to the conventional 3-level inverter. It is noticed that the results show a better performance. Further, the study shows that it can be effectively useful for PV applications.

| Table 7: Para | ameters for | 17 level | inverter |

|---------------|-------------|----------|----------|

|---------------|-------------|----------|----------|

| Parameters      | Specifications |

|-----------------|----------------|

| $V_{dc}$        | 40V            |

| F               | 2.5kHz         |

| M1, M2          | 0.83, 0.5      |

| C1              | 100 µf         |

| C1, C2, C1',C2' | 1000µf         |

| L, L'           | 500µH          |

| Load            | 1KVA           |

Fig. 7.Voltage output across dc-link of t-type converter

Fig. 8.Voltage output and current output of 17 level inverter

Fig. 9. FFT and THD analysis of 17 level inverter output voltage.

### **IV. CONCLUSION**

In this study, a new structure of sepic based cascaded t-type multilevel inverter is presented. Sine PWM control with encoder logic operation is implemented to realize the 17 level output voltage waveforms in the MATLAB environment. The sepic converter effectively regulates the voltage and also performance of the converter under steady-state is presented. The proposed circuit is modular one and can be extended for further levels by cascading the H-bridge circuits.

#### REFERENCES

- 1. Xing Tao Sun, "Hybrid Control Strategy for a Novel Hybrid Multilevel Inverter", IEEE conference on E-product, E-Service and E-Environment, pp. 1-4, 2010.

- 2. Yi Wang, Heming Li, Xinchun Shi, and Boqiang Xu "A novel carrier based PWM strategy for hybrid multilevel inverters", IEEE 35th Annual Power Electronics Specialists Conference, pp.4233-4237, 2004.

- Jammy Ramesh Rahul, A. Kirubakaran, and D. Vijyakumar "A New Multilevel DC-DC Boost Converter for Fuel Cell Based Power System". IEEE Students' Conference on Electrical, Electronics and Computer Science, pp.1-5, 2012.

- 4. Lai YS, and Shyu FS. "Topology for hybrid multilevel inverter", IEE Proceedings-Electric Power Applications, vol.149, pp.449-458, 2002.

- P. Thounthong, S. Sikkabut, P. Sethakul, and B. Davat, "Model 5. Based-Control of Three-Level Boost Converter for Fuel Cell Applications,"10th International Conference on Environment and Electrical Engineering, pp. 1-4, 2011..

- Palanivel, P. and Dash, S.S. "A FPGA based Variable switching 6. frequency Multi-carrier Pulse width modulation for Three phase Multilevel Inverter", control, Automation, Communication and Energy Conservation, pp. 1 - 4, 2009.

- 7 J. Rodriguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," IEEE Trans. on Industrial Electronics, vol. 49, No. 5, pp. 724-738, 2002. L.M. Tolber, T.G. Habetler, "Noval multilevel inverter carrier based

- 8. PWM methods", IEEE IAS Annual meeting, pp. 1424-1431. 1998.

- 9. Eenstra, M.; Rufer, A. Hegner, "Control of a hybrid asymmetric multilevel inverter for competitive medium-voltage industrial drives", Industry Applications, IEEE Transactions on Digital Object Identifier, 41(2) pp. 655-664, 2005.

- 10. R. Arunprasath, D. Vijayakumar, M. Rathinakumar, S. Meikandasivam, and A. Kirubakaran, "Performance Evaluation of SEPIC Based Single-Phase Seven-Level Inverter for Renewable Applications", International Journal Renewable Energy Research, pp.1-8, 2019.

# **AUTHOR PROFILE**

Mr. R. Arun Prasath, was born in Kanchipuram, Tamil Nadu, in 1979. He received the B.E. degree in Electrical Electronic Engineering from Madras University, Chennai, India, in 2003, the M.E. degree in Power Electronics and Industrial Drives from Sathyabama University, Chennai, Tamil Nadu, in 2007, he has been with the Department of Electrical Engineering, Sri Krishna College of Engineering where he is currently a Associate Professor. His

research interests include modeling and control of dc/dc converters, design of Renewable Energy-supplied inverters for grid connection.

Dr. D. Vijayakumar, was born in Kanchipuram, Tamil Nadu, in 1980. He received the B.E. degree in Electrical Electronic Engineering from Madras University, Chennai, India, in 2002, the M.E. degree in Power System from SCSVMV, Enathur, Tamil Nadu, in 2005, and the Ph.D. degree in Electrical Engineering from MANIT, Bhopal, MP, in 2010. From July 2002 to June 2003, he was a Lecturer with the Department of Electrical and Electronic Engineering, Pallavan Polytechnic

College, Iyengarkulam, Kanchipuram. He was an Assistant Professor with the Department of Electrical and Electronics Engineering, Pallavan College of Engineering, Thimmasamuthiram, Kanchipuram, from January 2006 to June 2006. Since 2009, he has been with the School of Electrical Engineering (SELECT), VIT University, Vellore, where he is currently a Professor. His research interests include modeling and control of dc/dc converters, design of Renewable Energy-supplied inverters for grid connection, and Power Systems Protection and Control.

M. Rathinakumar, currently working as Professor and Head of the Department of Electrical Engineering, SCSVMV University, Kanchipuram. He has published more than 40 peer reviewed journals. His area of interest lies in Power System Security, Voltage Stability, Reactive Power Control

S. Meikandasivam received the Bachelor's degree in electrical and electronics engineering in 2002, the Master's degree in power systems in 2005, and the Ph.D. degree from the Maulana Azad National Institute of Technology, Bhopal, India, in 2010. Since 2010, he has been an Associate Professor with the School of Electrical Engineering, Vellore Institute of Technology, Vellore.

Kirubakaran Annamalai (M'01-SM'18) received his B.E. degree in Electrical and Electronics Engineering from Madras University in 2002, M.E. degree in Power System from Annamalai University in 2004 and PhD degree in Electrical Engineering from Maulana Azad National Institute of Technology, Bhopal in 2011. He was a Lecturer in Thirumalai Engineering College affiliated to Anna University during 2004-2007 and holds the position

of Assistant Professor Senior Grate and Associate Professor at the School of Electrical Engineering, VIT University, Vellore from 2010-2012. He is currently working as an Assistant Professor in Department of Electrical Engineering, National Institute of Technology Warangal, Warangal, India. His fields of interest are power converter topologies, advanced digital control for power electronics and renewable energy systems.

Retrieval Number: B2288129219 /2019©BEIESP DOI: 10.35940/ijeat.B2288.129219 Journal Website: <u>www.ijeat.org</u>

3648