# 11-level Multilevel Inverter for Medium Voltage High Power ID and FD Fan Drives in Power Plant

#### B. V. Pranav, Y. Mohana, Mule Sai Krishna Reddy, K.V. Siva Reddy, S. Ravi Teja

Abstract: Multi-level inverter technology has emerged recently as a very important alternative in the area of medium-voltage high-power energy control such as ID and FD fans which runs with the help of these megawatt power drives and renewable energy integration to grid such as solar energy integration which requires pure sinusoidal voltage with less than five percent THD to synchronize to grid. For the requirement of large voltage sources(DC) in number, reduced electromagnetic interference, utilization of power electronic devices having less voltage blocking capability, less percentage of total harmonic distortion in output voltage, reduced stress on insulation they are mostly used. Various topologies are used for multilevel inverters. Among them the most commonly used is cascaded H-bridge (multi-cell). A 3-phase 11-level reduced H-bridge topology is proposed and is controlled by level shift carrier PWM in this paper. The considered topology and controlled algorithm is implemented in MATLAB/SIMULINK. The simulation results show a reduction of THD to a greater extent which will be useful in renewable areas and mega watt power drives.

Keywords: H- Bridge, Multilevel, Inverter, level shift carrier PWM, THD, ID and FD fan.

#### I. INTRODUCTION

The photovoltaic process has acquired exceptional significance in these modern days in the development of pollution-free electricity. Using solar stages the photovoltaic device transforms the sun's light energy into electrical energy. The electricity generated is in the form of direct current (DC). A photovoltaic network connected to the grid often includes a two-level inverter to transform DC-to-AC.

Revised Manuscript Received on December 30, 2019.

\* Correspondence Author

**B. V. Pranav**, B.Tech, Department of Electrical and Electronics Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India.

Y. Mohana, B.Tech, Department of Electrical and Electronics Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India.

Mule Sai Krishna Reddy, Asst.Professor, Department of Electrical and Electronics Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India.

**K. V. Siva Reddy,** Asst. Professor, Department of Electrical and Electronics Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India.

**S. Ravi Teja**, Asst. Professor, Department of Electrical and Electronics Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC BY-NC-ND license (<u>http://creativecommons.org/licenses/by-nc-nd/4.0/</u>)

Yet it is unable to generate a waveform similar to sinusoidal, and thus contributes a high level of harmonic material in current and voltages, rendering the inverter bulky in length [1-4]. In the high-power sector, it is not appropriate with conversion purposes, thus, two level inverters have been substituted by multilevel inverters ideal for high-power conversion. The increased level decreases the harmonic content and brings the waveform of output voltage similar to the sinusoidal [5]. The multilevel inverter (MLI) has thus attracted tremendous interest in the high-voltage sector. There are traditional multilevel inverters with three forms, diode-clamped MLI, MLI moving capacitor and cascaded H-bridge MLI. For diode-clamped MLI, the bulk of diodes are used and the number of diodes decreases with the level increment. In diode clamped MLI has been discussed with lesser number of diodes. The count of capacitor is dominant in flying capacitor MLI, and the number of capacitor decreases with a rise in MLI level, it is addressed the modified flying capacitor. In cascaded MLI, as the level of the cascade increases, the quantity of switches and sources will certainly increase [6-8]. To obtain 11-level output five H-bridge cells are required, but the same 11-level output can be obtained from three H-bridge cells with unequal voltage rating of dc sources. For example for 11-level with three H-bridge cell configuration  $V_{dc}$ ,  $2V_{dc}$  and  $3V_{dc}$  level sources are required. Although reduction in no. of H- bridge cells is achieved, but this type of configuration is compromising modularity, equal voltage sharing capability, simplicity in selection of switches [9-10]. Hence the regular configuration with five H-bridge cells of equal source voltage rating is considered with a source voltage of  $V_{dc}$ . In the power plants ID and FD fans play a major role and they work under megawatt power drives. If trouble arises with a single draft fan the entire plant unit generation would be stopped. In this paper the proposed configuration is a modular multilevel inverter which would drive the ID and FD fans. Even if a single H-Bridge is failed it acts as a low level inverter and power generation would not be interrupted energy wastage is will be monitored [11-12]. Section-II discusses the proposed converter switching logic and operation. Section-III dedicated to simulation results and analysis and finally comparison with other shifted PWM schemes is done and represented in Section-IV.

#### II. PROPOSED 11-LEVEL INVERTER

#### A. Proposed Topology Operating Principle

The proposed topology is developed by considering the conventional H-bridge. The stage of proposed topology consists of five H-Bridges in

each phase.

Retrieval Number: B3433129219/2019©BEIESP DOI: 10.35940/ijeat.B3433.129219 Journal Website: <u>www.ijeat.org</u> Published By: Blue Eyes Intelligence Engineering & Sciences Publication

#### 11-level Multilevel Inverter for Medium Voltage High Power ID and FD Fan Drives in Power Plant

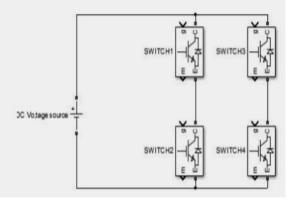

The switching table of proposed topology is shown in Fig 2.1.In the figure only a single bridge in a phase is represented. Five H-Bridges are connected in each phase. The switching table for obtaining the 11-level is hereby shown under in table 2.1.

The switches S1and S3are complimentary to the switches S2 and S4. If switch S1 is on it gives an output voltage of  $V_{dc}$  in that bridge. If switch S3 is on it gives an output voltage of  $-V_{dc}$ .

| Voltage Levels | B1-S1 | B1-S3 | B2-S1 | B2-S3 | B3-S1 | B3-S3 | B4-S1 | B4-S3 | B5-S1 | B5-S3 |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0              | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Vdc            | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 2Vdc           | 1     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 3Vdc           | 1     | 0     | 1     | 0     | 1     | 0     | 0     | 0     | 0     | 0     |

| 4Vdc           | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 0     | 0     |

| 5Vdc           | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     |

| 4Vdc           | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 0     | 0     |

| 3Vdc           | 1     | 0     | 1     | 0     | 1     | 0     | 0     | 0     | 0     | 0     |

| 2Vdc           | 1     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Vdc            | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0              | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| -Vdc           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

| -2Vdc          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     |

| -3Vdc          | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     | 0     | 1     |

| -4Vdc          | 0     | 0     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     |

| -5Vdc          | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     |

| -4Vdc          | 0     | 0     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     |

| -3Vdc          | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     | 0     | 1     |

| -2Vdc          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     |

| -Vdc           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

Table 2.1: Switching table for designed inverter

Considering a single phase the levels of the output voltage are as follows:

#### B. Switching Algorithm

- 1. First level (1L): When all the switches in all the Five bridges are off it gives an output voltage zero.

- 2. Second level (2L): When the switch S1 in the bridge -1 is on and the rest other switches are off then it gives an output voltage of  $V_{dc}$ .

- 3. Third level (3L): When the switch S1 in the bridge -1, switch S1 in the bridge 2 are on and the rest other switches are off then it gives an output voltage of  $2V_{dc}$ .

- 4. Fourth level (4L): When the switch S1 in the bridge -1, switch S1 in the bridge 2, switch S1 in the bridge 3 are on and the rest other switches are off then it gives an output voltage of  $3V_{dc}$ .

- 5. Fifth level (5L): When the switch S1 in the bridge -1,switch S1 in the bridge 2,switch S1 in the bridge 3,switch S1 in the bridge 4 are on and the rest other switches are off then it gives an output voltage of  $4V_{dc}$ .

- 6. Sixth level (6L): When the switch S1 in the bridge -1,switch S1 in the bridge 2,switch S1 in the bridge 3,switch S1 in the bridge 4,switch S1 in the bridge five are on and the rest other switches are off then it gives an output voltage of  $5V_{dc}$ .

- 7. Seventh level (7L): When the switch S3 in the bridge -5 is on and the rest other switches are off then it gives an output voltage of  $-V_{dc}$ .

- 8. Eighth level (8L): When the switch S3 in the bridge -5, switch S3 in the bridge 4 are on and the rest other switches are off then it gives an output voltage of  $-2V_{dc}$ .

- 9. Ninth level (9L): When the switch S3 in the bridge -5,switch S3 in the bridge 4,switch S3 in the bridge 3,are on and the rest other switches are off then it gives an output voltage of  $-3V_{dc}$ .

- 10. Tenth level(10L): When the switch S3 in the bridge -5,switch S3 in the bridge 4,switch S3 in the bridge 3,switch S3 in the bridge 2 are on and the rest other switches are off then it gives an output voltage of  $-4V_{dc}$

- 11. Eleventh Level(11L): When the switch S3 in the bridge -5,switch S3 in the bridge 4,switch S3 in the bridge 3,switch S3 in the bridge 2, switch S3 in the bridge 1 are on and the rest other switches are off then it gives an output voltage of  $-5V_{dc}$ .

Fig: 2.1 H-Bridge

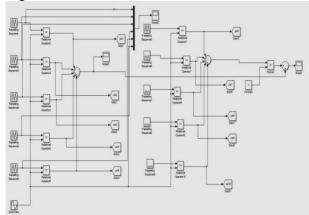

The proposed system has implemented the carrier based level shift PWM for 11-level cascaded H-Bridge MLI. In this topology if there are m levels m-1 carriers are to be generated. Initially first level carrier is generated depending on the carrier frequency and the number of carriers. Remaining carriers are generated by adding dc -offset to the first level carrier. All these carriers are bounded in the range of -1 to 1.These carriers are compared with ma value which depends on the amplitude of the reference wave (sinusoidal) having maximum value of 1.

Fig 2.2 PWM Generation Module

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

Retrieval Number: B3433129219/2019©BEIESP DOI: 10.35940/ijeat.B3433.129219 Journal Website: <u>www.ijeat.org</u>

The proposed configuration used level shift carrier PWM technique. For 11-level inverter one needs to have ten carrier signals. It is compared with sine wave and pulses are generated with respect to that and those are given to switches.

Fig 2.3 Comparison of reference with carrier

Level shift methods are based on the amplitude modulation (ma). To attain different levels by changing the value of ma. The levels are generated when their respective level carriers are compared with the reference wave (sinusoidal). The different types of level shift modulation are phase disposition PWM, Phase opposition disposition PWM, Alternative Phase opposition Disposition PWM.

#### **III. SIMULATION RESULTS**

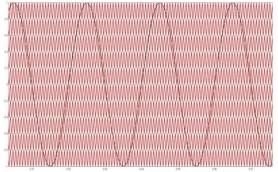

The proposed Multi-cell configuration is simulated and verified using MATLAB/SIMULINK. The obtained results are for ma=1 and with each H-bridge DC source voltage of 100Volts to obtain a maximum value of 500Volts approximately. The results were obtained under the consideration of specifications as shown in the below table 3.1

| S.No | Specification           | Rating    |

|------|-------------------------|-----------|

| 1    | H-Bridge Voltage        | 100 Volts |

| 2    | Induction machine       | 1000Watts |

|      | power rating            |           |

| 3    | Value of m <sub>a</sub> | 1         |

| 4    | Carrier Frequency       | 1.35kHz   |

| 5    | Nominal Voltage of the  | 415Volts  |

|      | induction machine       |           |

Table 3.1 -specifications of proposed topology

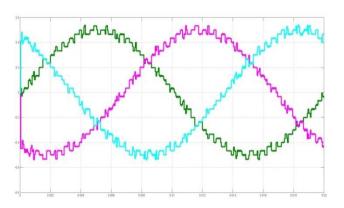

Fig 3.1-Output Voltage of 11-level cascaded inverter

The figure 3.1 represents the output voltage of the 3 phase 11-level cascaded H-bridge multilevel inverter .It can clearly observed the 11-levels in the output voltage which is almost sinusoidal. Filter requirement is also not there as the output voltage is almost sinusoidal which can be used for megawatt power drives.

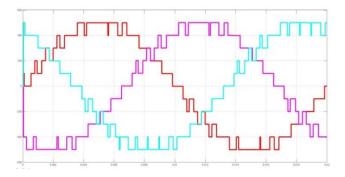

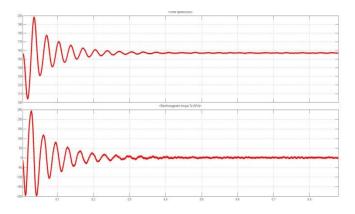

#### Fig 3.2-Output current waveform of 11-level cascaded inverter

The figure 3.2 shows the output current of the inverter. The current is almost sinusoidal having a slight ripple with a peak current value of 0.5Amps induction motor load.

Fig 3.3-Torque and Speed characteristics of induction motor drive

It can be clearly observed that smooth torque and speed characteristics. Torque ripple is even less when operated by the output of this multilevel inverter. The drive operation is very effective when operated under this modular inverter.

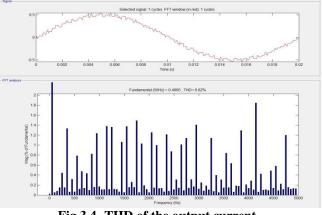

Fig 3.4- THD of the output current

#### IV. COMPARISION WITH OTHER TOPOLOGIES

It is observed that reduced THD while using phase disposition in level shift carrier PWM technique.

Published By:

& Sciences Publication

#### 11-level Multilevel Inverter for Medium Voltage High Power ID and FD Fan Drives in Power Plant

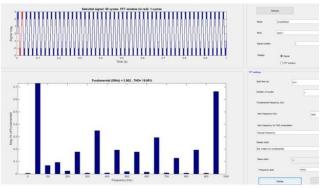

The resulted THD is comparatively less to that of phase opposition and alternative phase opposition disposition technique. The THD results of those are shown in the fig 4.1 and 4.2

Fig 4.1- THD of phase opposition technique

The figure 4.1 represents the the percentage of THD obtained for an 11-level inverter with phase opposition technique.

## The figure 4.1 represents the the percentage of THD obtained for an 11-level inverter with alternate phase opposition disposition technique.

### Fig 4.2- THD of alternate phase opposition and disposition technique

| Table 4.1- THD comparison | of different topologies |

|---------------------------|-------------------------|

|---------------------------|-------------------------|

| S.No | Topology                       | THD    |

|------|--------------------------------|--------|

| 1    | Proposed Topology              | 6.62%  |

| 2    | Phase opposition               | 17.99% |

| 3    | Alternate Phase opposition and | 18.00% |

|      | disposition                    |        |

The various THD values obtained for the different topologies are compared in the above table with the proposed topology THD. It is observed that proposed topology THD is comparitively less than that of the other existing ones.

#### V. CONCLUSION

To validate the topology the MATLAB/SIMULINK model is done, where carrier frequency  $f_c$  is take as 1.35 kHz, single level voltage  $V_{dc}$  is taken as 100 volts. The output is shown in figure above. Megawatt power drives are used to run FD and ID fans in thermal power plants. Megawatt power drives can be run only with the help of multilevel inverters. So, these inverters should run with greater efficiency and any mislead leads to the stoppage of power generation. Implementation of cascaded inverter will be very helpful in these areas with greater efficiency and reduced THD. In the implemented inverter even if there is any failure in one of the bridges it would act as a low level inverter because of its modular structure. Modularity plays a key role here. If this is used to run a drive its speed and torque characteristics settles well and it can be observed the ripple in the torque.

#### REFERENCES

- J. Rodriguez, S. Bernet, P. K. Steimer and I. E. Lizama, "A Survey on Neutral-Point-Clamped Inverters," in IEEE Transactions on Industrial Electronics, vol. 57, no. 7, pp. 2219-2230, July 2010.

- R. M. Tallam, Rajendra Naik and T. A. Nondahl, "A carrier-based PWM scheme for neutral-point voltage balancing in three-level inverters," Applied Power Electronics Conference and Exposition, 2004. APEC '04. Nineteenth Annual IEEE, 2004, pp. 1675-1681 Vol.3.

- J Rodriguez, J S. Lai, and F. Z Peng, "Multilevel Inverters A Survey of Topologies, Controls, and Applications," IEEE Trans. Ind Electron.,vol. 49, no. 4, pp. 724-736, Aug. 2002.

Z. Pan, F. Z. Peng, K. A. Corzine, V. R. Stefanovic, J. M. Leuthen, and

- Z. Pan, F. Z. Peng, K. A. Corzine, V. R. Stefanovic, J. M. Leuthen, and S. Gataric, "Voltage balancing control of diodeclamped multilevel rectifier/inverter systems," IEEE Transactions on Industry Applications, vol. 41, no. 6, pp. 1698–1706, Nov 2005.

- S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, J. Rodriguez, M. A. Perez, and J. I. Leon, "Recent advances and industrial applications of multilevel converters," IEEE Transactions on Industrial Elec- tronics, vol. 57, no. 8, pp. 2553–2580, Aug 2010.

- K. N. Raju, M.V.G. Rao, and M. Ramamoorthy, "Hybrid modulation technique for neutral point clamped inverter to eliminate neutral point shift with minimum switching loss," in TENCON 2015 - 2015 IEEE Region 10 Confer- ence, Nov 2015.

- K. N. Raju and V. G. R. Mannam, "An effective carrier based pwm technique for neutral point voltage stabilization of three level inverter," in 2014 Interna- tional Conference on Smart Electric Grid (ISEG), Sept 2014.

- Ms. D. Sindhuja and Mr. V. Yuvaraju M.E. "Five Level Active Neutral Point Clamped Converter based STATCOM", IRJET volume: 03 Issue: 04 | Apr-2016.

- Kuthuri Narasimha raju, Chandra Sekhar Obbu, M Ramamoorthy, " Appropriate switching state selection to Avoid capacitor imbalance in five-level NPC," International Journal of Power Electronics and Drives (IJPEDS) vol. 9, no. 1, pp. 676-681, 2018.

- Fang Zheng Peng, Jih-Sheng Lai, J. McKeever and J. VanCoevering, "A multilevel voltage-source converter system with balanced DC voltages," Power Electronics Specialists Conference, 1995. PESC '95 Record., 26th Annual IEEE, Atlanta, GA, 1995, pp. 1144-1150 vol.2.

- Senthil Kumar K, M. Sai Krishna Reddy, D. Elangovan and R. Saravana Kumar "Interleave isolated boost converter as a front end converter for fuel cell applications" Proceedings of the 2014 IEEE 2nd International Conference on Electrical Energy Systems, ICEES 2014, 202-205.

- S. K. S. Gunturi and M. S. K. Reddy, "IoT Based Domestic Energy Monitoring Device," in 2018 3rd International Conference for Convergence in Technology (I2CT), Pune, pp. 1–4 (2018).

#### **AUTHORS PROFILE**

**B. V. Pranav** is born in Andhra Pradesh, India. He is pursuing his Bachelor's degree in electrical and electronics engineering from KLEF, Vaddeswaram, Guntur His research interests include electrical drives, power electronics, electric machines, renewable-energy systems, and electrical hybrid vehicles.

Y. Mohana is born in Andhra Pradesh, India. She is pursuing her Bachelor's degree in electrical and electronics engineering from KLEF, Vaddeswaram, and Guntur. Her research interests include electrical drives, power electronics, electric machines, renewable-energy systems, and electrical hybrid vehicles.

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

Retrieval Number: B3433129219/2019©BEIESP DOI: 10.35940/ijeat.B3433.129219 Journal Website: <u>www.ijeat.org</u>