# Design and Performance Analysis of FIR Filter for VLSI Applications

P. Anjali, G. Navya Jyothi

Abstract: The Primary essential basis for planning and realization of Digital signal processor is space improvement and decrease in power utilization. The basic part for arranging and acknowledgment of processor is the FIR Filter. This Filter contains three basic blocks that area unit Adder blocks, memory block and number blocks. The execution of this Filter is basically subjective by the wide assortment that is the moderate block out of all. In this paper, the Filter has been planned using two completely different multipliers particularly Array multiplier and Booth multiplier. An upgrade has been finished in each with respect to space and lag. Additionally, minimum power utilization and degradation concerning lag and working frequency of the booth multiplier maintain extremely appropriate for the planning of the FIR Filter for less voltage and less power VLSI operations.

Key phrases-Finite Impulse Response (FIR), Array Multiplier, Booth Multiplier.

#### I. INTRODUCTION

The digital signal Processors realizes vast operations in medicine trade fields. Digital filters area unit helpful architectures for signal processing operations, and in signal study and evaluation [1]. The development within the knowledge, the no. of procedures needed for planning of digital filters have bit by bit decreased with the assistance of VLSI primarily established tools. FIR filter area unit have lot of beneficial regarding durability and secure limited section aspects and this filter even have larger machine potency so that dropping the amount of computations.

The essential procedure performed by digital filters is multiplication that successively needs a lot of hardware in time of space, rapidity, interruption elements, and a rise in power utilization resulting in ineffective filter style. Thus, it's needed to reduce these specifications and to scale back the computations performed in time of number. In the present work we are using two multipliers. Both contain FIR Filter. The structure of filter consists of adders, multipliers and D flip-flops. The first multiplier is often taken as a number that subsists of an oversized array of adders. Or else, it may be considered as a number that handles a lower array of adders, many times to finish the merchandise.

Revised Manuscript Received on February 05, 2020.

\* Correspondence Author

**Ms. P.Anjali\***, Assistant Professor, SR Engineering College, Ananthasagar, Warangal, Telangana, INDIA.

**Ms.G. Nvaya Jyothi,** Assistant Professor, SR Engineering College, Ananthasagar, Warangal, Telangana, INDIA.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC BY-NC-ND license (<a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>)

The second multiplier might be a structure that truncates the amount of reproduction steps. The process of the second multiplier is often considered as a two step procedure. The primary step consists of fractional product construction by the encoder of second multiplier. In the second consecutive stage, the two products are summed to create the final product passed through the carry save adder [2]. In the present work, the above filter has been considered victimization each them on top of specified multipliers.

Further, the outcome has similar regarding resource consumption, frequency of procedure, and power utilization. As an outcome, it's been established that the booth number achieves a similar process by compressing the amount of fractional product generated at every step thereby reducing the design regarding delay, quality, and power utilization specifications. Additionally, it involves smaller on chip space thereby creating it a lot of appropriate for practice in production trade.

#### II. FINITE IMPULSE RESPONSE FILTER

In signal processing, a filter that has finite response, because it settles to zero in finite time is called a FIR filter.

Fig 1: Architecture of the filter

Transfer function of the filter is:

$$H(z) = \sum_{n=0}^{N-1} h(n).z^{-n}$$

(1)

This filter has three types of basic building blocks: an adder block, a multiplier and a delay block. A D flip-flop will give the aim of delay component. An adder block adds the binary numbers and finishes its process. For every one bit count process we use 0.5 or full adder. A number building block results in a large amount delay within the style and thus has to be enhanced.

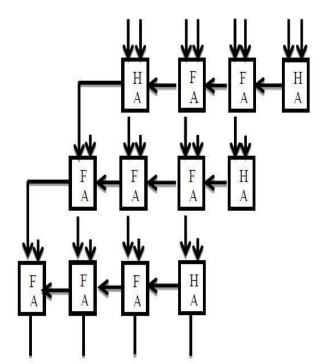

#### III. ARRAY MULTIPLIER

This multiplier is often taken as a number that involves an oversized array of adders or it may observe as a number that processes a slighter selection of adders, much extent to finish the merchandise. It is recycled as a reproduction building block during which associate degree selection of equal cells produce fractional product and therefore, the fractional product area unit assembled at the same time. The similar execution is employed in high presentation equipment wherever the amount of calculations had to be decreased.

Fig 2:Architecture of array multiplier

The interruption in adders is incredibly massive if ripple carry adders area unit used. This is often decreased by carry-look ahead adders. The most improvement of victimization associate degree array number is a step by step arrangement would simply be enforced such production of every phase will function associate degree input for future step. The interruption obtained is additionally comparative to the bit extent individual employed as associate degree contribution, however, this interruption will function an obstacle once the bit amount is massive therefore resulting in moderate actions.

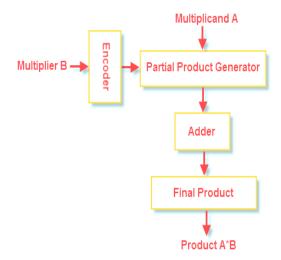

# IV. BOOTH MULTIPLIER

This multiplier is a moderate component within the planning of the filter thus it is essential that the rate of the multiplier should be such it produces the smallest amount interruption. One among the efficient and economical manner of accelerating the rate of the number is: scale back the amount of fractional product individual achieved throughout the reproduction method with the help of encoder. The booth secret writing theme is such slighter varieties of additives have to be compelled to be observed as compared to the traditional reproduction rule. It's been established that World Wide Web design shaped because of the adder and therefore, the number results in advance rate, and space optimization by decreasing the amount of fractional product needed and reducing the desired power utilization.

Fig 3: Architecture of the Multiplier

## V. SIMULATION RESULTS AND ANALYSIS

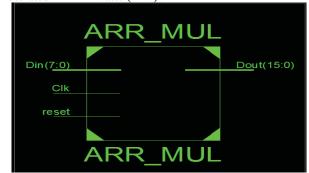

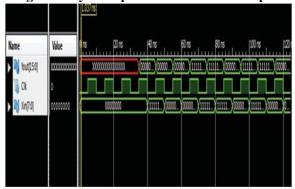

The two multipliers were realized by using the verilog HDL and evaluation is also balanced between both. The two multipliers are analyzed in time of power utilization, space consumption and interruption. Evaluation among style analysis taken from the Xilinx software of two multiplier filters considered area unit. The power utilization among two is disbursed victimization power analyzer and total power description has been prepared. The ability utilization is illustrated in milliWatts (mW).

Fig 4: Array Multiplier RTL Schematic Report

Fig 5: Array Multiplier Simulated output

Table I: Area Report of Array Multiplier

| Device Utilization Summary                     |      |           |             |  |  |  |

|------------------------------------------------|------|-----------|-------------|--|--|--|

| Logic Utilization                              | Used | Available | Utilization |  |  |  |

| Number of Slice Flip-Flops                     | 80   | 1,920     | 4%          |  |  |  |

| Number of 4 input LUTs                         | 303  | 1,920     | 15%         |  |  |  |

| Number of occupied slices                      | 218  | 960       | 22%         |  |  |  |

| Number of Slices containing only related logic | 218  | 218       | 100%        |  |  |  |

| Number of Slices containing unrelated logic    | 0    | 218       | 0%          |  |  |  |

| Total Number of 4 input LUTs                   | 306  | 1,920     | 15%         |  |  |  |

| Number used as logic                           | 303  |           |             |  |  |  |

| Number used as a route-thru                    | 3    |           |             |  |  |  |

| Number of bonded IOBs                          | 26   | 66        | 39%         |  |  |  |

| Number of BUFGMUXs                             | 1    | 24        | 4%          |  |  |  |

| Number of MULT 18X18SIOs                       | 4    | 4         | 100%        |  |  |  |

| Average Fan-out of Non-Clock Nets              | 2.70 |           |             |  |  |  |

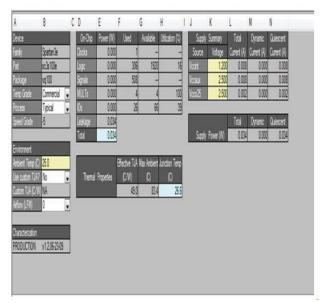

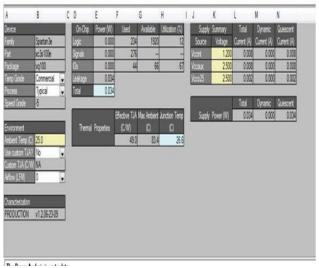

Fig 6: Array Multiplier Power evaluation

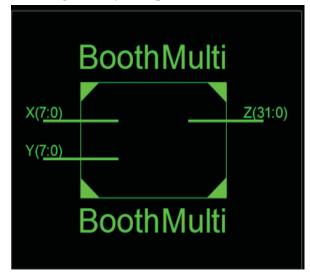

Fig 7: Booth Multiplier RTL schematic report

Fig 8: Booth Multiplier simulated output

Table II: Area Report of Booth Multiplier

| Device Utilization Summary                     |      |           |             |  |  |  |

|------------------------------------------------|------|-----------|-------------|--|--|--|

| Logic Utilization                              | Used | Available | Utilization |  |  |  |

| Number of 4 input LUTs                         | 232  | 1,920     | 12%         |  |  |  |

| Number of occupied slices                      | 119  | 960       | 12%         |  |  |  |

| Number of Slices containing only related logic | 119  | 119       | 100%        |  |  |  |

| Number of Slices containing unrelated logic    | 0    | 119       | 0%          |  |  |  |

| Total Number of 4 input LUTs                   | 234  | 1,920     | 12%         |  |  |  |

| Number used as logic                           | 232  |           |             |  |  |  |

| Number used as a route-thru                    | 2    |           |             |  |  |  |

| Number of bonded IOBs                          | 44   | 66        | 66%         |  |  |  |

| Average Fan-out of Non-Clock Nets              | 3.07 |           |             |  |  |  |

Fig 9: Booth Multiplier Power evaluation

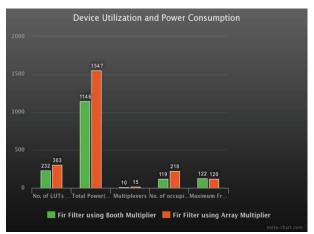

#### COMPARISON OF THE RESULTS

| Type of Multiplier | Area (No. of<br>LUTs) | Power (mW) | Multiplexers | occupied slices | Maximum<br>frequency |

|--------------------|-----------------------|------------|--------------|-----------------|----------------------|

| Booth Multiplier   | 232                   | 1547       | 10           | 119             | 122 MHz              |

| Array Multiplier   | 303                   | 1146       | 15           | 218             | 120MHz               |

Fig 10: Performance analysis of both Multipliers

Hence, the speed further increase. It's obvious from the above chart that the second multiplier power utilization is less. And also the first multiplier power utilization is more, thus creating it a lot of appropriate for the planning of the above digital filter.

## VI. CONCLUSION

Traditionally the FIR filters that include vast operation in a Signal processing be advanced victimization ancient DSP algorithms. By means of the development within the machinery, the FIR filters area unit individual advanced victimization VLSI machinery. The analysis work started during this paper has managed sufficient results, and have incontestable the potency of high level development Approaches. During this, the FIR filter has been considered by both multipliers. From this work, it's finished that chip space of FIR filter designed by booth number is decreased which in addition while not rising any power dissipation.

# REFERENCES

- Y.H.Chen, "An accuracy-adjustment fixed-width Booth multiplier based on multilevel conditional probability," IEEE Trans. Very Large Scale Integration. (VLSI) Syst., vol. 23, no. 1, pp. 203–207, Jan. 2015.

- P.Anjali, G.Renuka.," High accuracy Fixed Width Modified Booth Multiplier Based on MLCP",oct-2016, International Journal of Scientific Engineering and Technology Research(IJSETR), Vol.05,Issue.31,pp. 6401-6411.

- 3. Arulmurugan R., Chandramouli A."Modeling of PV powered seven-level inverter for power quality improvement",2019, Springer Science and Business Media Deutschland GmbH,vol.105,pp.113-121.

- M. H. Tsai, "Low-error reduced- width Booth multipliers for DSP applications," IEEE Trans. Circuits Syst. I, vol. 50,no. 11, pp. 1470–1474, Nov. 2003.

- Sumit Vaidya, Deepak Dandekar, "Delay-power performance comparison of Multipliers in VLSI circuit design", International Journal

- of Computer Networks & Communications (IJCNC), Vol.2, No.4, July 2010

- Karri C., Rajababu D., Raghuram K. "Optimal bidding strategy in deregulated power market using krill herd algorithm", 2019, Springer Verlag, vol. 698, pp. 43-51.

- 6. Swetha T., Srinivas S."A novel IEEE-754 floating-point butterfly

- architecture based on multi operand adders",2019, Blue Eyes Intelligence Engineering and Sciences Publication,vol.7,Issue 5,pp.55-60.

- Ravi N, Rao TS (2011).," A New Design for Array Multiplier with Trade off in Power and Area 8".,pp.533-537.

- Kumar V., Anuradha P.," Power consumption optimization and home automaton using smart sensor networks ", 2019, Blue Eyes Intelligence Engineering and Sciences Publication,vol.8, 6 Special Issue 4,pp. 837-841.

## **AUTHORS PROFILE**

**Ms. P.Anjali** received her M.Tech in VLSI and B.Tech in Electronics and Communication Engineering. Working as Assistant Professor from SR Engineering College, Ananthasagar, Warangal, Telangana, INDIA.

Ms.G. Nvaya Jyothi received her M.Tech in VLSI and B.Tech in Electronics and Communication Engineering. Working as Assistant Professor from SR Engineering College, Ananthasagar, Warangal, Telangana, INDIA.