# Impact of Threshold Voltage roll off in Ultra Thin Fully Depleted Silicon on Insulator **MOSFET**

## Chandra Shakher Tyagi1, R.L. Sharma, Prashant Mani

Abstract: This article is discussing about threshold voltage roll off effect in Ultra Thin Fully Depleted Silicon on Insulator MOSFET. The device performance is improved due to the reduction in threshold voltage roll off. The thickness of oxide layer is optimized to 2nm which also have a vital role in improvement of device's throughput. The effect of oxide thickness on parasitic parameter also discussed. Device conductance and transconductance also take in account on simulating the ultra thin fully depleted SOIMOSFET.

Keywords **Threshold** voltage, SOI. MOSFET, Transconductance.

#### I. INTRODUCTION

$N_{

m ow}$  days the scaling is most interesting part of modern device design engineering due to reduction in chip size. Industry demand for improved performance, scaling of SOI MOSFET's has reached the regime of short channel for improved speed, narrow width for lower power consumption and ultra thin silicon film layer for reducing the short channel effects. Silicon - On - Insulator (SOI) devices are a relatively widely used technology. Although the technology has been used around since the 1960"s, SOI devices are only recently becoming commercially viable, due to the cost associated in producing the devices 1-3. SOI devices are an advancement of standard MOSFET technology. The difference between SOI and MOSFET technology is the inclusion of an insulating layer. SOI MOSFET's are created from a silicon layer which is very thin is placed on above the insulating layer. SOI MOSFET's execution advantage over ordinary mass MOSFET's is for the most part from lower normal edge voltage because of transient floating-body (FB) activity and lower intersection capacitance 4-6. The fractional exhausted (PD) rather than completely drained (FD) SOI has gotten the attractive decision for standard computerized applications,

Revised Manuscript Received on February 05, 2020.

\* Correspondence Author

Chandra Shakher Tyagi1\*, Department of Electronics and Communication Engineering, Noida International University, Noida, U.P. INDIA Email: tyagi\_shekhar@yahoo.co.in

R.L. Sharma , Department of Electronics and Communication Engineering, Noida International University, Noida, U.P. INDIA Email:. rlsharmadigudr@yahoo.co.in

Prashant Mani, SRM Institute of Science and Technology, U.P. INDIA Email: 3prashantmani29@gmail.com

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/)

because of the straightforward of assembling, better control of short channel impacts, bigger plan window for the edge voltage, and lower self-warming effect.[1] The short channel effect (SCE) is diminished as parallel bearing building actualized in gadget. DIBL and Subthreshold rolloff is likewise considered . The investigation of Kink impact is additionally considered and we discover the gadget is for all intents and purposes liberated from kink.[2]

Silicon-on-Insulator (SOI) innovation gives numerous preferences over mass silicon CMOS handling. Specifically higher speed, lower power dissemination, high radiation resilience, lower parasitic capacitance, low short channel impacts, high subthreshold voltage swing, fabricating similarity with the current mass silicon CMOS innovation. In this paper a portion of the SOI COMS models which are presently considered as an choice to mass CMOS innovation and related ideas are displayed.[8]

The edge voltage and ideality factor models of the front and back entryways have been confirmed with numerical reproductions as far as the gadget geometry parameters and the applied predisposition voltages, just as with test results for gadgets with channel length down to 17 nm. In view of the base estimations of the front and back surface possibilities of softly doped UTBB FD-SOI MOSFETs, straightforward logical models for the front and back entryway limit voltages and ideality factors have been determined as far as the gadget geometry parameters and the applied inclination voltages with back door control.[9]

Presented a model that emulates an UT-FDSOI-MOSFET using COMSOL Multiphysics. The model reenacts the Electrostatic potential and the buoy and scattering streams on the device using Poisson condition and Drift and Diffusion conditions for the charge transporters. The Threshold Voltage dependence was expelled on the indirect access voltage and it agrees with preliminary outcomes. We have in like manner showed the dependence of the transconductance on the indirect access voltage and the fundamental structure agrees with exploratory results from a SOI-MOSFET.[10]

## II. METHODOLOGY OF THRESHOLD MODELING (V<sub>TH</sub>)

## A. Submission of the paper

Because of ceaseless decrease in highlight size of gadget the demonstrating of nano scale SOI MOSFET become increasingly extreme.

## Impact of Threshold Voltage roll off in Ultra Thin Fully Depleted Silicon on Insulator MOSFET

A basic strategy to show SCE, threshold voltage move off in nanoscale n-channel FDSOI MOSFETs is exhibited. [3,4]The decrease of limit voltage with littler door length is a generally realized short channel impact named the "edge voltage move off" has been mimicked. By utilizing edge voltage(Vth), current-voltage bend have been distinguished for different working locales of MOSFETs with different channel lengths and furthermore for numerous oxide thickness.[6,7] To demonstrate the rightness of the proposed model the reproduced outcomes have been contrasted and the accessible scientific information. The explanatory articulations inferred in the present model can be a useful device in gadget plan and advancement.

For MOSFET the connection between the physical gadget parameter and limit voltage is given as [8]

$$V_m = \phi_{ms} + rac{kT}{q} \ln \left( rac{2C_0 \dots k - T}{q^2 m_1 r_2}

ight) + rac{q_1^2 \pi^2}{2m r_2 r_2^2}$$

The primary term of (1), is the work contrast between the entryway and the silicon film, which is equivalent to - 0.17eV in our recreations. The subsequent term speaks to the potential  $\Phi$  in the channel; it is contrarily relative to the silicon film thickness tsi and furthermore relies upon the oxide thickness. The third term is the most reduced subband vitality above conduction band minima. It is a quantum mechanical term which shifts relying upon the parting of the conduction band vitality level into subbands.

Limit voltage change for channel length decrease can be found by the accompanying articulation.

Where rj is the profundity of the source and channel intersection, Wm the most extreme width of the exhaustion layer, Lch is the gadget channel length. The estimations of various parameters are accessible in [9]. Edge voltage move off can be found by subtracting Vth from the limit voltage, Vth as:

Threshold voltage roll-off  $=V_{rh}-\Delta V_{rh}$

The channel conductance of the gadget likewise relies upon edge voltage, is characterized by the accompanying articulation

$$g_{d} = \frac{W_{eff} \ \mu_{eff} \ C_{ox}}{L_{ch}} (V_{gs} - V_{th})$$

$$g_{m} = \frac{W_{eff} \ \mu_{eff} \ C_{ox}}{L_{ch}} (V_{gs} - V_{th})$$

(3)

Here  $W_{eff}$  is the effective width of channel  $\mu_{eff}$  is effective electron mobility  $C_{ox}$  is oxide capacitance  $L_{ch}$  is channel Length

#### III. RESULTS AND DISCUSSIONS

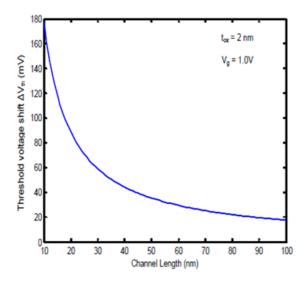

Figure 1 Threshold voltage shift ( $\Delta V_{th}$ ) with channel length.

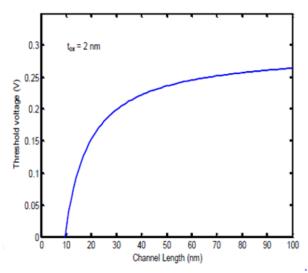

Figure 2 Threshold voltage roll-off for nanoscale MOSFET.

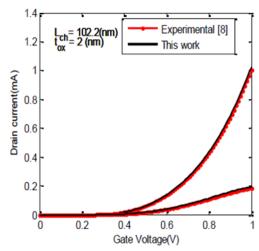

Figure 3 Drain current versus drain voltage.

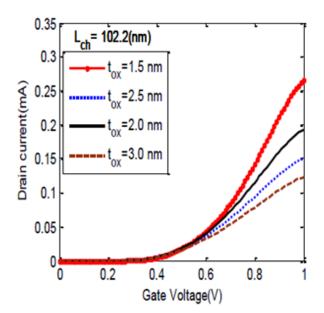

Figure 4 Channel conductance versus drain

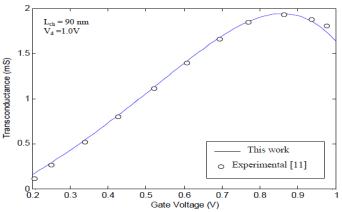

Figure 5 Transconductance versus gate voltage

The channel current versus door voltage is appeared in Fig.4. The nonstop lines for this work and the circles speak to the exploratory outcomes. Channel current are plotted for 50mV and 1.0V of channel voltages and contrasted and the exploratory information. It is seen that the exchange attributes lies near the exploratory outcomes for low just as high channel inclination. The impact of oxide thickness on channel current versus door voltage is plotted in Fig.5. It is seen that when the oxide thickness is expanded, the channel current reductions and the bends move descending. This is on the grounds that, the oxide capacitance increments with the decline in oxide thickness and the oxide capacitance is legitimately relative to the channel current. The transconductance vs gate voltage plotted in Fig 6. It is observed as the gate voltage increase the transconductance also increase linearily, but after gate voltage increases 0.9 V the tranconductance decreases.

#### IV. CONCLUSIONS

This paper shows a straightforward methodology of limit voltage move off system for nanoscale n channel nano scale MOSFET. The scientific articulation for limit voltage move off has created. By utilizing this articulation the edge voltage move off has been reproduced by thinking about the distinctive physical gadget parameters and gadget channel length. Besides, move attributes and output qualities of the gadget for channel length 102 nm and oxide thickness 2.0 nm have watched. The outcomes show a generally excellent concurrence with the trial information. Moreover gadget channel conductance and transconductance have been reproduced and contrasted and exploratory outcomes. The impact of oxide thickness on I-V qualities has additionally been reenacted and shows that it greatly affects channel current. To advance improvement of this model, other reasonable impacts can be accounted, for example, 3D parasitic impacts that are particularly serious in nano scale MOSFETs.

#### REFERENCES

- Cristoloveanu, Sorin. "Silicon on insulator technologies and devices: from present to future." Solid-State Electronics 45.8 (2001): 1403-1411

- Kruppa, W., and J. Brad Boos. "Examination of the kink effect in InAlAs/InGaAs/InP HEMTs using sinusoidal and transient excitation." *IEEE Transactions on Electron Devices* 42.10 (1995): 1717-1723.

- Jin, Li, et al. "Two-dimensional threshold voltage analytical model of DMG strained-silicon-on-insulator MOSFETs." *Journal of Semiconductors* 31.8 (2010): 084008.

- Dhar, Subhra, Manisha Pattanaik, and Poolla Rajaram. "Advancement in nanoscale CMOS device design en route to ultra-low-power applications." VLSI Design 2011 (2011).

- He, Jin, et al. "Analytic carrier-based charge and capacitance model for long-channel undoped surrounding-gate MOSFETs." *IEEE Transactions on Electron Devices* 54.6 (2007): 1478-1485.

- 6. Jariwala, Deep, et al. "Emerging device applications for semiconducting two-dimensional transition metal dichalcogenides." *ACS nano* 8.2 (2014): 1102-1120.

- Sathi, EJ Zinat Mahol, and Quazi DM Khosru. "An accurate model of inversion carrier effective mobility considering scattering mechanisms for nanoscale mos devices." *International Conference on Electrical & Computer Engineering (ICECE 2010)*. IEEE, 2010.

- 8. Tiwari S.P., S. K, Bansal K.K. "A Survey of Metaheuristic Algorithms for Travelling Salesman Problem" International Journal Of Engineering Research & Management Technology 1(5)

- Jaju, Vishwas, and Vikram Dalal. "Silicon-on-insulator technology." EE 530 (2004): 1-12.

- Fasarakis, Nikolaos, et al. "Analytical modeling of threshold voltage and interface ideality factor of nanoscale ultrathin body and buried oxide SOI MOSFETs with back gate control." IEEE Transactions on Electron Devices 61.4 (2014): 969-975.

- Bustamante, José, and Lionel Trojman. "Ultra-thin Depleted Silicon on Insulator mosfet: A Simulation Based on COMSOL Multiphysics." Avances en Ciencias e Ingenierías 4.1 (2012): C42-C45.

### **AUTHORS PROFILE**

Mr Chandra Shakher Tyagi , Research Scholar, Noida International University. Has completed B.Tech CSE , M.Tech VLSI. Having 8 Years Teaching Experience in SRMIST , NCR Campus. He has 14 research papers to his credit published in national and international journals. He has a fellow of ISTE, IETE.

# Impact of Threshold Voltage roll off in Ultra Thin Fully Depleted Silicon on Insulator MOSFET

(Dr.) R L Sharma has more than 46 years of industry and teaching experience. He had been a communication officer for 35 years in BSF and was also involved in national and international operations. He is highly decorated officer and is recipient of Police medal of gallantry, Bar to police medal for gallantry, Police medal for meritorious services, President's Police medal

for distinguished services and several commendations. He was an instructor in BSF signal training school. For the last 11 years, he is in academics as Professor and had served in AKG Engg. College, Ghaziabad, HR institute of technology, Ghaziabad and Noida International University. His areas of interest are optical fibers, optical sensors, antenna and wave propagation, optical networks and wireless communications. He has 27 research papers to his credit published in national and international journals and is guiding research to 06 students in above areas. He has been a Dy. Proctor in AKG Engg. College, Ghaziabad and is a fellow of IETE.

Dr.Prashant Mani, Associate Professor, SRMIST, NCR Campus, Ghaziabad, Has completed B. Tech Electronics & Instrumentation Engineering, M. Tech VLSI Design and Ph. D VLSI. He has published more than 33 papers in international journals and