# A Novel Symmetrical Multilevel Inverter with Reduced Switch Count

# Ujwala Gajula

Abstract: Multilevel inverters produced lot of interest in academia and industry as they are becoming feasible technology for number of applications. These are considered as the progressing power converter topologies. To generate a quality output waveform with minimum number of switches, reduced switch multilevel inverter topologies has come in focus. This paper introduces a modified symmetrical MLI with reduced component count thereby ensuring the minimum switching losses, reduced total harmonic distortion, Size and installation cost. By proper combination of switches it produces a staircase output waveform with low harmonic distortion. In this paper novel symmetrical inverter topology with reduced component count based on level shift phase opposition and disposition PWM (PODPWM) is proposed. The results are validated using MATLAB/SIMULINK.

Keywords: Reduced switch MLI, Level shift pulse width modulation, Switching losses, Total Harmonic distortion, Staircase output Waveform.

# I. INTRODUCTION

The term "Multilevel Inverter" has played an important role in the recent years and is suitable for medium to highvoltage applications such as renewable energy sources, Industrial drives, fans, blowers because of their capability to synthesize output voltage waveform with better harmonic spectra, better output voltage. With proper arrangement of voltage sources and power switching semiconductor devices a multilevel output can be obtained. The three conventional MLI types are Flying capacitor Multilevel inverter, Diode Clamped Multilevel inverter and cascaded H Bridge Multilevel Inverter [1]. Although the above mentioned conventional MLI finds number of applications, all these topologies need more number of switches to produce higher voltages. So in the recent years the research focuses on reducing the number of components. Reducing the number of diodes used, voltage sources, switches and capacitors can improve the quality as well as reduce the switching losses, overall cost etc., [5]. In this paper a novel symmetrical inverter topology with reduced component count based on level shift phase opposition and disposition PWM (PODPWM) is proposed.

#### **II. PROPOSED NOVEL INVERTER TOPOLOGY**

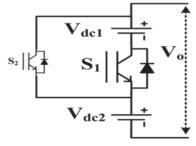

The fundamental unit of the proposed novel inverter topology is given in fig.1 (a).

Revised Manuscript Received on April 18, 2020. \* Correspondence Author

**Ujwala Gajula\***, Assistant Professor, EEE Department, G.N.I.T.S, India. E-Mail: <u>gjujwala@gmail.com</u>

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC BY-NC-ND license (<u>http://creativecommons.org/licenses/by-nc-nd/4.0/</u>)

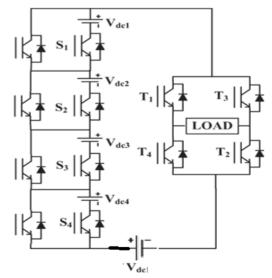

Retrieval Number: D7964049420/2020©BEIESP DOI: 10.35940/ijeat.D7964.049420 Journal Website: <u>www.ijeat.org</u> It consists of two isolated DC sources and six unidirectional switches ( $T_1$ ,  $T_2$ ,  $T_3$ ,  $T_4$ ,  $S_1$  and  $S_2$ ). The basic unit generates five level of output voltage ( $2V_{dc}$ ,  $V_{dc}$ , 0,  $-V_{dc}$ ,  $-2V_{dc}$ ). The switching states are given in Table 1. Fig.1 (b) gives the proposed 11 level symmetrical novel inverter topology with reduced switch count.

Fig.1. a) Basic Structure

| S.No. | Level of<br>Combined<br>Signal | Switches<br>in ON<br>State                          | Output<br>Voltage |

|-------|--------------------------------|-----------------------------------------------------|-------------------|

| 1     | 2                              | $S_1, T_1, T_2$                                     | $+2V_{dc}$        |

| 2     | 1                              | $S_2, T_1, T_2$                                     | + V <sub>dc</sub> |

| 3     | 0                              | T <sub>1</sub> , T <sub>3</sub>                     | 0                 |

| 4     | -1                             | S <sub>2</sub> , T <sub>3</sub> ,<br>T <sub>4</sub> | -V <sub>dc</sub>  |

| 5     | -2                             | S <sub>1</sub> , T <sub>3</sub> ,<br>T <sub>4</sub> | -2V <sub>dc</sub> |

Fig.1. b) proposed MLI Topology

In the proposed symmetrical reduced switch Multilevel Inverter topology the number of switches (N<sub>s</sub>) required to produce number of levels  $(N_L)$  is given by eq (1) & (2) and the maximum output voltage is given by eq(3).

$$Ns = 2n+2$$

----- (1)

Where n is the number of DC sources used  $N_L$ :

$$= 2Ns - 5 - ... (2)$$

$V_{Max,O} = n V dc ---- (3)$ The Table 2 below gives comparison of number of switches used in conventional cascaded H- Bridge inverter and proposed symmetrical MLI topology.

Table 2. Comparison of proposed and Conventional MLI's

| 1411/1 5                |           |                  |                  |                      |  |  |

|-------------------------|-----------|------------------|------------------|----------------------|--|--|

| Parameters              | СНВ       | Ref [3]          | Ref[4]           | Proposed<br>Topology |  |  |

| Number of DC<br>sources | n         | n                | n                | n                    |  |  |

| sources                 |           |                  |                  |                      |  |  |

| Number of               | 2n+1      | 2n+1             | 2n+1             | 2n+1                 |  |  |

| levels                  |           |                  |                  |                      |  |  |

| Number of               | 4n        | 3n               | 2n+4             | 2n+2                 |  |  |

| Switches                |           |                  |                  |                      |  |  |

| Output Voltage          | $nV_{DC}$ | nV <sub>DC</sub> | nV <sub>DC</sub> | nV <sub>DC</sub>     |  |  |

The switching states of the proposed symmetrical reduced switch multilevel inverter are given in Table 3.

| S.No | Conducting Switches                                                                                  | Output<br>Voltage |

|------|------------------------------------------------------------------------------------------------------|-------------------|

| 1    | S <sub>4b</sub> ,S <sub>3b</sub> ,S <sub>2b</sub> , S <sub>1b</sub> , H <sub>1</sub> ,H <sub>4</sub> | +V <sub>dc</sub>  |

| 2    | $S_{1a}$ , $H_1$ , $H_4$ , $S_{4b}$ , $S_{3b}$ , $S_{2b}$                                            | $+2V_{dc}$        |

| 3    | S <sub>2a</sub> ,S <sub>1b</sub> ,H <sub>1</sub> ,H <sub>4</sub> ,S <sub>4b</sub> ,S <sub>3b</sub>   | +3V <sub>dc</sub> |

| 4    | S <sub>3a</sub> ,S <sub>2b</sub> ,S <sub>1b</sub> ,H <sub>1</sub> ,H <sub>4</sub> ,S <sub>4b</sub>   | $+4V_{dc}$        |

Table 3. Switching States of the Proposed MLI

| 5  | S <sub>4a</sub> ,S <sub>3b</sub> ,S <sub>2b</sub> ,S <sub>1b</sub> ,H <sub>1</sub> ,H <sub>4</sub>   | $+5V_{dc}$        |

|----|------------------------------------------------------------------------------------------------------|-------------------|

| 6  | H <sub>1</sub> ,H <sub>4</sub>                                                                       | 0                 |

| 7  | S <sub>4b</sub> ,S <sub>3b</sub> ,S <sub>2b</sub> , S <sub>1b</sub> , H <sub>2</sub> ,H <sub>3</sub> | -V <sub>dc</sub>  |

| 8  | $S_{1a}$ , $H_2$ , $H_3$ , $S_{4b}$ , $S_{3b}$ , $S_{2b}$                                            | -2V <sub>dc</sub> |

| 9  | S <sub>2a</sub> ,S <sub>1b</sub> ,H <sub>2</sub> ,H <sub>3</sub> ,S <sub>4b</sub> ,S <sub>3b</sub>   | -3V <sub>dc</sub> |

| 10 | S <sub>3a</sub> ,S <sub>2b</sub> ,S <sub>1b</sub> ,H <sub>2</sub> ,H <sub>3</sub> ,S <sub>4b</sub>   | -4V <sub>dc</sub> |

| 11 | S <sub>4a</sub> ,S <sub>3b</sub> ,S <sub>2b</sub> ,S <sub>1b</sub> ,H <sub>2</sub> ,H <sub>3</sub>   | -5V <sub>dc</sub> |

### **III. CONTROL SWITCHING SCHEME**

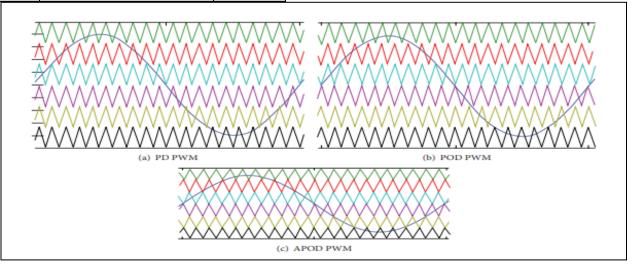

The high frequency conventional switching techniques which provide faster response are pulse width modulation, Space vector modulation and sinusoidal pulse width modulation. Later many carrier based PWM techniques has been introduces which reduces distortions [2]. Carrie based PWM techniques are divided into Phase Shift PWM (PS-PWM) and Level Shift PWM (LS-PWM). In PS-PWM technique different phase shifted carrier signals are used with synchronization of Zero crossing of each carrier and voltage reference, where in LS-PWM technique only

one carrier signal is used to produce different voltage levels. The LS-PWM is the mostly used technique. This is again divided into three types namely phase disposition PWM (PD-PWM), phase opposition and disposition PWM (PODPWM), and alternative phase opposition and disposition PWM (APOD-PWM). The carrier alignment for the carrier based Level shift PWM techniques is shown in Figure 2.

Fig 2. Carrier alignment of Level Shift PWM Techniques

Retrieval Number: D7964049420/2020©BEIESP DOI: 10.35940/ijeat.D7964.049420 Journal Website: <u>www.ijeat.org</u>

# **III. RESULTS AND DISCUSSION**

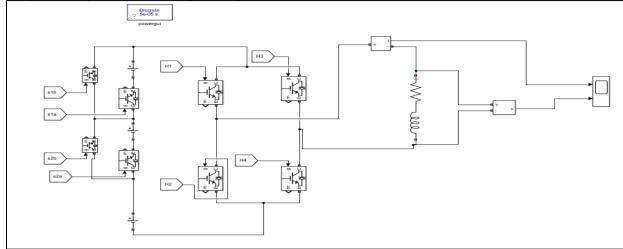

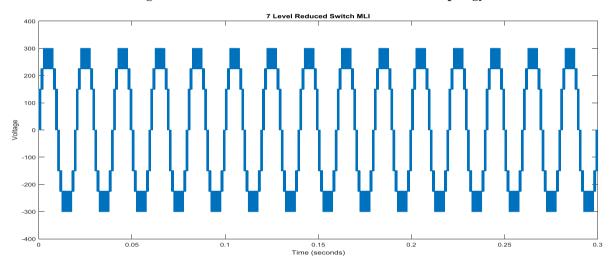

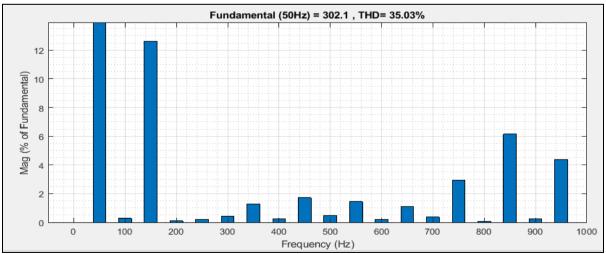

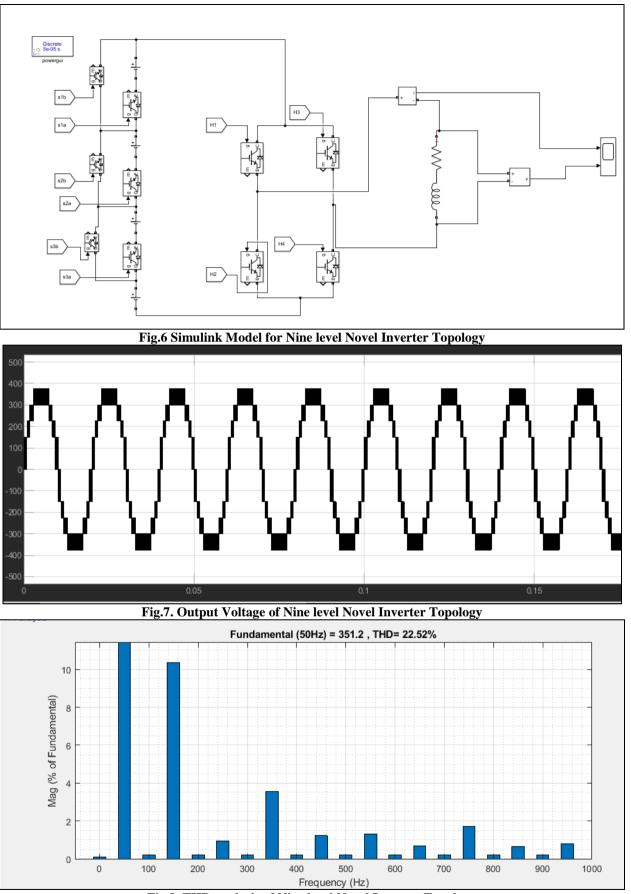

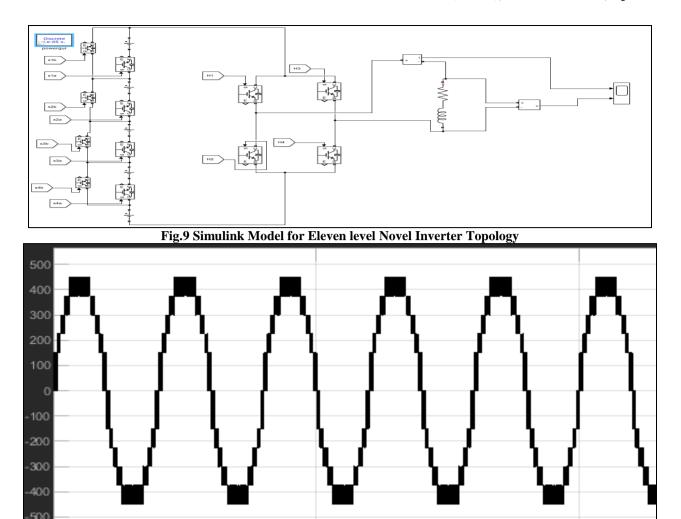

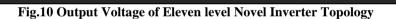

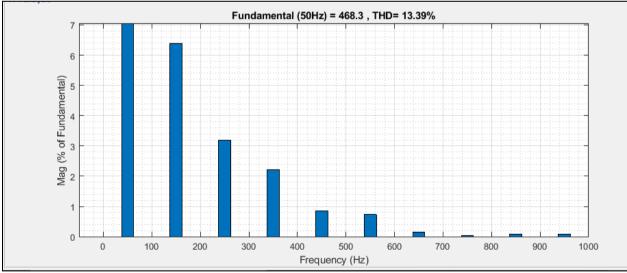

Fig. 3, Fig. 6, Fig.9 gives the simulink model of Novel Inverter Topology symmetrical MLI for 7, 9 and 11 levels. Fig. 4, Fig. 7 and Fig. 10 shows the output voltage waveform for different levels. Fig. 5, Fig. 8 and Fig. 11gives the total harmonic distortion for 7, 9 and 11 levels andfrom Fig.12 it is noted that as the number of levels increasestheTHDisreduced.

Fig.3 Simulink Model for seven level Novel Inverter Topology

Fig.4. Ouput Voltage of seven level Novel Inverter Topology

Fig.5. THD analysis of seven level Novel Inverter Topology

Retrieval Number: D7964049420/2020©BEIESP DOI: 10.35940/ijeat.D7964.049420 Journal Website: <u>www.ijeat.org</u>

Fig.8. THD analysis of Nine level Novel Inverter Topology

Retrieval Number: D7964049420/2020©BEIESP DOI: 10.35940/ijeat.D7964.049420 Journal Website: <u>www.ijeat.org</u>

Fig.11. THD analysis of Eleven level Novel Inverter Topology

0.1

Published By:

& Sciences Publication

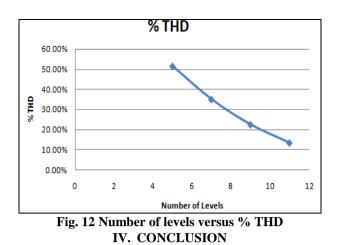

A modified symmetrical level inverter with reduced number of switches is designed in MATLAB/SIMULINK. As the number of levels increases the switches used are drastically reduced thereby reducing the switching losses when compared to the conventional multilevel inverter. A 11 level stepped output waveform is generated using POD-PWM. POD-PWM is observed as more efficient than other PWM techniques. The Total harmonic distortion is also reduced as the number of levels is increased. Fig. 13 shows plot of Number of levels versus No. of switches for Proposed and Conventional MLI.

Fig. 13 Number of levels versus No. of switches for Proposed and Conventional MLI

#### REFERENCES

- Prabhat Ranjan Bana, Kaibalya Prasad Panda, R. T. Naayagi, Pierluigi Siano, And Gayadhar Pandal "Recently Developed Reduced Switch Multilevel Inverter for Renewable Energy Integration and Drives Application: Topologies, Comprehensive Analysis and Comparative Evaluation" IEEE Access, vol. 7, pp. 54888–54909, 2019.

- H. Abu-Rub, J. Holtz, G. Baoming, and J. Rodriguez, "Mediumvoltage multilevel converters—State of the art, challenges, and requirements in industrial applications," IEEE Trans. Ind. Electron, vol. 57, no. 8, pp. 2581–2596, Aug. 2010.

- K. Thakre, K.B. Mohanty, V.S. Kommukuri, and A. Chatterjee, "Experimental validation of a modular multilevel inverter with less number of switches," Proc. In: 19th National Power Systems Conference (NPSC), IIT Bhubaneswar, India, 2016, pp. 1-5.

- 4. E. Babaei, S.H. Hosseini, New cascaded multilevel inverter topology with minimum number of switches, Energy Conversion and Management, 50, 2761–2767, 2009.

- R. R. Karasani, V. B. Borghate, P. M. Meshram, H. M. Suryawanshi, and S. Sabyasachi, "A three-phase hybrid cascaded modular multilevel inverter for renewable energy environment," IEEE Trans. Power Electron., vol. 32, no. 2, pp. 1070–1087, Feb. 2017.

Retrieval Number: D7964049420/2020©BEIESP DOI: 10.35940/ijeat.D7964.049420 Journal Website: <u>www.ijeat.org</u> AUTHOR'S PROFILE

**Ujwala Gajula** received her B-Tech in Electrical & Electronics Engineering from JNTUH in the year 2004 and M.Tech in Power Electronics & Electric Drives from JNTUH in the year 2010. She is member of IEI and ISTE. Her areas of interest are Power Quality, Renewable Energy Sources.