# **Design and Implementation of AES** Algorithm

T.Krishnarjuna Rao, Aftab Jamil, I.V.Saikumar, J.Sairam

Abstract: In this paper the Advanced Encryption Standard (AES) was endorsed by the National Institute of Standards and Technology in 2001. It was intended to supplant the maturing Data Encryption Standard (DES) and be valuable for a wide scope of utilizations with differing throughput, zone, control dissemination and vitality utilization necessities . Though they are very adaptable, FPGAs are regularly less effective than Application Specific Integrated Circuits (ASICs); There have been numerous AES executions that attention on acquiring high throughput or low region use, however almost no examination done in the territory of low power or vitality productive based AES; actually, it is uncommon for assessments on power dispersal to be made by any means. This postulation introduces new effective equipment usage to those propelled encryption standard (AES) calculation. Two primary commitments are introduced in this thesis, the initial you quit offering on that one will be a secondary speed 128 odds AES encrypted, and the second person is another 32 odds AES configuration. In 1st commitment An 128 odds circle unrolled sub-pipelined AES encrypted is exhibited. In this encrypted a effective blending to those encryption methodology sub-steps will be executed following relocating them. Those second commitment displays An 32 odds AES plan. In this design, the S-BOX is actualized for inward pipelining Furthermore it is imparted the middle of those principle round and the enter development units. Also, the way development unit is actualized will fill in on the fly What's more previously, parallel with the fundamental round unit. These outlines bring attained higher FPGA (Throughput/Area) effectiveness analyzing to past AES outlines.

Keywords—AES, Encryption, AES-128 bits

#### Revised Manuscript Received on July 05, 2019.

T.Krishnarjuna Rao, Associate Professor, Department of ECE, Siddhartha Institute of engineering and technology , Hyderabad

Aftab Jamil, UG Student, Siddhartha Institute of engineering and technology

I.V .Saikumar, Siddhartha Institute of engineering and technology

#### 1. INTRODUCTION

A large number cryptographic calculations were proposed, for example, such that the information encryption standard (DES), the elliptic bend cryptography (ECC), the propelled encryption standard (AES) Also different calculations. Huge numbers scientists Furthermore hackers are dependably attempting will break these calculations utilizing beast compel Also side channel strike. Exactly strike were fruitful Likewise it might have been those case to those information encryption standard (DES) over 1993, the place the distributed cryptanalysis assault Might break those des.

The Advanced encryption standard (AES) is recognized these days as a standout amongst those strongest distributed cryptographic algorithms, the place it might have been embraced by those national establishment for guidelines What's more engineering (NIST) after those neglecting of the information encryption standard (DES). Moreover, it may be utilized within large portions provisions for example, Previously, RFID cards, atm Machines, cell-phones Also extensive servers.

Because of the vitality of the AES algorithm and the various provisions that it has, the principle concern about this proposal will make introducing new productive fittings usage to this algorithm.

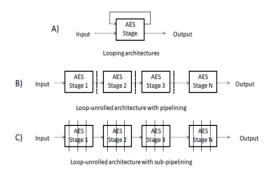

Figure.1. AES structural design

### **Proposed work**

AES executions can be partitioned into three primary sorts relying upon information way width. The main sort accompanies 8-bits information way going for low region structures. The subsequent kind is the 32-bits information way structures which procedure each state cluster line or

segment together focusing on medium throughput а applications. The last kind of

Published By:

& Sciences Publication

387

executions is the 128-bits circle unrolled designs which targets exceptionally rapid applications. For the most part, structures with 8 bits and 32 bits information ways use circling models. Circling designs utilize a one phase of AES encryptor/decryptor with a criticism toward the end

In this route the information will experience this phase until finishing the needed number of iterations which may be dictated as stated by span of the utilized way. This AES stage Might be best an encryptor or a encryptor with decryptor What's more it incorporates the equipment usage to the four AES steps: movement Rows Step, byte substitution utilizing those substitution box (S-BOX), blend Columns and include round magic.

For high velocity provisions which will be executed Similarly as full 128 odds information path, the throughput might a chance to be multiplied ideally n times Toward applying those circle unrolled structural engineering. In this architecture, replicates of the AES phases need aid actualized for series, the place n number from claiming phases may be utilized. Over AES 128 odds way measure architecture, n may be 10, Likewise 10 AES iterations are required with complete the encryption/decryption forms.

### 2. Discussion of result

### The Data Encryption Standard (DES):

In the early 1970"s, IBM created those information encryption standard as a symmetric-key cryptography algorithm. This algorithm might have been embraced by the national foundation about standard What's more innovation (NIST) On 1977, the place it might have been distributed in the national data transforming standard (FIPS) production 46 [20]. The des comprises of 64 odds information piece with way size about 56 bits, the place 16 encryption rounds will be connected of the information should finish those encryption transform.

Those des algorithm begins will fizzle then afterward a few distributed beast energy strike. The straight cryptanalysis strike [22] Might break the des and constructed it unstable calculation. Those nist began with quest for an alternate algorithm to displace those DES, the place the Rijndael cio might have been chose Likewise the new Advanced encryption standard (AES).

| I <sub>00</sub> | I <sub>01</sub> | I <sub>02</sub> | I <sub>03</sub> |     | <b>S</b> <sub>00</sub> | <b>S</b> <sub>01</sub> | S <sub>02</sub>  | \$ <sub>03</sub> |              | 000                    | 001                    | 002             | 003 |

|-----------------|-----------------|-----------------|-----------------|-----|------------------------|------------------------|------------------|------------------|--------------|------------------------|------------------------|-----------------|-----|

| I <sub>10</sub> | l <sub>ii</sub> | I <sub>12</sub> | $I_{13}$        |     | <b>S</b> <sub>10</sub> | \$ <sub>11</sub>       | \$ <sub>12</sub> | \$ <sub>13</sub> |              | <b>0</b> <sub>10</sub> | <b>0</b> <sub>11</sub> | 0 <sub>12</sub> | 013 |

| I <sub>20</sub> | l <sub>21</sub> | I <sub>22</sub> | l <sub>23</sub> | -   | <b>S</b> <sub>20</sub> | \$ <sub>21</sub>       | \$ <sub>22</sub> | \$ <sub>23</sub> | -            | 020                    | 021                    | 022             | 023 |

| I <sub>30</sub> | l <sub>31</sub> | I <sub>32</sub> | I <sub>33</sub> |     | S <sub>30</sub>        | S <sub>31</sub>        | \$ <sub>32</sub> | S <sub>33</sub>  |              | 0 <sub>30</sub>        | 031                    | 032             | 033 |

|                 | Input           | Array           |                 | - · | State Array            |                        |                  |                  | Output Array |                        |                        |                 |     |

## The Advanced Encryption Standard (AES):

Cryptography will be a standout amongst the the vast majority imperative topics identified with system security Furthermore transmission today. It assumes a paramount part in innovation Furthermore includes an incredible arrangement about foundation information from claiming PC science and math. Advanced Encryption Standard (AES) was self deployable and schema less framework where hubs are MANETs [2] are not dependent on the altered framework the place each center dives regarding Likewise a partly switch. The transmission of majority of the data alternately we can say that administering is completed through dissimilar controlling assemblies. It may be the continuous progressive field Furthermore is receiving amazing consideration since from utilizing self configuration and self upkeep, yet security may be that essential issue which ought to will make held under possibility with shield the correspondence starting with the debilitating condition. Those introduce status of a center ought to will make communicated should its neighbors When those hotspot center necessities will talk with those destination center. Since the current guiding information isn't referred to with separate hubs as shown in figure 1.

The perfect for this standard might have been to displace that old open key algorithm, information encryption standard (DES). Will would this, Rijndael might have been picked Similarly as the AES algorithm, which might have been outlined Eventually Tom's perusing Joan Daemen What's more Vincent Rijmen [1, 2]. An symmetric square cio with a 128-bit piece span may be those prerequisite for AES. Hence, both the collector What's more sender utilization one absolute magic should scramble or to unscramble those data. However, an iterated piece cio is outlined utilizing the Rijndael algorithm, which employments 128, 160, 192, 224 alternately 256 odds for its square sizes Furthermore magic lengths. Therefore, the additional recompense is not included done AES.

Those AES as stated by [1] need a consistent square size about 128 odds (16 bytes) with 3 diverse key sizes about 128 bits, 192 odds Furthermore 256 bits, the place 10, 12 and 14 encryption rounds will make connected to each way size, individually. Throughout the encryption Furthermore unscrambling courses the 16 bytes from claiming information will manifestation a variably (4\*4) show called those state exhibit. Throughout that encryption process, the state show comprises at first of the information data, this exhibit will keep evolving until arriving at the last enciphered information. In the unscrambling methodology the state exhibit will begin Toward the enciphered information and will keep evolving until retrieving those first information.

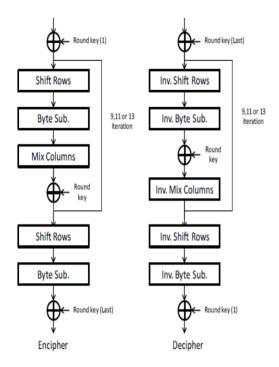

Every encryption round need 4 principle steps, movement Rows, byte substitution utilizing those substitution box (S-BOX), blend Columns, Furthermore include round way. The unscrambling transform comprises of the opposite steps, the place every unscrambling round comprises of: opposite movement Rows, byte substitution utilizing opposite S-BOX,

include round magic What's more opposite blend Columns. The individuals round keys

Published By:

& Sciences Publication

388

will a chance to be made using an unit known as the enter development unit. This unit will settle on generating 176,208 alternately 240 bytes of round keys relying upon the compass of the used key, additional focuses In those path development unit will aggravate elucidated after the fact in this segment. Fig. 3 demonstrates the AES encryption also unscrambling methods.

## **Future Scope**

The exploration works accomplished in this proposition are behind our inspiration to display the accompanying proposals for future research examinations in the equipment structure for the AES calculation and other conceivable cryptography calculations.

1. Those I-BOX method which might have been exhibited Might a chance to be received clinched alongside outline of the AES with 192 and 256 odds way sizes.

2. High pace widespread AES Processor that meets expectations with respect to at way sizes Might make executed Eventually Tom's perusing getting profit starting with those box strategy utilizing An circle unrolled framework.

3. Future AES outlines for 8-bits information way Might a chance to be planned In light of the S-BOX imparting and the pipelining systems introduced On Section 4.

4. Other cryptography calculations could profit from those plans from claiming blending Also relocating techniques, particularly over circle unrolled frameworks.

# V. Conclusion

In the principal engineering another structure for fast circle unrolled sub-pipelined AES scrambled was displayed. This structure misused from the rehashed errands On every period of the mixed should fulfill advantages joining What's more offering. In this encoded the mix segments step will be moved What's more every last one of round keys would gotten in the isomorphic mapping. By applying these alterations an viable meeting between those inverse isomorphic mapping, those relative progress duplication, and the isomorphic mapping to those accompanying encryption stage may be refined. This joining enabled the use with have bring down zone with shorter path length, which license higher FPGA (Throughput/Area) proficiency differentiating for secret word circis siliquastrum unrolled structures.

In the second building another structure to 32-bits majority of the data best approach AES encryptor/decryptor might have been presented. In this arrangement inner part pipelining to the composite field S-BOX might have been associated. This pipelining allowed parallel get ready to those state show segments Despite S-BOX offering the middle of those key round unit and the enter improvement unit. Additionally, this structure used on the fly agdistis for every one round keys which forestalls using enormous domain will store 74 every last one of keys Despite dropping the extra postponement advancing around done pre-figuring Also limit to all round keys. This building need finished higher FPGA (Throughput/Area) profit contrasted with secret word 32-bit AES structures.

# References

- [1] Advanced Encryption Standard (AES), FIPS PUB 197, Nov. 26, 2001, Federal Information Processing Standards publication 197. Federal Information Processing Standards Publication 197.

- [2] X. Zhang and K. K Parhi, "High-speed VLSI Architecture for the AES Algorithm", IEEE Transactions on Very Large Scale Integration (VLSI) System., vol.12, no. 9, pp. 957-967, Sep. 2004.

- [3] Jose M. Granado-Criado, Miguel A.Vega-Rodriguez, Juan M. Sanchez-Perez and Juan A. G'omez-Pulido, "A new methodology to implement the AES algorithm using partial and dynamic reconfiguration", Integration, the VLSI Journal 43 (2010) 72-80.

- [4] Vincent Rijmen, "Efficient Implementation of the Rijndael S-box". Katholieke Universiteit Leuven, Dept. ESAT. Belgium".

- Jarvinen, K., Tommiska, M., and Skytta, "A Fully [5] Pipelined Memoryless 17.8 Gbps AES-128 Encryptor". Proc. ACM/SIGDA 11th ACM Int. Symposium on Field-Programmable Gate Arrays, FPGA 2003, Monterey, CA, USA, February 2003, pp. 207-215.

[6] Kimmo Järvinen, Matti Tommiska and Jorma Skyttä, "Comparative Survey of High Performance

Cryptographic Algorithm Implementations on FPGAs", IEE

Published By:

& Sciences Publication

Proceedings - Information Security, vol. 152, no. 1, Oct. 2005, pp. 3-12.

- [7] C. Paar, "Efficient VLSI architecture for bit-parallel computations in Galois field," Ph.D. dissertation, Institute for Experimental Mathematics, University of Essen, Essen, Germany, 1994.

- [8] A. Satoh, S. Morioka, K. Takano, and S. Munetoh, "A compact Rijndael hardware architecture with S-Box optimization," in Proc. ASIACRYPT 2001, Gold Coast, Australia, Dec. 2000, pp. 239-254.

- [9] A. Rudra, P.K. Dubey, C.S. Jutla, V. Kumar, J.R. Rao, and P. Rohatgi. "Efficient Rijndael Encryption Implementation with Composite Field Arithmetic", Workshop on Cryptographic Hardware and Embedded Systems (CHES2001), pages 175-188, May 2001.

- [10] Edwin NC Mui, "Practical Implementation of Rijndael S-Box Using Combinational Logic", Texco Enterprise Ptd. [Online]. Available: Ltd. http://www.xess.com/projects/ Rijndael\_SBox.pdf.

- [11] Joseph Zambreno, David Nguyen, and Alok Choudhary, "Exploring Area/Delay Tradeoffs in an AES FPGA Implementation", Department of Electrical and Computer Engineering, Northwestern University.

- [12] [Hodjat A. and Verbauwhede. I, "A 21.54 Gbits/s fully pipelined AES processor on FPGA". Proc.12th Annual IEEE Symposium. Field Programmable Custom Computing Machines, FCCM"04, Napa, CA, USA, April 2004, pp.308-309.

- [13] I. Hammad, K. El-Sankary, and E. El-Masry, "High Speed AES Encryptor with Efficient Merging Techniques," IEEE Embedded Systems letters, vol. 2, no. 3, pp. 67-71, Sept. 2010.

- [14] K. Gaj and P. Chodowiec. Very Compact FPGA Implementation of the AES Algorithm. In the proceedings of CHES 2003, Lecture Notes in Computer Science, vol 2779, pp. 319-333, Springer-Verlag.

- [15] G. Rouvroy, F.-X. Standaert, J.-J. Quisquater and J.-D. Legat, "Compact and efficient encryption/decryption module for FPGA implementation of the AES Rijndael very well suited for small embedded applications", Information Technology Coding and Computing 2004.

Published By:

& Sciences Publication