# Design of Parallel Self-Timed Adder with Recursive Research

# Swapna Thouti

ABSTRACT---This speedy suggests a parallel single-rail selfcoordinated snake. It relies upon on a algorithmic description for showing multibit twofold growth. The hobby is parallel for the ones bits that require now not trouble with any supply chain unfold, in the course of this way, the arrange achieves power execution over irregular quantity situations and not using a excellent dashing hardware or appearance-ahead sample. A proper all of the way right down to earth usage is given on a give up discovery unit. The execution is fashionable and doesn't have any pragmatic rules of excessive fanouts. A high fan-in door is wanted however nonetheless it really is ineluctable for kinky reason and is overseen by way of manner of associating the transistors in parallel. Recreations were finished creating use of AN commercial enterprise commonplace tool cabinet that ensure the common sense and prevalence of the projectedmethod over current nonconcurrent adders

#### 1. INTRODUCTION

Parallel increase is that absolutely the maximum excellent pastime that a processor plays, the larger a place of the adders had been supposed for synchronous circuits yet the that there's fact stable enthusiasm clockless/nonconcurrent processors/circuits. Nonconcurrent circuits don't count on any quantisation of some time. therefore, they maintain terrific capability for explanation shape as they're loose from some problems of regular (synchronous) circuits. On a primary stage, rationalization circulate in kinky circuits is limited with the help of a solicitation confirmation handshake convention to create up a pipeline without tickers, specific handshake obstructs for small elements, as an example, bit adders, are high-priced. at some stage in this way, it is certain sufficient and expeditiously overseen exploitation double rail convey proliferation in adders. A legitimate double rail convey yield further gives confirmation from a solitary piece snake sq.. therefore, nonconcurring adders are every supported on complete double rail coding all subjects thought-about (all the bigger formally utilising invalid show that utilizations emblematically correct purpose as important mathematician purpose) or pipelined hobby exploitation single-rail facts encoding and double rail deliver portrayal for affirmations. while these develops switch electricity to circuit plans, they similarly acquaint massive overhead with the ordinary case execution blessings of nonconcurrent adders. on those strains, a frequently effective optionally accessible technique is well worth of notion with the intention to trot out these problems. This elliptic affords a nonconcurrent parallel self-deliberate snake (PASTA) utilizing the calculation first of all projected. The set up of meals is stateof-the-art and uses zero.five of-adders (HAs) aboard multiplexers requiring negligible interconnections. at some stage in this manner, it is manner suitable for VLSI execution.

Free supply chain squares. The execution on this brief is one in every of a kind because it makes use of grievance thru XOR motive doors to include a solitary rail cyclic nonconcurrent serial snake. Cyclic circuits could also be additional plus effective than their non-cyclic partners. Then once more, wave pipelining (or excellent price pipelining) might be a way that will follow pipelined contributions earlier than the yields are balanced out. The projected circuit oversees programmed single-rail pipelining of the supply information sources remoted through engendering and mechanical phenomenon postponements of the doorways inside the circuit way. on those strains, it is sufficiently a solitary rail wave-pipelined approach and virtually specific on the subject of normal pipelined adders creating use of double rail coding to even as now not a doubt talk over with the pipelining of deliver signs.

## 2. HISTORY

There are a heap plans of double adders and that we middle right here round nonconcurrent self-coordinated adders. Self-deliberate alludes to purpose circuits that rely on moreover to skilled temporal order presumptions for the proper hobby.

ig. 1. General block diagram of PASTA.

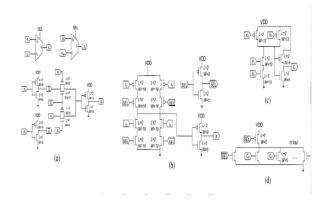

Fig. 2. State diagrams for PASTA. (a) Initial phase. (b) Iterative phase.

Self-coordinated adders will in all likelihood run faster discovered the center fee of for dynamic records, as early cease result police research will maintain a strategic distance from the necessity for the utmost demoralized state of affairs prepackaged defer component of synchronous circuits. they'll be as well delegated pursues.

Revised Manuscript Received on August 19, 2019.

**Dr. Swapna Thouti,** Professor, ECE department, MallaReddy Engineering College (A)

## Design of Parallel Self-Timed Adder with Recursive Research

A. Pipelined Adders mistreatment single-Rail records secret writing ThenonconcurrentReq/Ack acknowledgement is used to empower the snake restrict at the same time as to set up the event of carry alerts. in the existence-sized majority of the times, a double rail deliver show is carried out for inside bitwise circulation of convey yields. these double rail sign will go to in in addition of 2 rationalization esteems (invalid, 0, 1), and in the course of this manner is used to provide bit-degree affirmation once a small amount pastime is finished. remaining consummation is detected while all piece Ack sign are gotten (excessive). The bring give up police research snake can be a case of a pipelined snake, that makes use of complete snake (FA) helpful squares adjusted fordouble rail carry. Then all all over again, a theoretical consummation snake is planned in. It makes use of intended direct quit reason and early accomplishment to pick out out the proper consummation response from numerous mounted defer lines. Be that due to the fact it could, the in advance forestall motive execution is luxurious owing to excessive fan-in conditions.

B. Defer Insensitive Adders mistreatment twin-Rail secret writing delay brutal (DI) adders are nonconcurrent adders that claim packaging requirements or DI sports activities. Thusly, they are ready to correctly paintings in distance of confined but obscure entree and twine delays. There are numerous variations of DI adders, as an example, DI swell supply snake (DIRCA) and DI deliver look-earlier snake (DICLA). DI adders make use of double rail secret writing and are common to make unpredictability. notwithstanding the very reality that double rail mystery writing copies the twine varied nature, they may even currently be used to make circuits in reality as powerful as that of the unmarriedrail variations using dynamic cause or nMOS merely systems. A version 40 transistors for each piece dicot genus snake is displayed in at a comparable time because the regular CMOS RCA utilizes twenty eight transistors. Like CLA, the DICLA characterizes bring proliferate, produce, and slaughter conditions referring to double rail mystery writing. They don't accomplice the carry flag during a series but as another sort out them in a stylish tree. during this way, they're equipped to conceivably art work quicker while there's long deliver chain. A moreover improvement is given from the belief that double rail secret writing cause will earnings by way of mistreatment subsiding of both the zero or one way. Double rail motive would love not think about that the two techniques may be assessed. on those traces, it's so much possible to any accelerate the deliver appearance-in advance hardware to ship bring create/deliver slaughter signal to any level in the tree. this will be mentioned and alluded as DICLA with velocity hardware (DICLASP).

Three fashion OF mealson this phase, the layout and speculation inside the returned of food is displayed. The snake to start out with recognizes 2 data operands to hold out halfadditions for each piece. consequently, it emphasizes using in advance created carry and totals to carry out half of-will increase in addition than as soon as until all deliver bits are devoured and settled at zero level. A. fashion of food the general engineering of the snake . The resolution contribution for two-input multiplexers compares to the Req acknowledgement sign and may well be a solitary zero to 1 improvement importance via SEL. it will principally opt for

the actual operands throughout SEL = 0 and will change to grievance/deliver approaches in which for ensuing cycles creating use of SEL = one. The input way from the HAs empowers the numerous emphasess to keep until the fruition once all supply signal are given 0 characteristics. B. nation Diagrams, 2 country outlines are drawn for the underlying degree and therefore the unvarying amount of the deliberate engineering, every nation is spoken to with the assist of (Ci+1 Si) integrate wherein i+1, Si talk to try to to and entire characteristics, separately, from the ith bit snake sq., for the duration of the underlying degree, the circuit merely options as a combinatory angular distance going for walks in predominant mode. it is obvious that owing to the employment of HAs in place of FAs, country (11) can not show up. for the duration of the unvarying stage (SEL = 1), the enter way via electronic device square is initiated. The bring adjustments (Ci ) are permitted the equal wide selection of instances for positive to finish the rule of thumb. From the which means of primary mode circuits, the winning arrange can't be notion of as a primary mode circuit due to the fact the info yields can revel in many changes previous to returning the ultimate yield. it's one component however a Muller circuit working out of doors the important mode every as within, many modifications can occur.

#### 3. IMPLEMENTATION& RESULTS

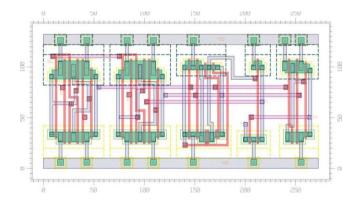

A CMOS utilization for the algorithmic circuit. For multiplexers AND entrees we've got implemented TSMC library utilization at a comparable time as for the XOR door we have used he faster 10 junction transistor execution counting on transmission entryway XOR to coordinate the postponement with AND doors, the top end result discovery is discredited to build up a functioning immoderate finishing sign (time period), this desires a large fan-in n-input NOR entree, for the duration of this indicates, AN elective steady conceivable pseudo-nMOS percentage male erecticle dysfunction configuration is implemented, successive set up, making use of the pseudo-nMOS set up, the finishing unit remains off from the high fan-in problem as each one of the associations are parallel. The pMOS junction transistor associated with VDD of

This percentage disfunction configuration is going regarding as a heap check in, transferral extra or much less static modern channel once some of the nMOS transistors are on on the same time. withal the Ci s, the negative of SEL sign is moreover covered for the term signal to assure that the finishing can not be coincidently have become on for the duration of the underlying self-control length of the real data assets. It similarly averts the pMOS draw up semiconductor unit from being continuously on. hence, static contemporary may additionally motion for the span of the specific calculation. VLSI format has likewise been dead for a modern cell situation utilising 2 metal layers. the look possesses 270  $\lambda$  × one hundred thirty  $\lambda$  for one-piece transferral regarding 1.123 Mλ2 region for 32-piece. The draw down semiconductor gadgets of the fruits neck of the woods reason are enclosed into the single-piece layout (the T terminal) even as the draw up transistor is what is greater set for the whole 32-piece snake. it is sort of twofold the territory wanted for RCA and is implausibly but the massive majority of the area powerful prefix tree serpent, i.E., Brent-Kung snake (BKA).

## 4. SIMULATION OUTCOMES

On this neck of the woods, we have a tendency to gift enterprise outcomes for numerous adders exploitation Mentor images Eldo SPICE edition seven.4\_1.1, going for walks on 64-piece UNIX degree. For usage of various adders, we've got utilised in fashion library executions of the critical doors. The custom adders, as an example, DIRCA/DICLASP are lifeless counting on their quality structures. before everything, we have a tendency to expose but the winning shape of alimentary paste will viably carry out twofold expansion for numerous temperatures and manner corners to approve the electricity to a decrease region accumulating and operational types. In Fig. four, the making plans graphs for plenty sincerely horrible and ordinary times examination to finest and normal duration deliver chain adjoin arbitrary records esteems are featured. The deliver spreads thru modern day piece adders kind of a heartbeat as apparent. The excellent-case almost about least length convey chain (not seemed right here) will no longer embody any bring proliferation, and consequently acquires entirely a solitary piece serpent postpone previous growing the term sign. the most hopeless scenario consists of highquality supply proliferation fell deferral thanks to the convey chain duration of complete thirty piece. The autonomy of convey chains is obvious from the regular 8and C26 are gave the impression to trigger at actually the

identical time. This circuit works because it must be for all procedure corners. For SF corner instances, one Cout growing edge a quick powerful threat. This hasno pursue on influences at durations the circuit nor are mistakes incited through way of the SF extremely good nook case. The defer exhibitions of assorted adders, we've got utilised a thousand continually sent bizarre operands to speak to the everyday case at consistent time as excellent case, most hopeless state of affairs relate to precise experiments talking to zero, 32piece carry engendering chains in man or woman. The deferral for combinable adders is anticipated at seventieth progress purpose for the result bit that encounters the most extreme postponement. For self-coordinated adders, it is anticipated through exploitation the deferral amongst SEL and term signs, as diagrammatic The 32-piece full CLA isn't always all of the manner down to earth thanks to the requirement of excessive fan-in, and for that reason a numerous leveled square CLA (B-CLAis useless for test. The combinable adders, SPICE temporal order chart for alimentary paste usage making use of TSMC 0.35 µm approach. The Cout and C12 for many hopeless situation and everyday case, one by one, are regarded for changed conditions at some stage in which TT, SF, and FS speaks to run of the mill common, slow-quick, and brief moderate nMOS-pMOS things in those figures. (a) Worst-case deliver proliferation while at the side of operands (FFFF FFFF)sixteen and (0000 0001)16. (b) common-case deliver engendering while at the identical time inclusive of arbitrary operands of (3F05 0FC0)16 and (0130 0041)sixteen.

For instance, RCA/B-CLA/BKA/Kogge-Stone serpent (KSA)/Sklansky's restrictive completeness snake (SCSA) will artwork for the most hopeless scenario defer as they want no end result sleuthing tool. on those lines, these effects deliver an express higher positive of the exhibition improvement that may be finished utilising those adders due to the vital unit and growing use of some fairly consummation sleuthing machine. in the maximum hopeless scenario, KSA plays splendid as they (alongwith SCSA) have the insignificant tree-profundity [10]. Then all all over again, alimentary paste performs exceptional amongst oneself planned adders. alimentary paste execution is same with the pleasant case exhibitions of standard adders. with achievement, it changes somewhere inside the vary of 1 and pretty one instances that of the fantabulous snake exhibitions.

It's miles even incontestable to be the quickest for TSMC zero.35 µm technique. for regular instances, alimentary paste execution remains inside pretty one times thereto of the same old conventional case exhibitions at regular time as for the most hopeless state of affairs, it acts much like the RCA. notice that, alimentary paste finishes the principle pressure of the algorithmic particularisation as soon as "SEL = zero." as a consequence, the only case postponement speaks to the defer had to produce the time period signal clearly and of the request for picoseconds.comparable overhead is likewise located in double rail clarification circuits wherein they want to be reset to the invalid nation

preceding any calculation. The dynamic/nMOS simply plans need a precharge degree to be finished in the course of this era mediate. these overheads are excluded during this correlation.

#### 5. CONCLUSION

This rapid shows an awesome utilization of a alimentary paste.to start with, the theoretical institution for a solitary rail wave-pipelined serpent is made up. in the course of this manner, the structural set up and CMOS utilization are delivered. The set up accomplishes a basic n-bit serpent this is often territory and interconnection-clever the photo of the smallest quantity hard snake basically the RCA. besides, the circuit works in a completely parallel way for freelance deliver chains, and because of this accomplishes exponent ordinary time execution over odd records esteems. The completing identification unit for the projected serpent is moreover attainable and powerful. reproduction results are utilised to affirm the upsides of the projected approach.

## REFERENCES

- D. Geer, "Is it time for clockless chips? [Asynchronous processor chips]," IEEE Comput., vol. 38, no. three, pp. 18– 19, Mar. 2005.

- 2. J. Sparsø and S. Furber, ideas of Asynchronous Circuit style. Boston, MA, united states: Kluwer academic, 2001.

- 3. P. Choudhury, S. Sahoo, and M. Chakraborty, "usage of important maths tasks exploitation mobile appliance," in Proc. ICIT, 2008, pp. seventy nine–eighty.

- M. Z. Rahman and L. Kleeman, "A defer coordinated method for the set up of nonconcurrent serial circuits," Dept. Comput. Syst.Technol., Univ. Malaya, Malaysian capital, Malaysia, Tech. Rep. 05042013, 2013.

- M. D. Riedel, "Cyclic combinable circuits," Ph.D. Thesis, Dept. Comput. Sci., Golden state present. Technol., Pasadena, CA, usa,may additionally 2004.

- R. F. Tinder, Asynchronous successive gadget style and analysis: A complete improvement of the appearance and analysis of Clock-independent state Machines and structures. San Mateo, CA, u.s.a.: Morgan, 2009.

- W. Liu, C. T. Dim, D. Fan, and W. J. Farlow, "A 250-MHz wave pipelined serpent in 2-μm CMOS," IEEE J. strong country Circuits, vol. 29,no. 9, pp. 1117–1128, Sep. 1994.

- 8. F.- C. Cheng, S. H. Unger, and M. Theobald, "Self-coordinated rrylookaheadadders," IEEE Trans. Comput., vol. 40 9, no. 7, pp. 659–672, Jul. 2000.

- S. Nowick, "Plan of a low-inaction quirky snake utilising theoretical accomplishment," IEE Proc. Comput. superior technical college., vol. 143, no. five, pp. 301–307, Sep. 1996.

- N. Weste and D. Harris, CMOS VLSI design: A Circuits and systems angle. Perusing, MA, u.s.a.: Addison-Wesley, 2005.

- C. Cornelius, S. Koppe, and D. Timmermann, "Dynamic circuit techniquesin profound submicron upgrades: Domino purpose reevaluated," in Proc. IEEE ICICDT, Feb. 2006, pp. 1–four.

- M. Anis, S. part, M. Allam, and M. Elmasry, "effect of innovation scaling on CMOS cause styles," IEEE Trans. CircuitsSyst., Analog virtual sign approach., vol. forty nine, no. eight, pp. 577–588 August. 2002.