# Strained SI/SIGE/SI Nano-Channel Hoi Mosfet

# Lalthanpuii Khiangte, Rudra Sankar Dhar

Abstract— Strained Si technology has headed in the development of single or dual channel strained silicon MOSFETs devices. Comprehending the need of advancement in recent technologies with miniaturized features, developing a novel MOSFET on ultrathin double strained Si with strained SiGe sandwiched in between and forming a tri-channel MOSFET has been the crux of this present research. Incorporation of quantum carrier confinement effect on the ultrathin dual strained Si layers in the channel has been implemented to counterbalance the threshold voltage roll-off induced by the strained layers. A comparison of the conventional strained silicon on relaxed silicon-germanium with double strained silicon channel MOSFET has been perceived leading to eloquent drain current enhancement of ~49% with a small reduction in the threshold voltage caused by the additional bottom strained Si layer. Further, 100nm and 50nm channel length have been compared and a superior device characteristic for the reduced device dimension is attained as the prominence of velocity overshoot is more in short channel device approaching to quasi-ballistic transport in the channel region.

Keywords: double strained Si; SOI; strained SiGe velocity overshoot; threshold voltage; MOSFET; HOI; transconductance  $(gm_{max})$ ; quantum confinement; DIBL.

# I. INTRODUCTION

A considerable amount of attention has been given to strained technology in the last decade for its ability to enhance carrier mobility and drive current for MOSFETs [1]. Literature suggested beneficial stress techniques for n-MOSFETs such as: (a) globally strained substrate, (b) stress memorization technique, and (c) tensile overlayer [2]-[9] and various structures of strained device with Si/SiGe material developed as: (1) Strained silicon (s-Si) on relaxed SiGe, (2) s-Si/strained SiGe (s-SiGe) dual channel layer, (3) direct s-Si on insulator and (4) Heterostructure on insulator (HOI) or on bulk [10]. Strain techniques does not compromise long term reliability aspects and has only a marginal impact on the quality of gate oxide has been validated [11]. But, a major concern with strained Si is the reduction of threshold voltage (Vth) which occurs due to decrease in band gap with increase in strain. On this account, detailed investigations suggested that for s-Si layer thickness of ~3nm, the benefits of using higher Ge mole fraction can be retained while maintaining the V<sub>th</sub> reasonably large [12][13]. Hence, Si<sub>1-x</sub>Ge<sub>x</sub> forms a better option for the dual channel MOSFETs.

This paper is focused on the development of a novel

Revised Manuscript Received on July 10, 2019.

Lalthanpuii Khiangte, Department of Electronics and Communication Engineering, National Institute of Technology Mizoram, Aizawl, India. Rudra Sankar Dhar, Department of Electronics and Communication Engineering, National Institute of Technology, Mizoram, Aizawl, India. (email: <a href="mailto:rdhar@uwaterloo.ca">rdhar@uwaterloo.ca</a>)

double strained Si channel heterostructure on insulator MOSFET featuring an additional bottom strained Si layer in the channel region which sandwiches  $\mathrm{Si}_{1\text{-x}}\mathrm{Ge}_x$  between making a distinguished structure than the conventional single strained Si SOI MOSFET, resulting in an enhanced drain current. An in-depth study and analysis of double strained Si channel MOSFET in nano-regime has been performed, where drain current, and transconductance enhancements are compared for 100nm and 50nm channel length devices. Physics of velocity overshoot effect has also been analyzed for 50nm channel length HOI MOSFET, which elucidated carriers approaching the quasi-ballistic transport.

### II. DEVICE STRUCTURE

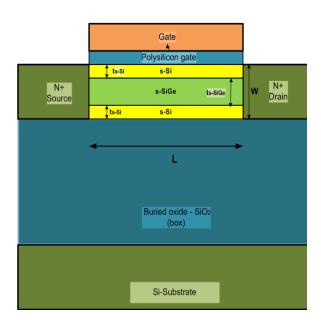

Incubating the benefits of SOI MOSFET with the ability to enhance carrier mobility by strained Si technology[15]-[20], doubly due to the additional s-Si layer discriminates this novel device structure and its superior characteristics to the conventional device (single s-Si MOSFET). Fig. exemplifies the two s-Si layers which are introduced in the channel region for the first time, sandwiching the SiGe layer, hence crafting a strained SiGe layer. This novel device structure thus consists of a tri-layered channel forming the heterostructure-on-insulator (HOI) MOSFET. To fabricate heterostructure on insulator MOSFET, strained Si, strained Si<sub>1-x</sub>Ge<sub>x</sub>, each layer is grown respectively on the relaxed Si<sub>1-v</sub>Ge<sub>v</sub> layer and transferred to the insulator preserving the original strain state. Ultrathin strained Si surface layer of ~2nm thick has been employed so that holes are not entirely confined at the surface, resulting in reduced influence of higher Ge content on the s-Si layer with this advancement these two s-Si layers formed the quantum well for carrier confinement. With parameters listed in Table 1, two devices have been designed: Device A -100nm, and Device B-50nm gate length double s-Si channel along with the conventional device-single s-Si specified as in [12].

Fig1.Double s-Si with s-SiGe HOI MOSFET

**Table.1 Device Parameters**

| = = = = = = = = = = = = = = = = = = = =    |                                   |

|--------------------------------------------|-----------------------------------|

| Parameters                                 | Values                            |

| Channel Length ( L)                        | 50nm, 100 nm                      |

| Ge mole fraction                           | 0.4                               |

| s-Si layer thickness ( t <sub>s-Si</sub> ) | 2 nm                              |

| Gate Oxide thickness                       | 2 nm                              |

| Source/Drain doping (N <sub>D</sub> )      | 10 <sup>19</sup> cm <sup>-3</sup> |

| channel doping ( N <sub>A</sub> )          | 10 <sup>16</sup> cm <sup>-3</sup> |

| Drain bias (V <sub>DS</sub> )              | 50mV                              |

# III. RESULTS AND DISCUSSION

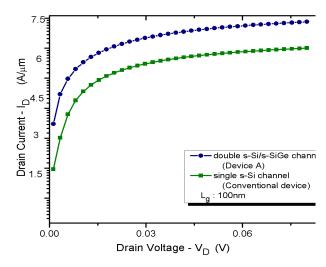

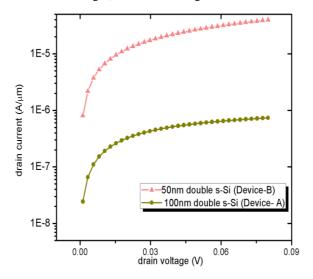

Using device parameters tabulated in Table I, simulation of the device structure shown in Fig.1 by 2D SYNOPSIS Sentaurus TCAD tool [22], [23], incorporating multi-valley model for both band structure and electron mobility [23] for strained induced band gap reduction and change in electron mobility respectively. Quantization effects were accounted by the 1D Schrodinger model [23] in which the Schrodinger and Poisson's equations were solved simultaneously on the non-local-mesh created between the s-Si and the dielectric interfaces. Drain current enhancement of ~49% was observed for Device A at 50mV drain-source voltage as shown in Fig. 2. over the conventional device which is essentially due additional strained Si layers in the channel region, favorable for the increment of electrons with enhanced mobility

$Fig. 2. \ I_{D.}V_{D} \ characteristics \ depicting \ 49\%$  enhancement in drive current for 100nm channel length HOI MOSFET over 100nm channel length Conventional devices

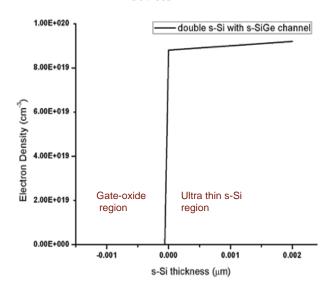

Fig.3. Carriers confinement in the ultrathin s-Si layer of Device A (100nm double s-Si HOI MOSFET)

Trace of carrier confinement in the s-Si layer was obtained as illustrated in Fig. 3 due to the quantization effect. Thus, energy band gap increased balancing the threshold voltage roll-off due to strained layers. A clear insight of velocity overshoot [24] being more prominent in reduced channel length is depicted in Fig. 4.

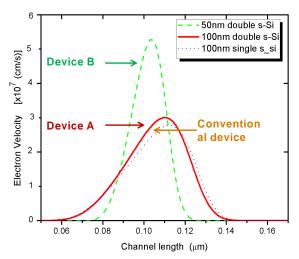

Fig.4. Electron velocity variation along the channel length compared between Device-A, Device-B and single s-Si channel MOSFETs.

With the reduction of channel length and increased in lateral electric field in Device-B the velocity overshoot condition is acquired i.e. non-equivalence of momentum relaxation time and energy relaxation time, result in low scattering and carriers do not have time to heat up. The electron velocity becomes greater than the saturation velocity. Hence, carrier transport approaches quasi-ballistic in nature result in drain current enhancement ( $\Delta I_D = (I_D^{50 \text{nm}})/I_D^{100 \text{nm}}$  double s-Si) of ~41.3% for Device-B (50nm channel length) in comparison to Device-A (100nm channel length) as shown in Fig. 5.

$Fig. 5. \ I_{D.}V_{D} \ characteristics \ depicting \ 41.3\%$  enhancement in drive current for 50nm channel length over 100nm channel length in HOI MOSFET devices

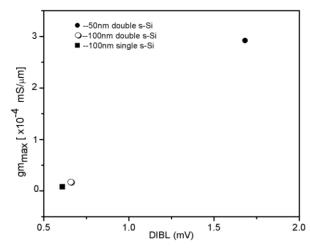

Distinct view about the short channel effects are exemplified by Fig.6 in which threshold voltage and DIBL and transconductance  $(gm_{max})$  variation as a function DIBL has been obtained for each of the three devices (Device A, Device-B and Conventional Device). A 25.25% threshold voltage roll has been attained in 50nm channel length in comparison to 100nm channel length for double s-Si MOSFET with a higher DIBL. A remarkable increase in transconductance is achieved featuring velocity overshoot

[25], which is a tradeoff between transconductance and DIBL observed due to the short channel effects in the HOI MOSFET devices.

Fig.6. Transconductance (gm<sub>max</sub>) as a function of DIBL for Device-A, Device-B and Conventional.

# IV. CONCLUSION

Double strained Si layers in the channel region of Heterostructure on Insulator MOSFET have been developed and analyzed. With intrusion of the additional strained Si layer in the channel region an eloquent drain current enhancement of 49.3% has been obtained for 100nm channel length device in comparison to the single s-Si SOI MOSFET device. Velocity overshoot has been perceived in the sub 100nm device (Device B) resulting in improved drive current along with high gm<sub>max</sub> attained in the 50nm short channel length device. Increased transconductance in this short channel-MOSFET was observed due to the effect of velocity overshoot experiencing ballistic carrier transport within the channel of the HOI MOSFET.

### V. ACKNOWLEDGMENT

The authors thank NIT Mizoram for providing blissful facilities and workplace, special gratitude to all the members of Department of Electronics & Communication Engineering for their excellent support throughout the work and in particular to Special Manpower Development Project (SMDP-C2SD) for providing workstation to carry out this work.

## REFERENCES

- M. Reiche et al., "Strained Silicon Devices Solid State Phenomena," Solid State Phenom., vol. 156-158, pp. 61-68, 2010. doi: 10.4028/www.scientific.net/SSP.156-158.61

- K. Rim et al., "Fabrication and mobility characteristics of ultra-thin strained Si directly on insulator (SSDOI) MOSFETs," IEDM Tech. Dig.,vol. 49, pp. 49-52, 2003. doi: 10.1109/ IEDM.2003. 1269163

- A. Wei et al., "Integration challenges for advanced process strained CMOS on biaxially- strained SOI (SSOI)

- substrates," ECS Trans., vol. 6, No. 1, pp. 15-22, 2007.

- C.Auth, A. Cappellani, J.S Chun et al., "45 nm high-k + metal gate strain-enhanced transistors," in Symp. Tech. Dig., 2008, pp.128-129, ISSN 2158-9682

- A. Shimzu et al., "Local mechanical-stress control (LMC): A new technique for CMOS-performance enhancement," in IEDM Tech. Dig., 2001, pp. 433-436.

- H. S. Yang et al., "Dual stress liner for high performance sub-45 nm gate length SOI CMOS manufacturing," in IEDM Tech. Dig., 2004, pp. 1075-1077.

- K. Otal et al., "Novel locally strained channel technique for high performance 55 nm CMOS," in IEDM Tech. Dig., 2002, pp. 27-30

- 8. C.H.Chen et al., "Stress memorization technique (SMT) by selectively strained-nitride capping for sub-65 nm high performance strained Si device application," in Symp. VLSI Tech. Dig., 2004, pp. 56-57.

- S. Gannavaram, N. Pesovic and M. C. Ozturk,"Low temperature (<800°C) recessed junction selective silicon-germanium source/ drain technology for sub-70 nm CMOS," in IEDM Tech., Dig., 2000, pp. 437-440.

- D. A. Antoniadis, I. Aberg, C. Ni Chleirigh, O. M. Nayfeh, A. Khakifirooz, and J. L. Hoyt, "Continuous MOSFET performance increase with device scaling: The role of strain and channel material innovations," IBM J. RES. DEV. vol. 50, Issue 4/5, pp. 363-376, July 2006.

- C. Claeys, E. Simoen, S. Put, G. Giusi and F. Crupi, "Impact strain engineering on gate stack quality and reliability," Solid state electronics, vol. 52, Issue 8, pp. 115-1126, 2008.

- M. Jagadesh Kumar, Tarun Vir Singh, "Quantum Confinement Effect in Strained Silicon MOSFET," Int. J. Nanosci., vol. 7, No. 2, pp. 81-84, June 2008.

- Stefan Flachowsky et al., "Understanding strain-induced drive current enhancement in strained-silicon n-MOSFET and p-MOSFET," IEEE Trans. Electron Devices, vol.57, No.6, pp. 1343-1354, June 2010.

- Eugene A. Fitzgerald, Minjoo L. Lee, Christopher W. Leitz and Dimtri A. Antobiadis,"MOSFET channel engineering using strained Si, SiGe and Ge channels," MIT, Cambridge, 2003. [Online]. Available: http://hdl.handle.net/1721.1/3726

- K.Rim, J. Welser, J. L. Hoyt and J. F. Gibbons,"Enhanced hole mobilities in surface-channel strained Si p-MOSFETs," IEDM Tech. Dig., pp. 517-520, 1995. ISSN 0163-1918

- Pramod Kumar Tiwari, Gopi Krishna Saramekala, Sarvesh Dubey and Anand Kumar Mukkhopadhyay,"Analytical model for subthreshold current and subthreshold swing of short channel double material gate MOSFETs with strained-silicon channel on silicon-germanium substrates," J. Semicond., vol. 35, No. 10, Oct., 2014.

- Douglas J. Paul," Si/SiGe heterostructures: from material and physics to devices and circuits," Semicond. Sci. Technol., vol. 19, No. 10, pp. 75-108, 2004.

- Sarah H. Olsen et al.," High performance nMOSFETs using a novel strained Si/SiGe CMOS architecture," IEEE Trans. Electron Device, vol. 50, No. 9, pp. 1961-1969, Sept., 2003.

- S. H. Olsen, K. S. K. Kwa, L.S. Driscoll, S. Chattopadhyay and A.G. O'Neil," Design, fabrication and characterization of strained Si/SiGe MOS transistors," IEE Proc. Circuits Devices Syst., vol. 151, No. 5, Oct., 2004.

- Sarah H. Olsen et al., "Optimization of alloy composition for high performance strained-Si-SiGe n-channel MOSFET," IEEE Trans. Electron Devices, vol. 51, No. 7, pp. 1156-1162, July 2004.

- Sarah H. Olsen et al., "Study of single- and dual-channel designs for high performance strained-Si-SiGe n-MOSEFTs," IEEE Trans. Electron Devices, vol. 51, No. 7, pp. 1245-1253, July 2004.

- 22. Sentaurus Structure Editor User Guide, Synopsys, Mar., 2016

- 23. Sentaurus Device User Guide, Synopsys, Mar., 2016.

- Himanshu Batwani, Mayank Gaur and M. Jagadesh Kumar, "Analytical drain current model for nanoscale strained-Si/SiGe MOSFETs," COMPEL: The Int. Journal for Computation and Mathematics in Electrical and Electronic Eng., vol. 28, No. 2, 2009.

- Willander, M. Y. A. Yousif and O. Nur, "Nanostructure effects in Si-MOSFETs," 9<sup>th</sup> Int. Symp., St. Petersburg, *Russia*, June 2006.