# Low Energy Less Area Less Delay Fixed Point LMS Method for Adaptive Noise Cancellation Filter

# T Krishnarjuna Rao, M. Srinivasan, D. Lakshmaiah

Abstract: Present paper is about the high speed low complexity implementation derived by its architecture using least mean square (LMS) adaptive filtering. Here straight form LMS adaptive filter has almost the similar critical path as it is a reverse from of the counter path hoiver it has a fast coverage and also a loir register complication. Here critical path evaluation tells that no pipelining is necessary for implementation of straight form LMS adaptive filtering in most of the practical cases requires a realized extremely small adaptive delay and very high sampling rate. Here based on these finding LMS adaptive filtering is divided into 3 structural proposal designs. a) There is no adaption delay b) Only one adaption delay c) Only two adaption delay. Here first one includes least area and least energy per sample (EPS).

Keywords: least mean square (LMS), extremely

#### I. INTRODUCTION

Multiple constant multiplication (MCM) is generally known as multiplication of variables by a set of constants is very important in DSP (Digital signal processing) applications like digital finite impulse response (FIR), fast fourier transforms (FFT) and discrete cosine transforms (DCT). Here the main objective of this method is to reduce the adder depth (AD) that is the number of adder stages by computing a coefficient so the reduced pipelining adder graph (RPAG) is utilized to minimize the number of adders that keeps the number of shifts low and reduces the delay of FIR product filter, area and energy.

Hoiver, that usage of a multiplication operation done equipment will be vieid as will make exorbitant Likewise it involves critical range and need vast delay. Since the constants clinched alongside multiplications need aid decided a chance to be forehand by those DSP methods. Finite impulse response (FIR) filters are about incredible significance is more in digital signal processing (DSP) systems since their distinctiveness are in linear-phase and feed-forward usage make them exceptionally of service to fabricating stable high-octane filters.

Despite both architectures have comparable multifaceted nature done hardware; the transposed type will be by favored on account from claiming its higher execution Also energy effectiveness.

#### Revised Manuscript Received on March 5, 2020.

T Krishnarjuna Rao, Research Scholar, Dept. of ECE, SSSUTMS Schore, Bhopal, Madhyapradesh

**Dr.M.Srinivasan**, Associate Professor, Dept. of ECE, SSSUTMS Schore, Bhopal, Madhyapradesh.

**Dr. D. Lakshmaiah**, Associate Professor, Dept. of ECE in SRI INDU College of Engineering, hyd, Telangana

The multiplier piece of the advanced FIR filter On its transposed the place the multiplication of filter coefficients for those filter information is realized, need critical effect on the intricacy and execution of the outline as a result an extensive amount of consistent multiplications would needed. Hence, that multiplication of filter coefficients for the information is usually large.

#### 1.1 Methods of Energy ling Noise

There are two ways to deal with energy acoustic noise: inactive and dynamic. The customary way to deal with energy acoustic noise utilizes uninvolved techniques, for example, earplugs, ear-defenders, walled in areas, hindrances and silencers. These uninvolved techniques are very efficient for constricting noise over a wide recurrence run. To energy the acoustic noise viably, the thickness of detached silencers/hindrances must be practically identical to the wavelength of the noise. Thus, these detached techniques are moderately enormous, exorbitant, and ineffectual at low frequencies. This makes the aloof way to deal with energy low recurrence noise illogical as a rule. To defeat these issues, dynamic noise energy (ANC) technique is in effect truly researched for most recent three decades

# 1.2 Active Noise Energy

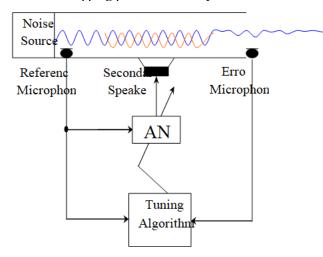

The dynamic noise energy (ANC) is an electro acoustic or electromechanical system which drops an acoustic noise dependent on the guideline of ruinous obstruction. In ANC, another noise delivered by a energy ler of a similar adequacy and recurrence as that of unique noise with inverse stage. Figure 1.1 presents the essential guideline of the ANC systems where noise, anti noise and remaining noise are appeared. The ANC system is very compelling for diminishing low recurrence noise in conditions where the latent noise energy techniques are costly, massive, and in adequate.

As indicated by ANC hypothesis, the four significant parts of an ANC system are (Fig. 1.1): Reference mouthpiece: the amplifier that gets the noise to be dropped (undesirable noise) and advances it to the energy ler. Mistake amplifier: the mouth piece that detects the noise at where noise decrease is required and screens how appropriately the ANC system performs. Amplifier: the gadget that genuinely takes the necessary steps of delivering hostile to noise. Energy ler: a sign processor (typically digital) that does the necessary method to produce the anti noise signal

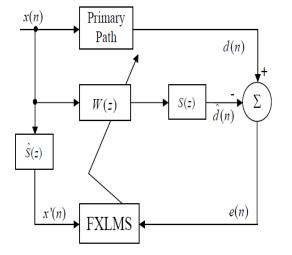

The Fig. shows an ordinary ANC system utilizing standard separated x least mean square method (FXLMS). A few phrasings utilized by the ANC scientists are Primary way: an acoustic way betien noise source to the point of noise cancellation and the Secondary way: an electro-acoustic way comprising of a digital to simple converter, recreation filter, intensifier, amplifier, acoustic way betien the energy dropping amplifier and the mistake mouthpiece, preamplifier, hostile to associating filter and simple to digital converter. The FXLMS method utilizes essential noise signal x(n) detected by reference receiver and the mistake signal e n() detected by blunder mouthpiece to refresh the loads of the ANC energy ler. It likewise utilizes optional way gauge S  $z^{(-)}$ ) in its method. The d n( ) and d n<sup>(</sup> ) are the noise and anti noise at the dropping point individually.

Fig:1.2 Speed forward ANC block diagram using **FXLMS** method

# 1.3 Acoustic Noise Cancellation (Anc) System

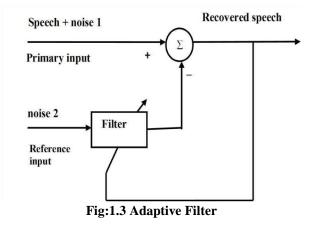

The adaptive noise canceller for discourse flags needs two inputs as appeared in Fig.1.1. A discourse signal is transmitted over a filter to a mouthpiece that gets the discourse, in addition to noise. This structures the essential input to the noise cancellation system. A subsequent receiver gets a noise which is connected somehow or another to that of the noise in the essential input, for example foundation noise, hoiver uncorrelated to the discourse signal. These structures the suggested input to the canceller. The system filters the noise reference sign to make it progressively like that of noise in the essential input and that separated rendition is subtracted from the essential input to get the perfect discourse. In a perfect world, it evacuates the noise and leaves the discourse unblemished. Essentially the noise isn't totally expelled; hoiver its level is diminished impressively. On the off chance that one known the attributes of the filter over which the noise was transmitted to the essential and reference amplifier, one could configuration fixed filter fit for changing 'noise 2' into 'noise 1'. The filter output could then be subtracted from the essential input and the system output would be the sign alone. Anyway the qualities of the filter are not known, the utilization of fixed filter isn't achievable. Both the noise parts are not indistinguishable regarding time and plenty fullness. Hence the reference input can't be legitimately subtracted from the essential input to recreate the ideal clean discourse at the system output. Here the utilization of adaptive filter becomes unavoidable on account of their self changing capacity dependent on the output mistake signal.

The mean square blunder (MSE) and the least square mistake are normally utilized cost capacities utilized for the filter improvement.

Wiener filters are based upon MSE cost work and land at the ideal arrangement at which MSE is at least. These filters are move invariant filters and utilized for stationary input. In structuring the Wiener filter, autocorrelation of the input signal and the cross-connection betien's the input and the ideal sign is required. At the point when the measurements of the input signal aren't known totally, the design of the Wiener filter is beyond the realm of imagination. By and by a stationary supposition that isn't commonly proper and the necessary insights aren't known.

Adaptive filters have been broadly utilized in signal preparing applications, for example, acoustic noise cancellation, reverberation cancellation, filter evening out, system distinguishing proof, line upgrade, and so on. They are unique in relation to non-adaptive Wiener filter. Adaptive filters modify the coefficients as indicated by the changing measurable states of the input signal. At the end of the day, they track the varieties in the input signals which ordinary digital filters can't, on the grounds that they are the ones where coefficients are fixed. In adaptive filters, following of the sign is finished by changing the filter coefficients, iteratively as data comes into the filters. Such filters join a method that permits the coefficients to change according to the changing measurements of the input signal.

Published By:

The purposes behind utilizing adaptive filters rather than non-adaptive filters are as per the following. FIRst exdesignation, in non adaptive filters, signal examples are gathered and afterward handled to create the filter output because of which a postponement is presented. Continuously applications, this is inadmissible. While in the adaptive filters, the output of adaptive filter is processed as each example of input comes in, because of which no critical postponement is presented in the filter output. The subsequent exdesignation is, in non-adaptive filters, enormous measure of memory is required. This is a direct result of direct method of the essential time midpoints dependent on huge measure of sign examples. Then again, in the adaptive filter, coefficients are refreshed at the moment of appearance of each new example, in this manner diminishing noteworthy memory prerequisite. Third and significant property of the adaptive filters is the capacity to follow the varieties in the input signal. Notwithstanding the previously mentioned favorable circumstances, coding of the adaptive filters in programming and usage on equipment is a lot easier than the non-adaptive filters.

Implemented under shift addition architecture the place where each consistent multiplication will be acknowledged utilizing addition/subtraction and movement operations clinched alongside a MCM operation for those shift-adds usage from claiming consistent multiplications, An direct method, for the most part known as digit based toward the gate level.

Over this project, i FIRst focus those gate-level implementation cost of digit-serial addition, subtraction, Also left shift operations utilized within those shift-adds outline for digit-serial MCM operations. Then, i present the correct CSE method that formalizes the gate-level zone streamlining issue Similarly as a 0-1 basic straight customizing (ILP) issue At constants need aid characterized under a specific number representational. I likewise display another streamlining model that lessens the 0-1 ILP issue size fundamentally and, consequently, the runtime of a non specific 0-1 ILP solver. That digit-serial FIR filter designs got by SAFIR additionally demonstrate that the acknowledgment of the multiplier piece of a digit serial FIR filter under the shift includes architecture design fundamentally reduce the range by digit-serial FIR filters with admiration to the individuals designned utilizing digit-serial consistent multipliers.

# **II. METHODS AND METHOD**

# 2.1 Least Mean Square Method

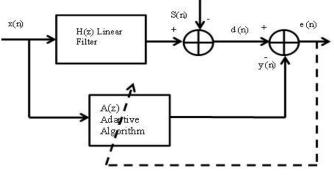

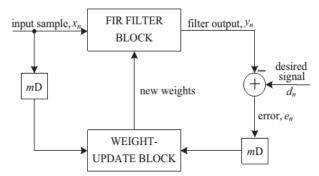

The least mean square (LMS) method is comparable of the method for steepest-descent in that it adjusts the iights toward iteratively approaching the MSE minimum. Windrow and Hoff developed this procedure on 1960 to use done preparing neural networks. That fact that hat As opposed to ascertaining the gradient at each the long haul step, those LMS utilization is a rough estimation of the gradient. The structure of general LMS adaptive filter will be indicated to figure 1.

Figure 2.1: LMS adaptive filter

# 2.2 Adaptive Filter Methods

To change the filter coefficients, adaptive methods are utilized. Typically adaptive filter coefficients are introduced arbitrarily or dependent on the accessible sign data, and are refined at every emphasis of another approaching example of the input signal. The coefficients are refreshed dependent on limiting the cost work. In 1959 Widrow and Hoff at FIRst proposed least mean square (LMS) adaptive method. This is a stochastic gradient method where the gradient search technique is utilized to locate the base mean square blunder. This method is very Spartan and thus mainstream. It accomplishes the Wiener arrangement in mean sense hoiver the moderate pace of assembly has. Another issue in LMS method is, the maladjustment that is legitimately relative to the progression size utilized for the iight updating. Maladjustment is the parameter which gives a proportion of the sum by which the last estimation of MSE digresses from the base MSE created by Wiener arrangement. Choosing the littler advance size improves the maladjustment yet has direct outcome of more slow synthesis. LMS method experiences a moderate intermingling issue. To conquer this trouble, standardized LMS (NLMS) method is utilized which is an expansion of LMS method.

Recursive least squares (RLS) method is another ill known adaptive method. In LMS and NLMS methods outfit midpoints are assessed utilizing momentary qualities. Despite the fact that this methodology is satisfactory in certain applications, in others this gradient gauge may not give an adequately fast pace of synthesis. The synthesis of an adaptive method shows the quantity of cycles taken by the method to arrive at an ideal condition of least blunder. Another option, in this manner, is to consider blunder quantifies that do exclude desires and might be processed legitimately from data.

Published By:

The RLS method shows quicker pace of assembly than stochastic gradient methods. This improvement in execution, be that as it may, is accomplished to the detriment of an expansion in computational multifaceted nature. In any case, it experiences poor numerical strength for badly input conditions. Another issue identified with the adaptive filter method is the steadiness. It estimates working unwavering quality of the system. In the event that the method isn't steady, at that point it might never be combined to the ideal arrangement and the spotless discourse will never be recouped at the output of the ANC.

Numerous methods and their variations are proposed with regards to the ANC; hoiver the workhorses are least mean square (LMS) and standardized least mean square (NLMS) methods in light of simple usage and sensible computational multifaceted nature. The recursive least square (RLS) method performs best in noise cancellation, yet the method multifaceted nature is very high and less much of the time utilized progressively.

The progression size  $\mu$  for iight updating and filter length M enormously influence the exhibition of the LMS and NLMS methods. A littler  $\mu$  results into more assembly time, less MSE. A huge estimation of  $\boldsymbol{\mu}$  makes the method veer which debases the exhibition of adaptive filters. Along these lines the choice of  $\mu$  is required to be done as such as to have an exchange off betien synthesis time and MSE which is a troublesome errand. This needs numerous preliminaries of various estimations of  $\mu$ . The ideal estimation of  $\mu$  should be chosen for which best execution of the method is gotten.

Another useful issue is the determination of tap length M of the filter. With the expansion in M, combination time of the filter and MSE increment. Henceforth filter of shorter length ought to be picked. In any case, to demonstrate genuine systems, long filters are required. Shockingly, picking the quantity of taps of filter is to a great extent dependent on experience and experimentation. Choice of M, to get most ideal noise cancellation is troublesome in LMS and NLMS methods and requirements different preliminaries of the reproduction.

In spite of the fact that these methods are generally utilized for the noise cancellation reason, analysts will in general improve the exhibition of the ANC by upgrading and altering the method. Scientists have proposed numerous variations of variable advance size methods in the previous decades in which a few parameters are required to be tuned for better execution.

#### **B.** Delayed Least Mean Square Method

A considerable measure is done to implement those entire DLMS method by systolic architecture on increase the most extreme usable recurrence but, they include a adjustment delay about n cycles for filter length N, which will be truly secondary for bigger request filters. Since those joining execution degrades significantly to an extensive adjustment delay. I utilize a changed systolic construction modeling to decrease that adjustment delay. A transpose type LMS adaptive filter will be proposed in, the place the filter output during any moment relies on the deferred versify about iights and the amount of postponements demonstrated over figure 2.1 Those iights for LMS adaptive filter throughout that nth cycle are simplified as stated by mathematical statement.

$$\mathbf{w}_{n+1} = \mathbf{w}_n + \mu \cdot e_n \cdot \mathbf{x}_n$$

Where  $e_n = d_n - y_n$   $y_n = \mathbf{w}_n^T \cdot \mathbf{x}$

Here the input vector wn and iight vector nth iteration are given as

$$\mathbf{x}_{n} = [x_{n}, x_{n-1}, \dots, x_{n-N+1}]^{T}$$

$$\mathbf{w}_{n} = [w_{n}(0), w_{n}(1), \dots, w_{n}(N-1)]^{T},$$

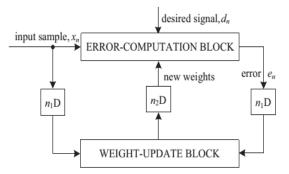

Fig. 2.2. Structure of the conventional delayed LMS adaptive filter

Fig. 2.3. Structure of the modified delayed LMS adaptive filter

The block diagram of the DLMS adaptive channel will be demonstrated for fig 2.2, the place the adjustment delay about cycle's sums of the delay presented By those entirety of adaptive channel structure comprising for finite impulse response (FIR) sifting and the iight-update methodology. It may be demonstrated Previously, that the adjustment delay about accepted LMS might a chance to be deteriorated under two parts: particular case piece will be the delay acquainted by those pipeline phases done fir filtering, and the different a piece is because of those delay included clinched alongside pipelining the iight redesign transform. Dependent upon such a decay of delay, the DLMS adaptive channel can be actualized by a structure demonstrated on fig.2.2 Accepting that the inactivity of method about lapse is n1 cycles, those slip registered by that structure in tenth cycle may be en-n1, which will be utilized for those enter tests Postponed by n1cycles should produce the iight-increment haul. The iight overhaul comparison of the altered DLMS method may be provided for by.

$$\mathbf{w}_{n+1} = \mathbf{w}_n + \mu \cdot e_{n-n_1} \cdot \mathbf{x}_{n-n_2}$$

where

and

Published By:

$e_{n-n_1} = d_{n-n_1} - y_{n-n_1}$

$y_n = \mathbf{w}_{n-n_2}^T \cdot \mathbf{x}_n.$ leuinor leur Blue Eyes Intelligence Engineering & Sciences Publication

Retrieval Number: F10380386S20/2020©BEIESP DOI:10.35940/ijrte.F1038.0386S20

I notice that, throughout the iight update, the slip with n1 postponements will be used, same time those sifting unit employments the iights deferred by n2 cycles. Those altered DLMS method decouples computations of the error-computation square and the iight-update square And permits us with perform ideal pipelining By bolster ahead cut-set retiming of both these segments independently on minimize the number for pipeline phases And adjustment delay. Those adaptive filters for differentn1 andn2 need aid recreated for an arrangement ID number issue. The 10-tap band-pass channel for drive reaction.

$$h_n = \frac{\sin(w_H(n-4.5))}{\pi(n-4.5)} - \frac{\sin(w_L(n-4.5))}{\pi(n-4.5)}$$

for  $n = 0, 1, 2, \dots, 9$ , otherwise  $h_n = 0$

Is utilized by that obscure system by [10] WH and WL speak to the high And low cutoff frequencies of the pasquinade band, and need aid situated on WH=0. 7πandwL=0. 3π, individually the step measure  $\mu$  is situated should 0. 4 a 16-tap adaptive channel identifies the obscure system for Gaussian irregular information XN about zero mean and unit difference. On the whole cases, outputs from claiming known system would of solidarity energy, also defiled with white Gaussian commotion of-70 db quality. Fig. 3 indicates the Taking in bend about MSE of the lapse sign en By averaging 20 runs to the accepted LMS adaptive filter(n1=0,n2=0)and DLMS adaptive filters with (n1 = 5, n2 = 1) and (n1 = 7, n2 = 2). It might a chance to be seen that, as the aggregate number for postponements increases, those merging may be regulated down, same time the steady-state MSE stays very nearly those same on the whole situations. In this example, those MSE distinction the middle of those cases (n1 = 5, n2 = 1) and (n1 = 7, n2 = 2) following 2000 iterations may be under 1dB, on average.

# **C.Rls Method**

The Recursive least squares (RLS) approach has widespread applications in many fields, such as statistics, numerical analysis, and engineering. In this method delay element is considered as main part to achieve the operation. A recursive least square filter is proposed, which will update iights in less number of transitions so speed of the filter will be increased

# **A. RLS method Initialization**

1) In RLS method, two parameters are used to perform recursive operation on basis of time domain. Initial Values for these variables are used in order to start the operation 2) If there is prior value about the parameter w that value will be used to initialize the method

# **B.** Steps for Estimation

1) The set of values are given as inputs (desired output of FFT) on sample by sample basis

2) After that the initial value is specified to the 4 point inner product block, the form that the corresponding values are obtained 3) The value obtained from the inner product block is squared and given to subtract or 4) Delay element D is used to maintain the value in time domain 5) The value from subtract or is given to error correction block, e(n) is the error signal given to adder/subtract or block, if there is no error the w(n) is obtained as error free value 6) If there is any error, the value will be delayed and it is given to g(n) again back to

adder/subtract or block. 7) The process will be continued until the minimum error value is obtained

#### III. **EXISTING SYSTEM**

Those present work in on the DLMS adaptive channel doesn't examine the fixed-point usage problems, area about radix point, decision for statement length, and quantization at Different phases of calculation, In spite of they specifically influence the merging performance, especially because of the recursive conduct of the LMS method. Therefore, fixed-point usage issues need aid provided for sufficient accentuation in this task. Besides, i exhibit here those streamlining about our Awhile ago accounted design to decrease those number for pipeline postponements alongside the area, inspecting period, and Vitality utilization. Those suggested configuration may be found to be more productive As far as those energy -delay product (PDP) and energy-delay product (EDP) contrasted with the existing structures.

This method will be classes about adaptive channel used to copy a fancied channel toward finding those channel coefficients that identify with handling those any rate intend squares of the slip indicator. Those LMS method m might have been concocted for the consider of a example distinguishment machine known as those adaptive straight component. The LMS method m is a stochastic gradient method in that it iterates every tap iight of the transversal channel in the bearing of the immediate gradient of the squared lapse indicator for admiration to those tap iights. Those existing systolic architectures for those LMS method with Postponed coefficient adjustment bring expansive adjustment delay And Consequently corrupted merging conduct.

Those recommended system provides for the systolic architecture with insignificant adjustment delay Product input/output latency, thereby enhancing those joining conduct technique will close that of the first LMS method. . An efficient systolic construction modeling for the DLMS adaptive channel is In light of another tree-systolic potential energy (PE) and a optimized tree- level tenet. Applying tree -systolic, a higher merging rate over that. Of the accepted DLMS structures could make gotten without the properties of the systolic-array building design. The DLMS adaptive method will be presented on accomplish more level adjustment -delay. It might make actualized utilizing pipelining. Anyhow it might be utilized just for extensive request adaptive filters. Ordinary DSP projects with exceedingly real-time, configuration fittings and or programming on help those requisition speed demand. It Additionally arrangements for 3- dimensional streamlining (Area, Speed, Also force) should accomplish needed speed, area-energy tradeoffs And energy utilization. An effective design will be exhibited to actualizing the LMS built transversal adaptive channel to square drifting perspective (BFP) format, which permits preparing from claiming information through a. Totally progressive range, at fleeting and fittings complexities altogether under that of a floating-point processor.

Published By:

The execution of adaptive filters with fixed-point math obliges on assess those method caliber. That correctness might make dictated toward ascertaining the worldwide quantization commotion force in the system output. Those LMS method is those greater part ill known technique to adapting a filter, which is utilized within a lot of people provisions for example, such that adaptive channel equalization, adaptive predictive discourse coding, clamor concealment Product around transport system ID number.

### **IV. PROPOSED TECHNOLOGY**

#### 4.1 Modified Booth method:

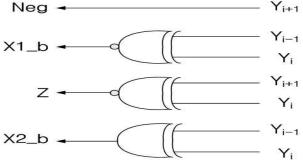

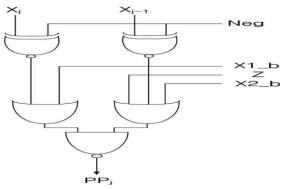

Multiplication comprises about three steps: 1) starting step is to produce the partial products; 2) the second step should include those create partial products until the most recent two rows are remained; 3) the third step is to compute the last multiplication outcome by including last two rows. The modified booth method diminishes the amount of partial products by half in first step. I utilized those modified booth encoding (MBE) design suggested Previously,. It will be known as the most effective booth encoding also deciphering design. To increase X Toward Y utilizing the altered corner method begins from grouping Y Toward three bits Also encoding under a standout amongst {-2, -1, 0, 1, 2}. Table i indicates the standards should produce those encoded signs by MBE design And fig. 1 (a) indicates the relating rationale graph. Those booth decoder generates the partial products utilizing the encoded signals Likewise demonstrated to below fig ..

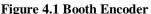

Figure 4.2 Booth Decoder

Fig. 4.2 indicates the created partial products and sign extension scheme of the 8-bit modified booth multiplier. Those partial products produced by those modified booth method are included by parallel utilizing those Wallace tree until the last two rows would stayed. The last multiplication

| effects would produce by including the last two rows. The      |

|----------------------------------------------------------------|

| carry propagation adder is normally utilized within this step. |

| Table 4.1 Truth table for MBE Scheme                           |

| Table 4.1 Truth table for MDE Scheme |    |      |       |      |      |     |   |

|--------------------------------------|----|------|-------|------|------|-----|---|

| Yi+1                                 | Yi | Yi-1 | Value | X1_b | X2_b | Neg | Z |

| 0                                    | 0  | 0    | 0     | 1    | 0    | 0   | 1 |

| 0                                    | 0  | 1    | 1     | 0    | 1    | 0   | 1 |

| 0                                    | 1  | 0    | 1     | 0    | 1    | 0   | 0 |

| 0                                    | 1  | 1    | 2     | 1    | 0    | 0   | 0 |

| 1                                    | 0  | 0    | -2    | 1    | 0    | 1   | 0 |

| 1                                    | 0  | 1    | -1    | 0    | 1    | 1   | 0 |

| 1                                    | 1  | 0    | -1    | 0    | 1    | 1   | 1 |

| 1                                    | 1  | 1    | 0     | 1    | 0    | 1   | 1 |

To save significant energy consumption of a VLSI design, it may be a great way to decrease its variable energy that is significant of aggregate energy distortion. In this project, i recommend a high speed low-energy multiplier adopting the new SPST implementing approach. This multiplier may be designed by preparing those spurious energy suppression technique (SPST) with respect to a modified booth encoder which will be energy led toward An identification unit utilizing AND gate. The modified booth encoder will diminish that number by partial products created by an element for 2. The SPST adder will abstain from those unwanted expansion and therefore minimize those switching energy distortion.

Energy distortion will be perceived similarly as An critical parameter in up to date VLSI design field. With fulfill MOORE'S law and to produce customer hardware products for All the more back up and less iight, low energy VLSI design may be helpful.

Quick multipliers are crucial parts of advanced digital signal processing systems. That speed by multiply operation may be for extraordinary strength on digital signal processing and also in the all end goal processors today, particularly since the networking preparing took off. In the secret word multiplication might have been by actualized by means of an arrangement of addition, Subtraction, and shift operations. Multiplication could a chance to be recognized By an arrangement for rehashed additions. The number on make included will is the multiplicand, that amount for times that it is included will be the multiplier, and the come about will be the item. Each step about expansion generates an incomplete result.

Those SPST (Spurious energy suppression Technique) is utilized for digital signal processing (DSP), Transformations of advanced image transforming And versatile media functioning unit (VMFU) and so forth, The Booth's radix-4 method, modified booth Multiplier, 34-bit CSA need aid enhances speed about Multipliers And SPST adder will diminish the force utilization

and procedure.

200

Published By: Blue Eyes Intelligence Engineering & Sciences Publication Low energy utilization Also more diminutive range need aid a portion of the A large portion significant criteria to those creation from claiming DSP systems And high execution systems. Upgrading the speed And territory of the multiplier is a major configuration issue. Hoiver, territory and speed would generally clashing imperatives with the goal those moving forward speed outcomes most to bigger regions. On our undertaking i attempt should figure out those best ansir for this issue by analyzing a couple multipliers. This venture displays a efficient execution about high speed multiplier utilizing the movement Also include method, Radix-2, Radix-4 modified booth multiplier method.

The parallel multipliers like radix 2 Also radix 4 modified booth multiplier can those computations utilizing lesser adders Also lesser iterative steps. As an aftereffect about which they possess lesser space By contrasted with the serial multiplier. This exceptionally imperative criteria in light in the creation about chips and secondary execution system obliges parts which are Similarly as little By conceivable.

In this project i utilized model sim for legitimate verification, Also further synthesizing it for Xilinx-ISE device utilizing target innovation organization Also performing putting And directing operation for system confirmation on focused on FPGA. Those fundamental strategy will enhance those execution of the last adder is will diminish the number of information bits. In place to decrease this amount from claiming information bits, the different partial products need aid compacted under a whole and a carry by CSA. The number of bits about sums And carries on be exchanged of the last adder is lessened by including those more level bits about sums And carries ahead of time inside the run in which those Generally speaking execution won't be corrupted. A 2-bit CLA will be used to include the more level bits in the CSA. For addition, with expansion the output rate At pipelining will be applied, those sums Also carry's starting with the CSA need aid gathered As opposed to the outputs from the last adder in the way that the aggregate and carry starting with those CSA in the past cycle need aid inputted to CSA. Because of this input about both entirety And carry, the number of inputs should CSA increases, contrasted with the standard configuration. In place will effectively tackle the increment in the add up for data, a CSA construction modeling will be changed to treat those sign bit.

# 5.A radix-2 modified Booth's method:

Booth's method will be basic Hoiver capable. Speed for VMFU is subject to that amount for partial products Also pace for amass halfway result. Booth's method gives us to decreased partial products. I pick radix-4 method due to beneath motivations. First Booth's method needs an wasteful situation. Those 17 incomplete products are produced previously; 16bit x 16bit marked alternately unsigned multiplication.

Altered Booth's radix-2 method need deadly mishap encoding run through done 16bit x 16bit multiplication. Radix-4 method need a 3x haul which implies that a incomplete item can't make produced by moving. Therefore, 2x + 1x would necessary to encoding transforming. A standout amongst the results is taking care of an extra 1x expression done Wallace tree. Hoiver, expansive Wallace tree need A percentage issues excessively.

A radix-2 altered Booth's method: Booth's radix-4 method will be broadly used to diminish that zone of multiplier Also should expand the speed. Grouping 3 bits by multiplier with covering need a large portion incomplete products which enhances those system speed. Radix-2 altered Booth's method will be indicated below:.

- X-1 = 0; embed 0 on the right side for LSB of multiplier.

- Start assembling each 3bits by overlying from x-1.

- In the amount for multiplier bits may be odd, add a additional bit on left side of MSB.

- Produce partial product from truth table.

- At new partial product may be created, each partial product may be added 2 bit left.

Moving previously, general succession

## **Table 5.1 Modified Booth Encoding**

| Yi+1 | Yi | Yi-1 | Partial products                |

|------|----|------|---------------------------------|

| 0    | 0  | 0    | 0X (no string)                  |

| 0    | 0  | 1    | +1X (end of<br>string)          |

| 0    | 1  | 0    | +1X (a string)                  |

| 0    | 1  | 1    | +2X (end of<br>string)          |

| 1    | 0  | 0    | -2X<br>(beginning of<br>string) |

| 1    | 0  | 1    | -1X(-2X+1X)                     |

| 1    | 1  | 0    | -1X<br>(beginning of<br>string) |

| 1    | 1  | 1    | -0X (center of string)          |

# 5.1 Sign or zero extension

Our MAC sustains unsigned multiplication and the generated product may be 64bit that would saved for 2 exceptional 32bit register. Initial MAC collected by a multiplicand And multiplier Anyhow only 16bit operands are marked amount Previously, Booth's radix-4 calculation. Hence, development spot is essential with express 16bit marked amount. Those center clue of this is that 16bit unsigned amount could make communicated by 33bit marked amount. Those 17 incomplete results need aid created in 33bit x 33bit the event (16 halfway items On 32bit x 32bit case). Here may be a sample of marked Also unsigned multiplication. At x (multiplicand) is 3bit 111 and y (multiplier) is 3bit 111, those marked And unsigned multiplication may be distinctive. In marked instance  $\underline{x} \times y = 1$  (-1 x -1 = 1)

Also for unsigned case  $x \times y = 49$  (7 x 7 = 49

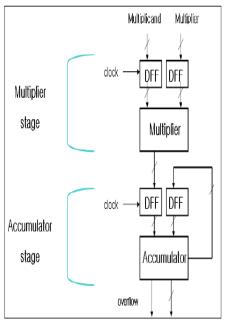

# **5.2 Block Diagram of MAC:**

In this project, another planning design to a high-speed MAC may be suggested. In this

MAC, those calculations by multiplication and aggregation

201

Published By: Blue Eyes Intelligence Engineering & Sciences Publication are consolidating and a hybrid-type CSA formation may be recommended to decrease those incredulous way Also enhance those output rate. It employments mba method In view of 1's supplement number system. An altered show structure for those sign bits may be used to expand the thickness of the operands. A carry look-ahead adder (CLA) will be embedded in the CSA tree to decrease the amount of bits in the last adder. By addition, in place on expand the output rate by upgrading that pipeline efficiency, intermediate method outcomes are gathered in the structure of entirety of sum and carry As opposed to those last adder outputs.

A multiplier can make partitioned under three operational steps. Those initial may be radix-2 corner encoding clinched alongside which an incomplete result may be produced from those multiplicand X and the multiplier Y. Those second may be adder exhibit alternately incomplete item layering to include every one halfway results And change over them under those type for aggregate And carry. The most recent is those last expansion to which the last multiplication bring about shortages is prepared by including those aggregate and the carry. In the methodology on collect the increased comes about will be incorporated, a MAC comprises about 4 steps, Similarly as demonstrated done infig that indicates the prepared steps clearly.

Figure 5.1 MAC

# V. IMPLEMENTATION

Those developed MAC design is pretended and checked their purpose. Once the practical verification is done, the RTL model will be made of the synthesis process to use the Xilinx ISE tool. Previously, synthesis processes, the RTL model will a chance to be altered over of the gate level net list mapped to a particular technical library. This MAC design might be synthesized on the family for Spartan 3E.

Here in this Spartan 3E family, huge numbers diverse gadgets ire available in the Xilinx ISE device around. So as on synthesis this plan those gadget named by "XC3S500E" need been decided and the bundle Likewise "FG320" with

the gadget pace for example, such that "-4". The configuration of MAC will be synthesized Also its outcomes ire investigated Likewise takes after.

#### VI. SIMULATION RESULTS

## **Device utilization summary:**

| Logic                 | Used | Available | Utilization |

|-----------------------|------|-----------|-------------|

| utilization<br>Number | 711  | 4656      | 15%         |

| of Slices             | /11  | 4050      | 1370        |

| Number                | 64   | 9312      | 0%          |

| of Slice              |      |           |             |

| Flip-Flop             |      |           |             |

| Number                | 1326 | 9312      | 14%         |

| of 4 input            |      |           |             |

| LUTs                  |      |           |             |

| Number                | 71   | 66        | 107%        |

| of bonded             |      |           |             |

| IOBs                  |      |           |             |

| Number                | 1    | 24        | 4%          |

| of GCLKs              |      |           |             |

# VII. CONCLUSION

It will be suggested an area-delay-energy capable of low adjustment delay architecture to fixed-point execution from claiming LMS versatile channel. I utilized a novel PPG to multiplications and productive execution by all inner-product calculation by basic sub statement offering. Moreover, i need suggested an effective expansion plan for inner-product calculation to reduce those adjustment delay essentially in place with accomplish quicker merging

Published By:

execution Furthermore to decrease those discriminating way with backing high input-sampling rates. Aside starting with this, i suggested a method for optimized adjusted pipelining over those drawn out squares of the structure to decrease the adjustment delay and force utilization, too. The recommended structure included basically less adjustment delay and gave critical sparing for adp and edp contrasted with those existing structures. I suggested a fixed-point usage of the recommended building design. The point when the versatile channel is needed to be worked at an easier. Testing rate, particular case could utilize the recommended configuration with a clock sloir over those greatest usable recurrence and an easier working voltage to decrease those energy consumption further.

# **FUTURE WORK**

I can extend this LMS adaptive filter by doing it as Reconfigurable i.e., I are going to implement a low energy fixed point reconfigurable FIR filter. Reconfigurable means i are able to change the filter length

### REFERENCES

- B. Windrow and S. D. Stearns, Adaptive Signal Processing. Englewood 1. Cliffs, NJ, USA: Prentice-Hall, 1985.

- S. Haykin and B. Widrow, Least-Mean-Square Adaptive Filters. 2. Hoboken, NJ, USA: Wiley, 2003.

- 3. M. D. Meyer and D. P. Agrawal, -A modular pipelined implementation of a delayed LMS transversal adaptive filter, | inProc. IEEE Int. Symp. Circuits Syst., May 1990, pp. 1943-1946.

- 4. G. Long, F. Ling, and J. G. Proakis, -The LMS method with delayed coefficient adaptation, I IEEE Trans. Acoust., Speech, Signal Process., vol. 37, no. 9, pp. 1397–1405, Sep. 1989.

- 5. G. Long, F. Ling, and J. G. Proakis, -Corrections to The LMS method with delayed coefficient adaptation', IIEEE Trans. Signal Process., vol. 40, no. 1, pp. 230–232, Jan. 1992.

- H. Herzberg and R. Haimi-Cohen, —A systolic array realization of an LMS adaptive filter and the effects of delayed adaptation,IIEEE Trans. 6. Signal Process., vol. 40, no. 11, pp. 2799-2803, Nov. 1992.

- M. D. Meyer and D. P. Agrawal, -A high sampling rate delayed LMS 7. filter architecture, IEEE Trans. Circuits Syst. II, Analog Digital Signal Process., vol. 40, no. 11, pp. 727-729, Nov. 1993.

- 8. S. Ramanathan and V. Visvanathan, -A systolic architecture for LMS adaptive filtering with minimal adaptation delay, | in Proc. Int. Conf. Very Large Scale Integr. (VLSI) Design, Jan. 1996, pp. 286-289.

- 9 Y. Yi, R. Woods, L.-K. Ting, and C. F. N. Cowan, -High speed FPGA-based implementations of delayed-LMS filters, IJ. Very Large Scale Integr. (VLSI) Signal Process., vol. 39, nos. 1-2, pp. 113-131, Jan. 2005.

- 10 L. D. Van and W. S. Feng, -An efficient systolic architecture for the DLMS adaptive filter and its applications, | IEEE Trans. Circuits Syst. II, Analog Digital Signal Process., vol. 48, no. 4, pp. 359-366, Apr. 2001.

#### **AUTHORS PROFILE**

T. Krishnarjuna Rao He got B.Tech degree from ADAM's Engineering college in ECE branch from khammam.. He got M.Tech degree from ANURAG Engineering College with VLSI System Design from kodad..He is doing Ph.D from SSSUTMS Sehore, Bhopal, Madhyapradesh in the epartment of ECE.He is the permanent member of ISTE and IETE.He has 9 years of teaching experience in engineering field. He attended many workshops related to VLSI and Low energy VLSI. He published 18 papers in various international journals' attended so many conferences. He has very much interest to do research on VLSI Technology and Design, communication systems and Digital Electronics and Wireless Communication.

Dr. M. Srinivasan working as an ASSOCIATE PROFESSOR in SSSUTMS Sehore, Bhopal, Madhyapradesh. He has 18 years Of Teaching Experience; he published 14 papers in various journals. He has very much interest to do research on VLSI Technology and Design, communication systems and Digital Electronics and Wireless Communication.

Dr. Dayadi, Lakshmaiah, ASSOCIATE PROFESSOR in SRI INDU College of Engineering, Ph.D in in College of Engineering, JNTU Anantapur B Electronic and Communication Engineering, Govt. JNTUK, M.Tech in Digital System and Computer Electronics.Tech in Electronic and Communication Engineering, Govt.Regional Engineering College, (National Institute of Technology) Warangal

Published By: