Abstract

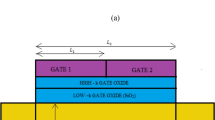

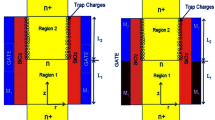

A charge plasma technique based dopingless (DL) accumulation mode (AM) junctionless (JL) cylindrical surrounding gate (CSG) MOSFET has been proposed and extensively investigated. Proposed device has no physical junction at source to channel and channel to drain interface. The complete silicon pillar has been considered as undoped. The high free electron density or induced N+ region is designed by keeping the work function of source/drain metal contacts lower than the work function of undoped silicon. Thus, its fabrication complexity is drastically reduced by curbing the requirement of high temperature doping techniques. The electrical/analog characteristics for the proposed device has been extensively investigated using the numerical simulation and are compared with conventional junctionless cylindrical surrounding gate (JL-CSG) MOSFET with identical dimensions. For the numerical simulation purpose ATLAS-3D device simulator is used. The results show that the proposed device is more short channel immune to conventional JL-CSG MOSFET and suitable for faster switching applications due to higher I ON/I OFF ratio.

Similar content being viewed by others

References

J.P. Colinge, C.-W. Lee, A. Afzalian et al., Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Z. Chen, Y. Xiao, M. Tang et al., Surface-potential-based drain current model for long-channel junctionless double-gate MOSFETs. IEEE Trans. Electron Dev. 59(12), 3292–3298 (2012)

M.-H. Han, C.-Y. Chang, H.-B. Chen et al., Device and circuit performance estimation of junctionless bulk FinFETs. IEEE Trans. Electron Dev. 60(6), 1807–1813 (2013)

S. Barraud, M. Berthome, R. Coquand et al., Scaling of trigate junctionless nanowire MOSFET with gate length down to 13 nm. IEEE Electron Dev. Lett. 33(9), 1225–1227 (2012)

C.W. Lee, A.N. Nazarov, I. Ferain et al., Low subthreshold slope in junctionless multiple gate transistors. Appl. Phys. Lett. 96(2), 102106-1–102106-3 (2010)

G. Leung, C.O. Chui, Variability impact of random dopant fluctuation on nanoscale junctionless FinFETs. IEEE Electron Dev. Lett. 33(6), 767–769 (2012)

A. Gnudi, S. Reggiani, E. Gnani et al., Analysis of threshold voltage variability due to random dopant fluctuations in junctionless FETs. IEEE Electron Dev. Lett. 33(3), 336–338 (2012)

M. Aldegunde, A. Martinez, J.R. Barker, Study of discrete doping induced variability in junctionless nanowire MOSFETs using dissipative quantum transport simulations. IEEE Electron Dev. Lett. 33(2), 194–196 (2012)

S.-J. Choi, M. Dong-Il, S. Kim et al., Sensitivity of threshold voltage to nanowire width variation in junctionless transistors. IEEE Electron Dev. Lett. 32(2), 125–127 (2011)

N. Trivedi, M. Kumar, S. Haldar, S.S. Deswal, M. Gupta, R.S. Gupta, Analytical modelling of junctionless accumulation mode MSOFET (JAM-CSG). Int. J. Numer. Model. Electron. Netw. Dev. Fields (2016). doi:10.1002/jnm.2162

M. Parihar, D. Ghosh, A. Kranti, Single transistor latch phenomenon in junctionless transistors. J. Appl. Phys. 113(18), 184503-1–184503-5 (2013)

B. Rajasekharan, R.J.E. Hueting, C. Salm et al., Fabrication and characterization of the charge-plasma diode. IEEE Electron Dev. Lett. 31(6), 528–530 (2010)

R.J.E. Hueting, B. Rajasekharan, C. Salm et al., Charge plasma P–N diode. IEEE Electron Dev. Lett. 29(12), 1367–1368 (2008)

M.J. Kumar, K. Nadda, Bipolar charge-plasma transistor: a novel three terminal device. IEEE Trans. Electron Dev. 59(4), 962–967 (2012)

C. Sahu, J. Singh, Charge-plasma based process variation immune junctionless transistor. IEEE Electron Dev. Lett. 35(3), 411–413 (2014)

C. Shan, Y. Wang, M.T. Bao, A charge-plasma-based transistor with induced graded channel for enhanced analog performance. IEEE Trans. Electron Dev. 63(6), 2275–2281 (2016)

N. Trivedi, M. Kumar, S. Haldar, S.S. Deswal, M. Gupta, R.S. Gupta, Analytical modeling simulation and characterization of short channel junctionless accumulation mode surrounding gate (JLAMSG) MOSFET for improved Analog/RF performance. Superlattic. Microstruct. 100, 1263–1275 (2016)

SILVACO Int (2015) Santa Clara, CA, Atlas 3D device simulator

Y. Pratap, S. Haldar, M. Gupta, Performance evaluation and reliability issue of junctionless CSG MOSFET for RFIC design. Electron Dev. IEEE Trans. 59(12), 418–424 (2014)

M.S. Parihar, D. Ghosh, A. Kranti, Ultra low power junctionless MOSFET’s for Subthreshold logic applications. Electron Dev. IEEE Trans. 60(5), 1540–1546 (2013)

S. Dubey, P.K. Tiwari, S. Jit, On-current modeling of short-channel double-gate (DG) MOSFETs with a vertical Gaussian-like doping profile. J. Semicond. 34(5), 1–8 (2013)

H. Lou, L. Zhang, Y. Lin, S. Yang, J. He, M. Chan, A junctionless nanowire transistor with a dual-material gate. IEEE Trans. Electron Dev. 59(7), 1829–1836 (2012)

G.S. Kumar, B. Srimanta, Novel characteristics of junction less dual metal cylindrical surround gate (JLDM CSG) MOSFET. Res. Sci. J. 2(1), 44–52 (2013)

S. Cho et al., A RF performance and small-signal parameter extraction of junctionless silicon nanowire MOSFETs. Electron Dev. IEEE Trans. 58(5), 1388–1396 (2011)

M. Kumar, S. Haldar, M. Gupta, R.S. Gupta, A new T-shaped source/drain extension (T-SSDE) gate underlap GAA MOSFET with enhance subthreshold analog/RF performance for low power applications. Solid State Electron. 101, 13–17 (2014)

Acknowledgements

One of the authors, Mr. Nitin Trivedi, is grateful to CSIR for providing financial assistance to carry out this research work. Authors are also grateful to the Director, Maharaja Agrasen Institute of Technology, for providing the facilities to carryout this research work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Trivedi, N., Kumar, M., Haldar, S. et al. Charge plasma technique based dopingless accumulation mode junctionless cylindrical surrounding gate MOSFET: analog performance improvement. Appl. Phys. A 123, 564 (2017). https://doi.org/10.1007/s00339-017-1176-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-017-1176-y