Abstract

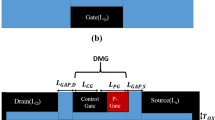

For the first time, we have explored the effect of positive and negative interface trap charges on the dopingless device using charge plasma concept and named the proposed device as heterogeneous gate dielectric charge plasma tunnel field-effect transistor (HD-CP-TFET). The heterogeneous gate dielectric is considered to improve the ON-state current and device performance. The main intention of this work is to improve the drain current, transconductance characteristics along with linearity figure-of-merits (FOMs). A comparative analysis is done with conventional CP-TFET in the presence of interface trap charges (ITCs). From comparative results, it is found that the proposed device shows a better performance in the presence of interface trap charges. All the simulations are performed on ATLAS TCAD device simulator. The results show that the proposed device has a better tunneling current, transconductance (\(g_{\text {m}}\)), cut-off frequency (\(f_{\text {T}}\)), second-order voltage intercept point (VIP2), third-order voltage intercept point (VIP3), third-order input intercept point (IIP3), and third-order intermodulation distortion (IMD3). Thus, the proposed device (HD-CP-TFET) shows the better performance in the presence of interface trap charges and indicates that this device is suitable for low-voltage analog/RF applications.

Similar content being viewed by others

References

U.E. Avci, D.H. Morris, I.A. Young, Tunnel field-effect transistors: prospects and challenges. IEEE J. Electron Devices Soc 3(3), 88–95 (2015)

V. Saripalli, A. Mishra, S. Datta, V. Narayanan, An energy-efficient heterogeneous CMP based on hybrid TFET-CMOS cores. In: Proc. 48th ACM/EDAC/IEEE Design Autom. Conf. (DAC), New York, NY, USA, pp. 729–734 (2011)

D. Esseni, M. Guglielmini, B. Kapidani, T. Rollo, M. Alioto, Tunnel FETs for ultralow voltage digital VLSI circuits: Part I-Device-circuit interaction and evaluation at device level. IEEE Trans. Very Large Scale Integr. (VLSI) Syst 22(12), 2488–2498 (2014)

S. Datta, R. Bijesh, H. Liu, D. Mohata, V. Narayanan, Tunnel transistors for low power logic. In: Proc. IEEE Compound Semicond. Integr. Circuit Symp. (CSICS), Monterey, CA, USA, pp. 1–4 (2013)

M. Lanuzza, S. Strangio, F. Crupi, P. Palestri, D. Esseni, Mixed tunnel-FET/MOSFET level shifters: a new proposal to extend the tunnel-FET application domain. IEEE Trans. Electron Devices 62(12), 3973–3979 (2015)

K. Boucart, A.M. Ionescu, Double gate tunnel FET with high \(\kappa\) gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

S.W. Kim, J.H. Kim, T.-J.K. Liu, W.Y. Choi, B.-G. Park, Demonstration of L-shaped tunnel field-effect transistors. IEEE Trans. Electron Devices 63(4), 1774–1778 (2016)

A.C. Seabaugh, Q. Zhang, Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98(12), 2095–2110 (2010)

S. Strangio et al., Impact of TFET unidirectionality and ambipolarity on the performance of 6T SRAM cells. IEEE J. Electron Devices Soc. 3(3), 223–232 (2015)

P.N. Kondekar, K. Nigam, S. Pandey, D. Sharma, Design and analysis of polarity controlled electrically doped tunnel FET with bandgap engineering for analog/RF applications. IEEE Trans. Electron Devices 64(2), 412–418 (2017)

K. Nigam, S. Gupta, S. Pandey, P.N. Kondekar, D. Sharma, Controlling the ambipolarity and improvement of RF performance using Gaussian Drain Doped TFET. Int. J. Electron. 105(5), 806–816 (2017)

V. Nagavarapu, R. Jhaveri, J.C.S. Woo, The tunnel source (PNPN) n-MOSFET: a novel high performance transistor. IEEE Trans. Electrons Devices 55(4), 1013–1019 (2008)

S. Saurabh, M.J. Kumar, Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans. Electrons Devices 58(2), 404–410 (2011)

Bandi Venkata Chandan, Sushmitha Dasari, S. Yadav, D. Sharma, Approach to suppress ambipolarity and improve RF and linearity performances on ED-Tunnel FET. IET. Micro Nano Lett. 13(5), 684–689 (2018)

S. Strangio et al., Assessment of InAs/AlGaSb tunnel-FET virtual technology platform for low-power digital circuits. IEEE Trans. Electron Devices 63(7), 2749–2756 (2016)

A. Sharma, A.K. Reza, K. Roy, Proposal of an intrinsic-source broken-gap tunnel FET to reduce band-tail effects on subthreshold swing: a simulation study. IEEE Trans. Electrons Devices 63(6), 2597–2602 (2016)

N. Damrongplasit, C. Shin, S.H. Kim, R.A. Vega, T.-J.K. Liu, Study of random dopant fluctuation effects in germanium-source tunnel FETs. IEEE Trans. Electrons Devices 58(10), 3541–3548 (2011)

A. Chattopadhyay, A. Mallik, Impact of a spacer dielectric and a gate overlap/underlap on the device performance of a tunnel field-effect transistor. IEEE Trans. Electron Devices 58(3), 677–683 (2011)

W.Y. Choi, W. Lee, Hetero-gate-dielectric tunneling fieldeffect transistors. IEEE Trans. Electron Devices 57(9), 2317–2319 (2010)

R. Wang et al., Investigations on line-edge roughness (LER) and line-width roughness (LWR) in nanoscale CMOS technology: Part II-Experimental results and impacts on device variability. IEEE Trans. Electron Devices 60(11), 3676–3682 (2013)

M.G. Pala, D. Esseni, F. Conzatti, in Impact of interface traps on the IV curves of InAs tunnel-FETs and MOSFETs: a full quantum study. Proc. IEEE IEDM, San Francisco, CA, USA, pp. 1–4 (2012)

J. Madan, R. Chaujar, Interfacial charge analysis of heterogeneous gate dielectric-gate all around-tunnel FET for improved device reliabiltiy. IEEE Trans. Device Mater. Reliab. 16(2), 227–234 (2016)

Y. Qiu, R. Wang, Q. Huang, R. Huang, A comparative study on the impacts of interface traps on tunneling FET and MOSFET. IEEE Trans. Electron Devices 61(5), 1284–1291 (2014)

Y. Pratap, S. Haldar, R.S. Gupta, M. Gupta, Performance evaluation and reliability issues of junctionless CSG MOSFET for RFIC design. IEEE Trans. Device Mater. Rel 14(1), 418–425 (2014)

G.B. Beneventi, E. Gnani, A. Gnudi, S. Reggiani, G. Baccarani, Can interface traps suppress TFET ambipolarity. IEEE Electron Device Lett. 34(12), 1557–1559 (2013)

P. Venkatesh, K. Nigam, S. Pandey, D. Sharma, P.N. Kondekar, Impact of interface trap charges on performance of electrically doped tunnel FET with heterogeneous gate dielectric. IEEE Trans. Device Mater. Rel. 17(1), 245–252 (2017)

S. Gupta, K. Nigam, S. Pandey, D. Sharma, P.N. Kondekar, Effect of interface trap charges on performance variation of heterogeneous gate dielectric junctionless-TFET. IEEE Trans. Electron Devices 64(11), 4731–4737 (2017)

M.-L. Fan, V.P.-H. Hu, Y.-N. Chen, P. Su, C.-T. Chuang, Analysis of single-trap-induced random telegraph noise and its interaction with work function variation for tunnel FET. IEEE Trans. Electron Devices 60(6), 2038–2044 (2013)

G.F. Jiao et al., in New degradation mechanisms and reliability performance in tunneling field effect transistors. In Proc. IEEE IEDM, Baltimore, MD, USA, pp. 1–4 (2009)

K. Nadda, M.J. Kumar, Thin-film bipolar transistors on recrystallized polycrystalline silicon without impurity doped junctions: proposal and investigation. J. Disp. Technol. 10(7), 590–594 (2014)

M.J. Kumar, K. Nadda, Bipolar charge-plasma transistor: a novel three terminal device. IEEE Trans. Electron Devices 59(4), 962–967 (2012)

M.J. Kumar, S. Janardhanan, Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60(10), 3285–3290 (2013)

ATLAS Device Simulation Software, Silvaco Int (Santa Clara, CA, USA, 2015)

B.Venkata Chandan, K. Nigam, S. Pandey, D. Sharma, P. N. Kondekar, in Impact of Temperature on Polarity Controlled Electrically Doped TFET for Analog/RF and Linearity Performance. Conference on Information and technology (CICT), pp. 1–5(2017)

T.-K. Chiang, A compact model for threshold voltage of surroundinggate MOSFETs with localized interface trapped charges. IEEE Trans. Electron Devices 58(2), 567–571 (2011)

S. Shabde, A. Bhattacharyya, R.S. Kao, R.S. Muller, Analysis of MOSFET degradation due to hot-electron stress in terms of interfacestate and fixed-charge generation. Solid State Electron. 31(11), 1603–1610 (1988)

P. Ghosh, S. Haldar, R.S. Gupta, M. Gupta, An investigation of linearity performance and intermodulation distortion of GME CGT MOSFET for RFIC design. IEEE Trans. Electron Devices 59(12), 3263–3268 (2012)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chandan, B.V., Nigam, K., Sharma, D. et al. Impact of interface trap charges on dopingless tunnel FET for enhancement of linearity characteristics. Appl. Phys. A 124, 503 (2018). https://doi.org/10.1007/s00339-018-1923-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-018-1923-8