Abstract

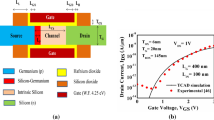

This work exclusively illustrates the impact of low-k gate oxide material on the ambipolarity of SOI-DG TFET proposed previously in literature (Goswami and Bhowmick in Silicon, https://doi.org/10.1007/s12633-019-00169-7, 2019) with a comparative AC analysis of the two TFET architectures presented here. Based upon the primary DC characterisation of the proposed device, a thorough analysis of ambipolarity, impact of varying mole fraction, influence of temperature on device characteristics are performed explicitly. For the complete RF characterisation, the transconductance, cut-off frequency, transit time, power delay product, transconductance generation efficiency and parasitic capacitances are presented in detail with a comparative summarization. The reasonably high on-current of the proposed device (orders of mA/μm) with very low leakage current floor (orders of fA/μm) makes the device suitable for low power applications as well as for high fan-out operations. The seemingly low threshold voltage with notably low VDD values (0.3 V) aids to substantial reduction of dynamic power consumption. The high cut off frequency (best reported in tera hertz) of the device opens the window for numerous diversified applications.

Similar content being viewed by others

References

P.P. Goswami, B. Bhowmick, Optimization of electrical parameters of pocket doped SOI TFET with L shaped Gate. Silicon (2019). https://doi.org/10.1007/s12633-019-00169-7

A.M. Ionescu, H. Riel, Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(7373), 329–337 (2011)

Hu C et al. Prospect of tunneling green transistor for 0.1 V CMOS. In: Proceeding of the IEEE IEDM, pp 1–4 (2010)

U.E. Avci, D.H. Morris, I.A. Young, Tunnel field-effect transistors: prospects and challenges. J. Electron. Devices Soc. (2015). https://doi.org/10.1109/jeds.2015.2390591

P.G.D. Agopian, M.D.V. Martino, S.G.D.S. Filho, J.A. Martino, R. Rooyackers, D. Leonelli, C. Claeys, Temperature impact on the tunnel fet off-state current components. Solid-State Electron. 28, 141–146 (2012)

Y. Qiu, R. Wang, Q. Huang, R. Huang, A comparative study on the impacts of interface traps on tunneling FET and MOSFET. IEEE Trans. Electron Devices 61, 1284–1291 (2014)

S. Turkane, D. Kureshi, Analysis of double gate tunneling FET characteristics for low power designs suppression. In: 2nd International Conference on Innovative Engineering Technologies, (2015)

P. Li, G. Hu, R. Liu, T. Tang, Electric potential and threshold voltage models for double-gate Schottky–Barrier source/drain Mosfets. Microelectron. J. 42, 1164–1168 (2011)

P.S. Gupta, S. Kanungo, H. Rahaman, K. Sinha, P.S. Dasgupta, An extremely low sub-threshold swing UTB SOI tunnel-FET structure suitable for low-power applications. Int. J. Appl. Phys. Math. 2(4), 240 (2012)

Z. Yang, Tunnel field-effect transistor with an L-shaped gate. IEEE Electron. Device Lett. 37, 839–842 (2016)

Q. Zhao, W. Yu, B. Zhang, M. Schmidt, S. Richter, D. Buca, J.-M. Hartmann, R. Luptak, A. Fox, K. Bourdelle, S. Mantl, Tunneling field-effect transistor with a strained si channel and a Si 0.5 Ge 0.5 source. Solid-State Electron. 74, 97–101 (2012)

Q.T. Zhao, J.M. Hartmann, S. Mantl, An improved si tunnel field effect transistor with a buried strained Si 1–x Ge x source. IEEE Electron Device Lett. 32(11), 1480–1482 (2011)

M. Schmidt, R.A. Minamisawa, S. Richter, A. Schӓfer, D. Buca, J.M. Hartmann, Q.-T. Zhao, S. Mantl, Unipolar behavior of asymmetrically doped strained Si0.5Ge0.5 tunneling field-effect transistors. Appl. Phys. Lett. 101, 123501 (2012)

J.-P. Colinge, The new generation of SOI MOSFETS. Rom. J. Inf. 11(1), 3–15 (2008)

P. Xu, H. Lou, L. Zhang, Z. Yu, X. Lin, Compact model for double-gate tunnel FETs with gate–drain underlap. IEEE Trans. Electron Devices 64(12), 5242–5248 (2017)

D.B. Abdi, M.J. Kumar, Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. J Electron Devices Soc Digit Object Identifier (2014). https://doi.org/10.1109/jeds.2014.2327626

R. Narang, M. Gupta, M. Saxena, Simulation study for dual material gate HeteroDielectric TFET: static performance analysis for analog applications. In: Annual IEEE India Conference (INDICON) (2013)

R. Goswami, B. Bhowmick, S. Baishya, Electrical noise in circular gate tunnel FET in presence of interface traps. Superlattices Microstruct (2015). https://doi.org/10.1016/j.spmi.2015.07.064

Sentaurus Device User (2009), Synopsys, 2009

C. Diaz Llorente, J.-P. Colinge, S. Martinie, S. Cristoloveanu, J. Wan, C. Le Royer, G. Ghibaudo, M. Vinet, New prospects on high on-current and steep subthreshold slope for innovative Tunnel FET architectures. Solid-State Electron. (2019). https://doi.org/10.1016/j.sse.2019.03.046

D. Esseni, M. Pala, P. Palestri, A. Cem, T. Rollo, A review of selected topics in physics based modeling for tunnel field-effect transistors. Semicond. Sci. Technol. (2017). https://doi.org/10.1088/1361-6641/aa6fca

S. Migita, K. Fukuda, Y. Morita, H. Ota, Experimental demonstration of temperature stability of Si-tunnel FET over Si-MOSFET. In: Proceedings of the Silicon Nanoelectron. Workshop, pp. 1–2 (2012)

Y.-N. Chen, M.-L. Fan, V.P. Hu, P. Su, C.-T. Chuang, Evaluation of Sub-0.2 V High-speed low-power circuits using hetero-channel MOSFET and tunneling FET devices. IEEE Trans Circ Syst I Regul Papers 61(12), 3339–3347 (2014)

A. Bhattacharjee, M. Saikiran, S. Dasgupta, A first insight to the thermal dependence of the DC, analog and RF performance of an S/D spacer engineered DG-ambipolar FET. IEEE Trans. Electron. Devices 64(10), 4327–4334 (2017)

R. Narang, M. Saxena, R.S. Gupta, M. Gupta, Impact of temperature variations on the device and circuit performance of tunnel FET: a simulation study. IEEE Trans. Nanotechnol. 12(6), 951–957 (2013)

J.S. Jang, W.Y. Choi, Ambipolarity factor of tunneling field-effect transistors (TFETs). J Semicond. Technol. Sci. 11(4), 272–277 (2011)

K.K. Bhuwalka, J. Schulze, I. Eisele, Scaling the vertical tunnel FET with tunnel bandgap modulation and gate workfunction engineering. IEEE Trans. Electron Devices 52(5), 909–917 (2005)

D.B. Abdi, M.J. Kumar, Dielectric modulated overlapping gate-on-drain tunnel-FET as a label-free biosensor. Superlattices Microstruct. (2015). https://doi.org/10.1016/j.spmi.2015.07.052

D.B. Abdi, M.J. Kumar, Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. J. Electron Device Soc. Digit. Object Identifier (2014). https://doi.org/10.1109/jeds.2014.2327626

C.K. Pandey, D. Dash, S. Chaudhury, Approach to suppress ambipolar conduction in tunnel FET using dielectric pocket. Micro & Nano Lett. 14(1), 86–90 (2019). https://doi.org/10.1049/mnl.2018.5276

S. Ahish, D. Sharma, Y.B.N. Kumar, M.H. Vasantha, Performance enhancement of novel InAs/Si hetero double-gate tunnel FET using Gaussian doping. IEEE Trans. Electron Devices 63(1), 288–295 (2016)

R.M. Imenabadi, M. Saremi, W.G. Vandenberghe, A novel PNPN-like Z-shaped tunnel field effect transistor with improved ambipolar behavior and RF performance. IEEE Trans. Electron Devices 64(11), 4752–4758 (2017)

R. Saha, B. Bhowmick, S. Baishya, Effect of Ge mole fraction on electrical parameters of Si1−xGex source step-FinFET and its application as an inverter. Silicon (2019). https://doi.org/10.1007/s12633-018-9846-8

L. Barboni, M. Siniscalchi, B. Sensale-Rodriguez, TFET-based circuit design using the transconductance generation efficiency gm/Id method. J. Electron Device Soc. Digit. Object Identifier. (2015). https://doi.org/10.1109/jeds.2015.2412118

Acknowledgements

This paper is an outcome of the R&D work undertaken in the project under the Visvesvaraya Ph.D Scheme of Ministry of Electronics & Information Technology, Government of India, being implemented by Digital India Corporation (formerly Media Lab Asia). The author offer their heartfelt gratitude to the “Microelectronics laboratory”, Dept. of Electronics and Communication Engineering, NIT Silchar to provide us with the facilities to perform our research work. We also acknowledge Dr. T.R. Lenka, Mr. Ashutosh Srivastava, Mr. Nitu Mani Rajbongshi and Mr. Bhargav Doley for their constant encouragement and motivation during the course of our research work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Goswami, P.P., Khosla, R. & Bhowmick, B. RF analysis and temperature characterization of pocket doped L-shaped gate tunnel FET. Appl. Phys. A 125, 733 (2019). https://doi.org/10.1007/s00339-019-3032-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-019-3032-8