Abstract

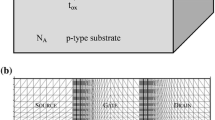

In this paper, a novel device structure called transparent gate recessed channel MOSFET (TGRC-MOSFET) is proposed to alleviate the hot carrier effects for the advanced nanometer process. TGRC-MOSFET involving a recessed channel and incorporates indium tin oxide as a transparent gate. TCAD analysis shows that the performance of TGRC-MOSFET surpasses conventional recessed channel (CRC)-MOSFET in terms of high ION/IOFF ratio and better carrier transport efficiency in comparison to CRC-MOSFET. This simulation divulges the reduction in hot-carrier-effects metrics like electron velocity, electron temperature, potential, and electron mobility. Furthermore, the effect of gate length is observed on the analog behavior of TGRC-MOSFET. All the simulations have been done using DEVEDIT-3D and ATLAS device simulator. The work proposes the novel design for reduced hot carrier and low power switching applications.

Similar content being viewed by others

References

AI-Mistarihi MF, Rjoub A, AI-Taradeh NR (2013) Drain induced barrier lowering (DIBL) accurate model for nanoscale Si-MOSFET transistor. IEEE microelectronics (ICM), 2013 25th international conference. doi:10.1109/ICM.2013.6735011

AI-Mistarihi MF, Rjoub A, AI-Taradeh NR (2013) Drain induced barrier lowering (DIBL) accurate model for nanoscale Si-MOSFET transistor. IEEE, 978-1-4799-3570-3/13. doi:10.1109/ICM.2013.6735011

Arora N (2007) MOSFET models for VLSI circuit simulation theory and practice. Springer Verlag, Wien, New York, pp 87–89. ISBN 3-211-82395-6

Chaujar R, Kaur R, Saxena M, Gupta M, Gupta RS (2008a) TCAD assessment of gate electrode workfunction engineered recessed channel (GEWE-RC) MOSFET and its multilayered gate architecture—part I: hot-carrier-reliability evaluation. IEEE Trans Electron Devices 55:2602–2612. doi:10.1109/TED.2008.2003085

Chaujar R, Kaur R, Saxena M, Gupta M, Gupta RS (2008b) GEWE-RCMOSFET: a solution to CMOS technology for RFIC design based on the concept of intercept point. International conference on microwave, IEEE, pp 661–664. doi:10.1109/AMTA.2008.4762978

Chaujar R, Kaur R, Saxena M, Gupta M, Gupta RS (2008) Solution to CMOS technology for high performance analog applications: GEWE-RCMOSFET, ACMD

Gautam R, Saxena M, Gupta RS, Gupta M (2013) Analytical model of double gate MOSFET for high sensitivity low power photosensor. J Semicond Technol Sci 13:500–510. doi:10.5573/JSTS.2013.13.5.500

Gomez L, Hashemi P, Hoyt JL (2009) Enhanced hole transport in short-channel strained-SiGe p-MOSFETs. IEEE Trans Electron Devices 56:2644–2651. doi:10.1109/TED.2009.2031043

Hajjiah AT, Huang AQ (2004) Novel SiC-Trench-MOSFET with reduced oxide electric field. IEEE, pp 340–344. doi:10.1109/PLASMA.2002.1030690

Krieger G, Sikora R, Cuevas PP, Misheloff MN (2001) Moderately doped NMOS (M-LDD)-hot electron and current drive optimization. IEEE Trans Electron Devices 38:121–127. doi:10.1109/16.65745

Long W, Ken KC (1997) Dual material gate field effect transistor (DMGFET). Electron devices meeting tech dig, pp 549–552. doi:10.1109/IEDM.1997.650445

Orouji AA, Kumar MJ (2005) Shielded channel double-gate MOSFET: a novel device for reliable nanoscale CMOS applications. IEEE Trans Device Mater Reliab 5:509–514. doi:10.1109/TDMR.2005.853505

Pammi SVN, Jung HJ, Yoon SG (2011) Low-temperature nanocluster deposition (NCD) for improvement of the structural, electrical, and optical properties of ITO thin films, pp 1059–1065. doi:10.1109/TNANO.2010.2103568

Pan Y, Ng KK, Wei CC (1994) Hot-carrier induced electron mobility and series resistance degradation in LDD NMOSFET’s. IEEE Electron Device Lett 15:499–501. doi:10.1109/55.338416

Salehi A, Gholizadeh M (2011) Selectivity enhancement of MOSFET hydrogen sensor with transparent ITO gate. IEEE Sens J 11:1201–1205. doi:10.1109/JSEN.2010.2090947

Shee S, Bhattacharyya G, Dutta PK, Sarkar SK (2014) Threshold voltage roll-off and DIBL model for DMDG SON MOSFET: a quantum study. In: Proceeding of the 2014 IEEE students’ technology symposium, pp 381–385. doi:10.1109/TechSym.2014.6808080

Shee S, Bhattacharyya G, Dutta PK, Sarkar SK (2014) Threshold voltage roll-off and DIBL model for DMDG SON MOSFET: a quantum study, pp 381–385. doi:10.1109/TechSym.2014.6808080

Thilakan P, Kumar J (1997) Studies on the preferred orientation changes and its influenced properties on ITO thin films. Vacuum 48:463–466

Torabi AJ, Joo M, Li X, Lim BS, Zhai L, Oentaryo RJ, Peen GO, Zurada JM (2013) A survey on artificial intelligence-based modeling techniques for high speed milling processes. IEEE Syst J, pp 1–12. doi:10.1109/JSYST.2013.2282479

Acknowledgments

The authors would like to gratitude to Microelectronics Research Lab, Department of Engineering Physics, Delhi Technological University to carry out this work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kumar, A., Gupta, N. & Chaujar, R. Analysis of novel transparent gate recessed channel (TGRC) MOSFET for improved analog behaviour. Microsyst Technol 22, 2665–2671 (2016). https://doi.org/10.1007/s00542-015-2554-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-015-2554-z