Abstract

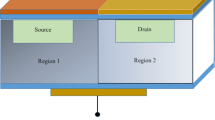

This paper proposes a 2-D investigative model for fully depleted dual-material-double-gate (DMDG) metal–oxide–semiconductor-field-effect-transistor (MOSFET) for surface potential profile. Analyses have been made with several oxide thicknesses, doping concentrations and gate voltages. The temperature effect and the interface charge density effect on the proposed surface potential model have also been reported. The different channel length ratios are also incorporated for this investigation. In this model we have also included the effect of high dielectric constant material like HfO2 and made a comparative study with the influence of different parameters. As anticipated, in DMDG structure the surface potential along the channel shows a step function which suppresses many short channel effects (SCEs). In the result the model shows that to get the same value of surface potential, the oxide thickness using HfO2 will be greater than SiO2. All the results of the analytical model outcomes have been endorsed by technology computer aided design (TCAD) simulation results. Tremendous conformity among them is observed.

Similar content being viewed by others

References

Chen X, Zhao H, Xiong Y, Wei F, Du H, Tang Z, Tang B, Yan J (2016) Study of Hf-Ti-O thin film as high-k gate dielectric and application for ETSOI MOSFETs. J Electron Mater 45:4407–4411

Choi JH, Mao Y, Chang JP (2011) Development of hafnium based high-k materials-a review. Mater Sci Eng R 72:97–136

Jelodar MS, Ilatikhameneh H, Kim S, Sarangapani P, Klimeck G (2016) Optimum high-k oxide for the best performance of ultra-scaled double-gate MOSFET. IEEE Trans Nanotechnol 15:904–910

Jossy AM, Vigneswaran T, Malarvizhi S, Nagarajan KK (2018) Characterization and modeling of dual material double gate tunnel field effect transistor using superposition approximation method. Concur Comput Pract Exp. https://doi.org/10.1002/cpe.4860

Kumar MJ, Chaudhury A (2004) Two-dimensional analytical modelling of fully depleted DMGSOIMOSFET and evidence for diminished SCEs. IEEE Trans Electron Devices 51(4):569–574

Kumar S, Goel E, Singh K, Singh B, Kumar M, Jit S (2016) A compact 2D analytical model for electrical characteristics of double-gate tunnel field-effect transistors with a SiO2/high-k stacked gate-oxide structure. IEEE Trans Electron Devices 63:3291–3299

Kumar S, Goel E, Singh K, Singh B, Singh PK, Baral K, Jit S (2017) 2-D Analytical modeling of the electrical characteristics of dual-material double-gate TFETs With a SiO2/HfO2 stacked gate-oxide structure. IEEE Trans Electron Devices 64:960–968

Long W, Ou H, Kuo JM, Chin KK (1999) Dual material gate field effect transistor. IEEE Trans Electron Devices ED-46:865–870

Maity NP, Maity R, Thapa RK, Baishya S (2014) Study of interface charge densities for ZrO2 and HfO2 based metal oxide semiconductor devices. Adv Material Sci Eng 2014:1–6

Maity NP, Maity R, Thapa RK, Baishya S (2016a) A tunneling current density model for ultra-thin HfO2 high-k dielectric material based MOS devices. Superlattices Microstruct 95:24–32

Maity NP, Thakur RR, Maity R, Thapa RK, Baishya S (2016b) Analysis of Interface charge densities for high-k dielectric materials based metal oxide semiconductor devices. Int J Nanosci 15:1660011

Maity NP, Maity R, Baishya S (2017) Voltage and oxide thickness dependent tunneling current density and tunnel resistivity model: application to high-k material HfO2 based MOS devices. Superlattices Microstruct 111:628–641

Maity NP, Maity R, Baishya S (2018) An analytical model for the surface potential and threshold voltage of a double-gate heterojunction tunnel FinFET. J Comput Electron 2018:1–11. https://doi.org/10.1007/s10825-018-1279-5

Maity NP, Maity R, Maity S, Baishya S (2019) Comparative analysis of the quantum FinFET and trigate FinFET based on modeling and simulation. J Comput Electron 2019:1–8. https://doi.org/10.1007/s10825-018-01294-z

Narang R, Saxena M, Gupta RS, Gupta M (2013) Impact of temperature variations on the device and circuit performance of tunnel FET: a simulation study. IEEE Trans Nanotechnol 12(6):951–957

Nicollian EH, Brews JR (1982) MOS (Metal Oxide Semiconductor) physics and technology. Wiley, Waco

Noor L, Safa S, Khan MZR (2016) Dual material double gate tunnel FET: gate threshold modeling and extraction. J Comput Electron 15(3):763–769

Reddy GV, Kumar MJ (2005) A new dual-material double-gate (DMDG) nanoscale SOI MOSFET-two-dimensional analytical modeling and simulation. IEEE Trans Nanotechnol 4(2):260–268

Sharma RK, Gupta RS, Gupta M (2009) Dual-material double-gate SOI n-MOSFET: gate misalignment analysis. IEEE Trans Electron Devices 56(6):1284–1291

Sharna RK, Gupta M (2011) TCAD Assessment of device design technologies for enhanced performance of nanoscale DG MOSFET. IEEE Trans Electron Devices 58:2936–2943

Shur M (1989) Split-gate-field-effect-transistor. Appl Phys Lett 54(2):162–164

Stesmans A, Afanas’ev VV (1998) Undetectability of the point defect as an interface state in thermal (100) Si/SiO2. J Phys Condens Matter 10(1):L19–L25

Vadthiya N, Tripathi S, Naik RBS (2018) A two-dimensional (2D) analytical modeling and improved short channel performance of graded channel gate stack (GCGS) dual material double gate (DMDG) MOSFET. Silicon 10(6):2399–2407

Young KK (1989) Short-channel effect in fully depleted SOI MOSFETs. IEEE Trans Electron Devices 36:399–402

Acknowledgements

The authors are highly indebted to Dept. of Electronics & Communication Engineering, National Institute of Technology, Silchar, India for technical help for this work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Chakrabarti, H., Maity, R. & Maity, N.P. Analysis of surface potential for dual-material-double-gate MOSFET based on modeling and simulation. Microsyst Technol 25, 4675–4684 (2019). https://doi.org/10.1007/s00542-019-04386-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-019-04386-3