Abstract

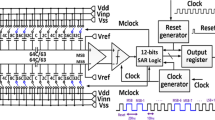

This paper presents a new very low-power, low-voltage successive approximation analog to digital converter (SAR ADC) design based on supply boosting technique. The supply boosting technique (SBT) and supply boosted (SB) circuits including level shifter, comparator, and supporting electronics are described. Supply boosting provides wide input common mode range and sub-1 Volt operation for the circuits designed in standard CMOS processes that have only high-Vt MOSFETs. A 10-bit supply boosted SAR ADC was designed and fabricated in a standard 0.5 μm, 5 V, 2P3M, CMOS process in which threshold voltages of NMOS and PMOS devices are +0.8 and −0.9 V, respectively. Fabricated SB-SAR ADC achieves effective number of bits (ENOB) of 8.04, power consumption of 147 nW with sampling rate of 1.0 KS/s on 1 Volt supply. Measured figure of merit (FOM) was 280 fJ/conversion-step. Proposed supply boosting technique improves input common mode range of both SB comparator and SAR ADC, allows sub-1 Volt operation when threshold voltages are in the order of the supply voltage, and achieves low energy operation. Thus, SBT is suitable for mixed-signal circuit designed for energy limited applications and systems in where supply voltage is in the order of threshold voltages of the process.

Similar content being viewed by others

References

Chang, L., Frank, D. J., Montoye, R. K., Koester, S. J., Ji, B. J., Coteus, P. W., et al. (2010). Practical strategies for power-efficient computing technologies. Proceedings of the IEEE, 98(2), 215–236.

Abo, A., & Gray, P. (1999). A 1.5-V. 10-bit, 14-MS/s CMOS pipeline analog-to-digital converter. IEEE Journal of Solid-State Circuits, 34, 599–606.

Duisters, T. A. F., & Dijkmans, E. C. (1998). A-90-dB THD rail-to-rail input opamp using a new local charge pump in CMOS. IEEE Journal of Solid-State Circuits, 33, 947–955.

Pierre, R. S. (2000). Low-power BiCMOS op amp with integrated current mode charge pump. IEEE Journal of Solid State Circuits, 35(7), 1046–1050.

Lotfi, R., Taherzadeh-Sani, M., Azizi, M. Y., & Shoaei, O. (2003). A 1-V MOSFET-only fully-differential dynamic comparator for use in low-voltage pipelined A/D converters. International Symposium on Signals, Circuits and Systems, (SCS), 2, 377–380.

Baschirotto, A., & Castello, R. (1997). A 1-V 1.8-MHz CMOS switched-opamp SC filter with rail-to-rail output swing. IEEE Journal of Solid-State Circuits, 32, 1979–1986.

Berg, Y., Wisland, D. T., & Lande, T. S. (1999). Ultra low-voltage/low-power digital floating-gate circuits. IEEE Transactions on Circuits and Systems I, 46, 930–936.

Blalock, B. J., Allen, P. E., & Rincon-Mora, G. A. (1998). Designing 1-V opamps using standard digital CMOS technology. IEEE Transactions on Circuits and Systems Part II: Express Briefs, 45, 769–780.

Hung, Y.-C., & Liu, B.-D. (2004). A low-voltage wide-input CMOS comparator for sensor application using back-gate technique. Biosensors and Bioelectronics, 20(1), 53–59.

Chu, W.-S., & Current, K. W. (1997). A rail-to-rail input-range CMOS voltage comparator. IEEE Midwest Symposium Circuits and Systems, (MWSCAS), 1, 160–163.

Rivoir, R., Maloberti, F. (1997). A 1mV resolution, 10MS/s rail-to-rail comparator in 0.5-μm low-voltage CMOS digital process. In IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 461–464).

Cho, T., & Gray, P. (1995). A 10 b, 20 Msample/s, 35 mW pipeline A/D converter. IEEE Journal of Solid-State Circuits, 30(3), 166–172.

Song, W., Choi, H., Kwak, S., & Song, B. (1995). A 10-b 20-Msample/s low power CMOS ADC. IEEE Journal of Solid-State Circuits, 30(5), 514–521.

Allen, P. E., & Holberg, D. R. (2002). CMOS analog circuit design (2nd ed.). Oxford: Oxford University Press.

Senderowicz, D., Nicollini, G., Pernici, S., Nagari, A., Confalonieri, P., Dallavalle, C. (1997). Low-voltage double-sampled ΣΔ converters. In IEEE International Solid-State Circuits Conference (ISSCC) (pp. 210–211, 458).

Scott, M. D., Boser, B. E., & Pister, K. S. J. (2003). An ultralow-energy ADC for smart dust. IEEE Journal of Solid-State Circuits, 38(7), 1123–1129.

Hariprasath, V., Guerber, J., Lee, S.-H., & Moon, U.-K. (2010). Merged capacitor switching based SAR ADC with highest switching energy-efficiency. Electronics Letters, 46(9), 620–621.

Liu, C.-C., Chang, S.-J., Huang, G.-Y., & Lin, Y.-Z. (2010). A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE Journal of Solid-State Circuits, 45(4), 731–740.

Craninckx, J., Plas, G. van der (2007). A 65fJ/conversion-step 0-to-50MS/s 0-to-0.7mW 9b charge-sharing SAR ADC in 90nm digital CMOS. In IEEE International Solid-State Circuits Conference (ISSCC) (pp. 246–247).

Hong, H.-C., & Lee, G.-M. (2007). A 65-fJ/conversion-step 0.9-V 200-kS/s rail-to-rail 8-bit successive approximation ADC. IEEE Journal of Solid-State Circuits, 42(10), 2161–2168.

Verma, N., & Chandrakasan, A. P. (2007). An ultra low energy 12-bit rate-resolution scalable SAR ADC for wireless sensor nodes. IEEE Journal of Solid-State Circuits, 42, 1196–1205.

Agnes, A., Bonizzoni, E., Malcovati, P., Maloberti, F. (2008). A 9.4 ENOB, 1V, 3.8μW, 100kS/s SAR-ADC with time-domain comparator. In IEEE International Solid-State Circuits Conference (ISSCC) (pp. 246–247).

Lee, S.-K., Park, S.-J., Suh, Y., Park, H.-J., Sim, J.-Y. (2009). A 1.3μW 0.6V 8.7-ENOB successive approximation ADC in a 0.18μm CMOS. In Symposium on VLSI Circuits (pp.242–243).

Lee, S.-Y., Cheng, C.-J., Wang, C.-P., Lee, S.-C. (2009). A 1-V 8-bit 0.95μW successive approximation ADC for biosignal acquisition systems. In IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 649–652).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ay, S.U. A sub-1 Volt 10-bit supply boosted SAR ADC design in standard CMOS. Analog Integr Circ Sig Process 66, 213–221 (2011). https://doi.org/10.1007/s10470-010-9515-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-010-9515-3