Abstract

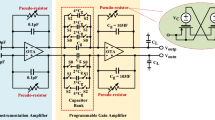

A compensation technique for low-power three-stage operational transconductance amplifiers is presented in this paper. The compensation network is made up of passive components and entails only one Miller capacitor. Design equations describing the amplifier behavior for different capacitive load conditions are reported along with three design examples for different capacitive loads, namely, 1 nF, 100 and 10 pF. The amplifier exhibits a gain-bandwidth product equal to 2.48, 6.74 and 7.66 MHz in the three cases while dissipating only 150, 150 and 57.5 μW from 2.5 V, respectively. Simulation results are found in good agreement with theoretical analysis and show an improvement in both small-signal and large-signal amplifier performance over many previously reported solutions.

Similar content being viewed by others

Notes

\(tg\left( {\alpha + \beta } \right) = \frac{{{\text{tg}}\alpha + {\text{tg}}\beta }}{{1 - {\text{tg}}\alpha \cdot {\text{tg}}\beta }}\).

References

Eschauzier, R. G. H., & Huijsing, J. H. (1992). A 100-MHz 100-dB operational amplifier with multipath nested miller compensation. IEEE Journal of Solid-State Circuits, 27(12), 1709–1716.

Eschauzier, R. G. H., & Huijsing, J. H. (1995). Frequency compensation techniques for low-power operational amplifiers. Dordrecht: Kluwer Academic.

Palumbo, G., & Pennisi, S. (2002). Feedback amplifiers: Theory and design. Berlin: Kluwer Academic Publishers.

Palumbo, G., & Pennisi, S. (2002). Design methodology and advances in nested-miller compensation. IEEE Transactions on Circuits and Systems Part I, 49(7), 893–903.

Mita, R., Palumbo, G., & Pennisi, S. (2003). Design guidelines for reversed nested miller compensation in three-stage amplifiers. IEEE Transactions on Circuits and Systems part II, 50, 227–233.

Peng, X., & Sansen, W. (2005). Transconductance with capacitances feedback compensation for multistage amplifiers. IEEE Journal of Solid-State Circuits, 40(7), 1515–1520.

Grasso, A. D., Palumbo, G., & Pennisi, S. (2006). Three-stage CMOS OTA for large capacitive loads with efficient frequency compensation scheme. IEEE Transactions on Circuits and Systems part II, 53(10), 1044–1048.

Grasso, A. D., Marano, D., Palumbo, G., & Pennisi, S. (2007). Improved reversed nested miller compensation technique with voltage buffer and nulling resistor. IEEE Transactions on Circuits and Systems part II, 54(5), 382–386.

Grasso, A. D., Palumbo, G., & Pennisi, S. (2008). Analytical comparison of frequency compensation techniques in three-stage amplifiers. International Journal of Circuit Theory and Applications, 36(1), 53–80.

Grasso, A. D., Marano, D., Palumbo, G., & Pennisi, S. (2010). Analytical comparison of reversed nested miller frequency compensation techniques. International Journal of Circuit Theory and Applications, 38(7), 709–737.

Grasso, A. D., Palumbo, G., & Pennisi, S. (2007). Advances in reversed nested miller compensation. IEEE Transactions on Circuits and Systems part I, 54(7), 1459–1470.

Mohan, C., & Furth, P. M. (2012). A 16-Ω audio amplifier with 93.8-mW peak load power and 1.43-mW quiescent power consumption. IEEE Transactions on Circuits and Systems part II, 59(3), 133–137.

Guo, S., & Lee, H. (2011). Dual active-capacitive-feedback compensation for low-power large-capacitive-load three-stage amplifiers. IEEE Journal of Solid-State Circuits, 46(2), 452–464.

Cannizzaro, S. O., Grasso, A. D., Palumbo, G., & Pennisi, S. (2008). Single miller capacitor compensation with nulling resistor. International Journal of Circuit Theory and Applications, 36(7), 825–837.

Fan, X., Mishra, C., & Sanchez-Sinencio, E. (2005). Single miller capacitor frequency compensation technique for low-power multistage amplifiers. IEEE Journal of Solid-State Circuits, 40(3), 584–592.

Leung, K. N., Mok, P. K. T., Ki, W. H., & Sin, J. K. O. (2000). Three-stage large capacitive load amplifier with damping-factor-control frequency compensation. IEEE Journal of Solid-State Circuits, 35, 221–230.

Peng, X., Sansen, W., Hou, L., Wang, J., & Wu, W. (2011). Impedance adapting compensation for low-power multistage amplifiers. IEEE Journal of Solid-State Circuits, 46(2), 445–451.

Tan, M., & Ki, W.-H. (2015). A cascode miller-compensated three-stage amplifier with local impedance attenuation for optimized complex-pole control. IEEE Journal of Solid-State Circuits, 50(2), 440–449.

Yan, Z., Mak, P.-I., Lau, M.-K., & Martins, R. P. (2013). A 0.016-mm 144-µW three-stage amplifier capable of driving 1-to-15nF capacitive load with 0.95-MHz GBW. IEEE Journal of Solid-State Circuits, 48(2), 527–540.

Chong, S. S., & Chan, P. K. (2012). Cross feedforward cascode compensation for low-power three-stage amplifier with large capacitive load. IEEE Journal of Solid-State Circuits, 47(9), 2227–2234.

Marano, D., Palumbo, G., & Pennisi, S. (2010). Step-response optimization techniques for low-power, high-load, three-stage operational amplifiers driving large capacitive loads. IET Journal of Circuits, Devices and Systems, 4(2), 87–98.

Palmisano, G., Palumbo, G., & Pennisi, S. (2001). Design procedures for two-stage CMOS OTAs: A tutorial. Analog Integrated Circuits and Signal Processing, 27(3), 179–189.

Cannizzaro, S. O., Grasso, A. D., Mita, R., Palumbo, G., & Pennisi, S. (2007). Design procedures for three-stage CMOS OTAs with nested-miller compensation. IEEE Transactions on Circuits and Systems part I, 54(5), 933–940.

Lewyn, L. L., Ytterdal, T., Wulff, C., & Martin, K. (2009). Analog circuit design in nanoscale CMOS technologies. Proceedings of IEEE, 97(10), 1687–1714.

Grasso, A. D., Palumbo, G., & Pennisi, S. (2015). High-performance four-stage CMOS OTA suitable for large capacitive loads. IEEE Transactions on Circuits and Systems part I, 62(10), 2476–2487.

Author information

Authors and Affiliations

Corresponding author

Appendix

Appendix

The useful simplification from general complex and conjugate poles \(1 + a'_{2} s + a'_{3} s\) into two separate poles in (22) with (23) and (24) causes an error in the coefficient of s term, due to the term

Indeed, considering the relationship

into (25) we can write

which rearranged yields

Comparing (37) with the corresponding equation resulting from (19), we find the term \(g_{m1} R_{a}^{*} C_{o2}\) in the round bracket of the C m coefficient of (37). This is the term introduces an error that is negligible under the case of two separate poles (i.e., \(C_{L} /C_{o2} > g_{m2} g_{m3} R_{a}^{*2}\)).

Rights and permissions

About this article

Cite this article

Di Cataldo, G., Grasso, A.D., Palumbo, G. et al. Improved single-miller passive compensation network for three-stage CMOS OTAs. Analog Integr Circ Sig Process 86, 417–427 (2016). https://doi.org/10.1007/s10470-016-0696-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0696-2