Abstract

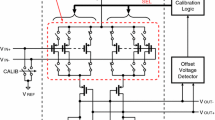

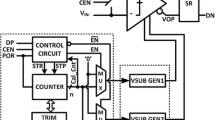

A fully differential latched comparator using a new offset cancellation technique is presented. The comparator consists of three stages: the input pre-amplifier, a positive feedback or latch stage and the offset cancellation circuitry. The effect of kick-back noise can be significantly reduced by using a pre-amplifier stage. Also, the offset and noise of the latch and offset cancellation stages are attenuated by the gain of the pre-amplifier when referred to the input. Latches regenerate faster than pre-amplifiers and provide a full swing digital output for the comparator. The last stage is the offset cancellation circuitry. The main advantage of the proposed offset cancellation technique is that it does not need to make any interrupt in normal operation of comparator to eliminate offset error. As a result, higher speeds for the comparator can be achieved. Moreover, the power consumption of the proposed offset cancellation circuitry is negligible compared to the overall power consumption. In order to evaluate the performance of the comparator, simulations are performed in a 0.18 μm standard CMOS technology. Simulation results show that the offset values of the pre-amplifier and latch stages are significantly eliminated by this cancellation technique and only about 450 μV offset voltage will be referred to the input due to offset error of the offset cancellation circuitry. The proposed comparator operates at 500 MHz clock frequency and dissipates 373 μW from a 1.8 supply. Also, it has a propagation delay of 138 ps and kick-back noise of 0.54 mV.

Similar content being viewed by others

References

Shih, T., Der, L., Lewis, S. H., & Hurst, P. J. (1997). A fully differential comparator using a switched-capacitor differencing circuit with common-mode rejection. IEEE Journal of Solid-State Circuits, 32(2), 250–253.

Lei, K. M., Mak, P. I., & Martins, R. P. (2013). Systematic analysis and cancellation of kick-back noise in a dynamic latched comparator. Analog Integrated Circuits and Signal Processing, 77(2), 277–284.

Wong, K. L. J. (2002). Comparison of digital offset compensation in comparators. Master of Science thesis, University of California.

Brenneman, C. (2010). Circuit design for realization of a 16 bit 1 MS/s successive approximation register analog-to-digital converter. Master of Science thesis, Worcester Polytechnic Institute.

Lu, J., & Holleman, J. (2013). A low-power high-precision comparator with time-domain bulk-tuned offset cancellation. IEEE Transactions on Circuits and Systems I: Regular Papers, 60(5), 1158–1167.

Jeon, H. J., & Kim, Y. B. (2012). A novel low-power, low-offset, and high-speed CMOS dynamic latched comparator. Analog Integrated Circuits and Signal Processing, 77(3), 337–346.

He, J., Zhan, S., Chen, D., & Geiger, R. L. (2009). Analyses of static and dynamic random offset voltages in dynamic comparators. IEEE Transactions on Circuits and Systems I: Regular Papers, 56(5), 911–919.

Nikoozadeh, A., & Murmann, B. (2006). An analysis of latch comparator offset due to load capacitor mismatch. IEEE Transactions on Circuits and Systems II: Express Briefs, 12(53), 1398–1402.

Razavi, Behzad. (2001). Design of analog CMOS integrated circuits. New York: Mcgraw-Hill.

Mashhadi, S. B., & Lotfi, R. (2012). An offset cancellation technique for comparators using body-voltage trimming. Analog Integrated Circuits and Signal Processing, 73(3), 673–682.

Jeon, H. J., & Kim, Y. B. (2011). Offset voltage analysis of dynamic latched comparator. In IEEE 54th international midwest symposium on circuits and systems (MWSCAS) (pp. 1–4).

Jeon, H. J., & Kim, Y. B. (2010). A low-offset high-speed double-tail dual-rail dynamic latched comparator, In Proceedings of the 20th symposium on Great lakes symposium on VLSI (pp. 45–48).

Degerli, Y., Fourches, N., Rouger, M., & Lutz, P. (2003). Low-power auto zeroed high-speed comparator for the readout chain of a CMOS monolithic active pixel sensor based vertex detector. IEEE Transactions on Nuclear Science, 50(5), 1709–1717.

Haddad, S. A. P., & Nascimento, I. (2011). A high-speed low-power CMOS comparator using auto-zero offset cancellation technique. In Proceedings of the 24th symposium on integrated circuits and systems design (pp. 35–38).

Fayed, A., & Ismail, M. (2003). A high-speed low-voltage CMOS offset comparator. Analog Integrated Circuits and Signal Processing, 36(3), 267–272.

Zumbahlen, H. (2008). Linear circuit design handbook. Norwood: Analog Devices.

Ahmed, Imran. (2010). Pipelined ADC design and enhancement techniques. Berlin: Springer.

Khorami, A., & Sharifkhani, M. (2016). High-speed low-power comparator for analog to digital converters. AEU-International Journal of Electronics and Communications, 70(7), 886–894.

Achigui, H. J., Fayomi, C., Massicotte, D., & Boukadouma, M. (2011). Low-voltage, high-speed CMOS analog latched voltage comparator using the flipped voltage follower as input stage. Microelectronics Journal, 42(5), 785–789.

Sadeghipour, K. D. (2011). An improved low offset latch comparator for high-speed ADCs. Analog Integrated Circuits and Signal Processing, 66(2), 205–212.

Khanghah, M. M., & Sadeghipour, K. D. (2014). A 0.5 V offset cancelled latch comparator in standard 0.18 μm CMOS process. Analog Integrated Circuits and Signal Processing, 66(2), 161–169.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Naghavi, S., Sharifi, N., Nematzadeh, M. et al. A 500 MHz low offset fully differential latched comparator. Analog Integr Circ Sig Process 92, 233–245 (2017). https://doi.org/10.1007/s10470-017-0998-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-017-0998-z