Abstract

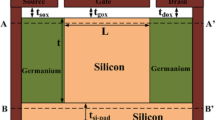

This paper reports studies of a doping-less tunnel field-effect transistor (TFET) with a \(\hbox {Si}_{0.55} \hbox {Ge}_{0.45}\) source structure aimed at improving the performance of charge-plasma-based doping-less TFETs. The proposed device achieves an improved ON-state current (\(I_{{\mathrm{ON}}} \sim {4.88} \times {10}^{-5}\,{\mathrm{A}}/\upmu {\mathrm{m}}\)), an \(I_\mathrm{ON}/I_\mathrm{OFF}\) ratio of \({6.91} \times {10}^{12}\), an average subthreshold slope (\(\hbox {AV-SS}\)) of \(\sim \) \({64.79}\,{\mathrm{mV/dec}}\), and a point subthreshold slope (SS) of 14.95 mV/dec. This paper compares the analog and radio of frequency (RF) parameters of this device with those of a conventional doping-less TFET (DLTFET), including the transconductance (\(g_{{\mathrm{m}}}\)), transconductance-to-drain-current ratio \((g_\mathrm{m}/I_\mathrm{D})\), output conductance \((g_\mathrm{d})\), intrinsic gain (\(A_{{\mathrm{V}}}\)), early voltage (\(V_{{\mathrm{EA}}}\)), total gate capacitance (\( C_{{\mathrm{gg}}}\)), and unity-gain frequency (\(f_{{\mathrm{T}}}\)). Based on the simulated results, the \(\hbox {Si}_{0.55}\hbox {Ge}_{0.45}\)-source DLTFET is found to offer superior analog as well as RF performance.

Similar content being viewed by others

References

Bhuwalka, K.K., Schulze, J., Eisele, I.: Performance Enhancement of Vertical Tunnel Field-Effect Transistor with SiGe in the \(\delta \)p+ layer. Jpn. J. Appl. Phys. 43(7A), 4073–4078 (2004)

Ionescu, A.M., Riel, H.: Tunnel Field-Effect Transistors as Energy Efficient Electronic Switches. Nature 479(7373), 329–337 (2011)

Bhuwalka, K.K., Schulze, J., Eisele, I.: Scaling the vertical Tunnel FET with Tunnel Bandgap Modulation and Gate Work Function Engineering. IEEE Trans. Electron Devices 52(5), 909–917 (2005)

Choi, W.Y., Park, B.G., Lee, J.D.: Tunneling Field-Effect Transistors (TFETs) with Subthreshold Swing (SS) less than 60 mV/dec. IEEE Electron Device Letters 28(8), 743–745 (2007)

Colinge, J.-P., Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O’Neill, B., Blake, A., White, M., Kelleher, A.M., McCarthy, B., Murphy, R.: Nanowire Transistors without Junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Aydin, C., Zaslavsky, A., Luryi, S., Cristoloveanu, S., Mariolle, D., Fraboulet, D., et al.: Lateral Interband Tunneling Transistor in Silicon-on-Insulator. Appl. Phys. Lett. 84(10), 1780–1782 (2004)

Koswatta, S.O., Lundstrom, M.S., Nikonov, D.E.: Performance Comparison between P-I-N Tunneling Transistors and conventional MOSFETs. IEEE Trans Electron Devices 56(3), 456–465 (2009)

Boucart, K., Ionescu, A.M.: Double Gate Tunnel FET with High-K Gate Dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

Lou, H., Lining, Zhang, Yunxi, Zhu, Xinnan, Lin, Shengqi, Yang, Jin, He, Chan, M.: A Junctionless Nanowire Transistor With a Dual-Material Gate. IEEE Transaction on Electron Devices 59(7), 1829–1836 (2012)

Beneventi, G.B., Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: Dual-Metal-Gate InAs Tunnel FET with Enhanced Turn-On Steepness and High On-Current. IEEE Transactions on Electron Devices 61(3), 776–784 (2014)

Narang, Rakh, Saxena, Manoj, Gupta, Gupta, R.S., Mridula, Gupta: Effect of Temperature and Gate Stack on the Linearity and Analog Performance of Double Gate Tunnel FET, pp. 466–475. Springer Berlin Heidelberg, 197, (2011)

Zhao, Q.T., Hartmann, J.-M., Mantl, S.: An Improved Si Tunnel Field Effect Transistor with a Buried Strained Si\(_{1-x}\)Ge\(_{x}\) Source. Electron Device Letters, IEEE 32(11), 1480–1482 (2011)

Wang, Pei-Yu., Tsui, Bing-Yue: Si1-xGex Epitaxial Tunnel Layer Structure for P-Channel Tunnel FET Improvement. IEEE Transaction on Electron Devices 60(12), 4098–4104 (2013)

Damrongplasit, N., Kim’, S.H., Liu, T.J.K.: Study of Random Dopant Fluctuation Induced Variability in the raised-Ge-Source TFET. IEEE Electron Device Lett 34(2), 184–186 (2013)

Rajasekharan, B., Hueting, R.J.E., Salm, C., van Hemert, T., Wolters, R.A.M., Schmitz, J.: Fabrication and Characterization of the Charge-Plasma Diode. IEEE Electron Device Letters 31(6), 528–530 (2010)

Anand, Sunny, Intekhab Amin, S., Sarin, R.K.: Analog Performance Investigation of Dual Electrode Based Doping-Less Tunnel FET”. Journal of Computational Electronics 15(1), 94–103 (2016)

Jagadesh Kumar, M.: Doping-Less Tunnel Field Effect Transistor: Design and Investigation. IEEE Transactions on Electron Devices 60(10), 3285–3290 (2013)

Sunny, anand, Intekhab Amin, S., Sarin, R.K.: Performance Analysis of Charge Plasma based Dual Electrode Tunnel FET. Journal of semiconductors 37(5), 054003-1-8 (2016)

Sunny, Anand, Sarin, R.K.: An Analysis on Ambipolar Reduction Techniques for Charge Plasma Based Tunnel FETs. Journal of Nanoelectronics and Optoelectronics 11(4), 543–550 (2016)

Walke, A.M., Vandooren, A., Rooyackers, R., Leonelli, D., Hikavyy, A., Loo, R., Verhulst, A.S., Ka, Kuo-Hsing, Huyghebaert, C., Groeseneken, G., Rao, V.R., Bhuwalka, K.K., Heyns, M.M., Collaert, N., Thean, A.V.-Y.: Fabrication and Analysis of a Si/Si\(_{0.55 }\)Ge\(_{0.45}\) Heterojunction Line Tunnel FET. IEEE Transactions on Electron Devices 61(3), 707–715 (2014)

ATLAS Device Simulation Software: Silvaco Int. Santa Clara, CA, USA (2012)

Omura, Y., Horiguchi, S., Tabe, M., Kishi, K., et al.: Quantum-mechanical effects on the threshold voltage of ultrathin-SOI nMOSFETs. IEEE Trans. Electron Devices 14(12), 569 (1993)

Kilchytska, V., Neve, A., Vancaillie, L., Levacq, D., Adriaensen, S., van Meer, H., de Meyer, K., Raynaud, C., Dehan, M., Raskin, J.P., Flandre, D.: Influence of Device Engineering on The Analog and RF of SOI MOSFETs. IEEE Transactions on Electron Devices 50(3), 577–588 (2003)

Patel, Nayan, Ramesha, A., Mahapatra, Santanu: Drive current boosting of n-type tunnel FET with strained SiGe layer at source. Microelectronics Journal 39, 1671–1677 (2008)

Mookerjea, S., Krishnan, R., Datta, S., Narayanan, V.: Effective Capacitance and Drive Current for Tunnel FET (TFET) CV/I Estimation. IEEE Transactions on Electron Devices 56(9), 2092–2098 (2009)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Anand, S., Sarin, R.K. Analog and RF performance of doping-less tunnel FETs with \(\hbox {Si}_{0.55} \hbox {Ge}_{0.45}\) source. J Comput Electron 15, 850–856 (2016). https://doi.org/10.1007/s10825-016-0859-5

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-016-0859-5