Abstract

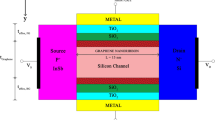

In this article, the electrical behavior of laterally grown novel short-channel III–V/Si heterostructure double gate triple material PiN tunneling graphene nanoribbon field effect transistor (DG-TM-PiN-TGNFET) has been studied based on their quantum mechanical effect (QME). Firstly, by varying the device process parameters of the novel TFET structure, the DC parameter responses viz. threshold voltage, electric field and surface potential are investigated. Further these responses are analyzed by considering the QME for better device performance. Two-dimensional numerical device simulator (SILVACO TCAD) tool is used for simulating the quantum and semi-classical models. The simulation work has been validated by extensive analytical modeling, that reflected in our accurate graphical representations. Finally, to investigate the QME effect in circuit level applications, an TFET inverter circuit has been designed and its DC performance viz. power dissipation and propagation delay analysis is performed.

Similar content being viewed by others

References

Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(7373), 329–337 (2011)

Koswatta, S.O., Lundstrom, M.S., Nikonov, D.E.: Performance comparison between p-i-n tunneling transistors and conventional MOSFETs. IEEE Trans. Electron. Devices 56(3), 456–465 (2009)

Seabaugh, A.C., Zhang, Q.: Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98(12), 2095–2110 (2010)

Choi, W.Y., Park, B.-G., Lee, J.D., Liu, T.-J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

Thomas, N., Philip Wong, H.S.: The end of Moore’s Law: a new beginning for information technology. IEEE J. Comput. Sci. Eng. 19(2), 41–50 (2017)

Dutta, R., Konar, S.C., Paitya, N.: Influence of gate and channel engineering on multigate tunnel FETs: a review. In: Maharatna, K., Kanjilal, M., Konar, S., Nandi, S., Das, K. (eds.) Computational advancement in communication circuits and systems. Lecture notes in electrical engineering, vol. 575. Springer, Heidelberg (2020)

Madan, J., Gupta, R.S., Chaujar, R.: Mathematical modeling insight of hetero gate dielectric-dual material gate-GAA-tunnel FET for VLSI/analog applications. Microsyst. Technol. 23(9), 4091–4098 (2017)

Bardon, M.G., Neves, H.P., Puers, R., Van Hoof, C.: Pseudo two- dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans. Electron. Devices 57(4), 827–834 (2010)

Madan, J., Gupta, R.S., Chaujar, R.: Performance investigation of heterogeneous gate dielectric-gate metal engineered–gate all around-tunnel FET for RF applications. Microsyst Technol 23, 4081–4090 (2017)

Dutta, R., Paitya, N.: Electrical characteristics assessmenton heterojunction tunnel FET (HTFET) by optimizing various high-κ materials: HfO2/ZrO2. Int. J. Innov. Technol. Explor. Eng. 8(10), 393–396 (2019)

Verhulst, A.S., Soree, B., Leonelli, D., Vandenberghe, W.G., Groeseneken, G.: Modeling the single-gate, doublegate, and gate all-around tunnel field-effect transistor. J. Appl. Phys. 107(2), 024518 (2010)

Alper, C., Palestri, P., Lattanzio, L., Padilla, L. J., Ionescu, A.M.: Two dimensional quantum mechanical simulation of low dimensional tunneling devices. In: 2014 44th European solid state device research conference (ESSDERC), pp. 186–189 (2014)

Wu, J., Min, J., Taur, Y.: Short-channel effects in tunnel FETs. IEEE Trans. Electron Dev. 62(9), 3019–3024 (2015). https://doi.org/10.1109/ted.2015.2458977

Dutta, R., Paitya, N., Subash, T.D.: Electric field and surface potential analytical modeling of novel double gate triple material PiN tunneling graphene nano ribbon FET (DG-TM-PiN-TGNFET). Silicon (2020). https://doi.org/10.1007/s12633-020-00474-6

Chien, N.D., et al.: Dependence of short-channel effects on semiconductor bandgap in tunnel field-effect transistors. J Phys Conf Ser 1034, 012003 (2014)

Dutta, R., Subash, T.D., Paitya, N.: InAs/Si hetero-junction channel to enhance the performance of dg-tfet with graphene nanoribbon: an analytical model. Silicon (2020). https://doi.org/10.1007/s12633-020-00546-7

Vimala, P., Arun Samuel, T.S., Nirmal, D., Panda, A.K.: Performance enhancement of triple material double gate TFET with heterojunction and heterodielectric. Solid State Electron. Lett. 1, 64–72 (2019)

TCAD Atlas Manual, Silvaco, Inc., CA 95054, USA (2015)

Cappy, A., et al.: Comparative potential performance of Si, GaAs, GaInAs, InAs submicrometer-gate FET’s. IEEE Trans. Electron Devices ED27(11), 2158–2160 (1980)

Arora, N.D., Hauser, J.R., Roulston, D.J., et al.: Electron and hole mobilities in silicon as a function of concentration and temperature. IEEE Trans. Electron Devices 29(2), 292–295 (1982)

Fossum, J.G., Lee, D.S., et al.: A physical model for the dependence of carrier lifetime on doping density in nondegenerate silicon. Solid State Electron 25, 741–747 (1982)

Richter, S., Trellenkamp, S., Schäfer, A., Hartmann, J.M., Bourdelle, K., Zhao, Q.T., Mantl, S.: Improved tunnel-FET inverter performance with SiGe/Si heterostructure nanowire TFETs by reduction of ambipolarity. Solid State Electron. 108, 97–103 (2015). https://doi.org/10.1016/j.sse.2015.02.018

Richter, S., Trellenkamp, S., Schafer, A., Hartmann, J.M., Bourdelle, K.K., Zhao, Q.T., Mantl, S.: Tunnel-FET inverters for ultra-low power logic with supply voltage down to VDD = 0.2 V. In: 2014 15th international conference on ultimate integration on silicon (ULIS), 2014.

Kwon, D.W., Kim, H.W., Kim, J.H., Park, E., Lee, J., Kim, W.: Effects of localized body doping on switching characteristics of tunnel FET inverters with vertical structures. IEEE Trans. Electron Devices 64(4), 1799–1805 (2017)

Acknowledgement

This work was supported by All India Council for Technical Education (AICTE), Govt. of India, under Research Promotion Scheme through the Grant: 8-139/RIFD/RPS-NER/Policy-1/2018-19. Special acknowledgement also goes to Dr. Nitai Paitya for facilitating the authors with Nanoelectronics Lab, Sikkim Manipal Institute of Technology (SMIT)-Sikkim, India, for this research work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Dutta, R., Subash, T.D. & Paitya, N. DC performance analysis of III–V/Si heterostructure double gate triple material PiN tunneling graphene nanoribbon FET circuits with quantum mechanical effects. J Comput Electron 20, 855–863 (2021). https://doi.org/10.1007/s10825-020-01649-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01649-5