Abstract

Interconnections in semiconductor devices need to provide a seamless electrical, thermal, and mechanical link to different parts of the circuit. Since the move away from lead-based solders due to toxicity concerns, the search has been on for materials that can provide desirable attributes before, during, and after bonding. While lead-free solders have been extensively used as a replacement, they are now reaching their limits in terms of pitch scaling, as well as, electrical and thermal properties, forcing the semiconductor industry to look for alternative material systems for the next interconnection node. This review provides an overview of key properties needed in metal interconnections and possible use of nanoporous metals due to ease of fabrication, nanostructured ligaments, and other key physical attributes.

Similar content being viewed by others

Introduction

Nanoporous (NP) metals are part of a broader category of porous media or metal–air composites that can extend the range of properties and therefore applications of the parent (solid wall) material.1 The solid mass fraction (or relative density) for NP metals is typically greater that 30%2,3,4,5,6,7,–8 with open-cell structure, formed by a random arrangement of nanosized ligaments and junctions through the volume. Abundant information exists on the physical properties of porous media with ligaments and porosities in the micron or above range,9 but several modifications are necessary for NP metals due to their higher relative density3 and the interplay of nanosized ligament properties, which can substantially influence their overall physical properties; For example, NP metals have been reported to have different scalings of strength4,5,10,11,12,–13 and stiffness3 than expected. NP metals, with their open-cell structure, bicontinuous porosity, and resulting high surface-to-volume ratio, have been proposed as catalysts,14,15,–16 sensors,17,18,–19 actuators,18,20 radiation-resistant coatings,21 and optical22 or lipid bilayer platforms.23

This review discusses the favorable attributes of NP metals (and NP copper in particular) that make them promising interconnection materials for power electronics and microelectronics applications.24,25,–26 In power electronics, nanoporous copper is proposed as a low-cost alternative to Ag sintering for die-attach interconnections, with a drastic reduction in organic volatile content, superior design flexibility for control of bondline thickness and stress management, and improved manufacturability. In microelectronics, NP copper can be used as low-modulus capping on top of a copper pillar to improve manufacturability, of direct Cu-Cu bonding particular tolerance to non-coplanarities and warpage, while still retaining pitch scalability, owing to their solid state.

Fundamentals of Interconnections and Assembly

Electronic systems are made of multiple interconnected semiconductor devices and passive components to realize their electronic functions. Most leading-edge active components contain billions of transistors or bits, so they need to be connected to other parts of the system, such as other integrated circuits, as in multichip modules for digital systems with high data rates, or to passive components to form functional circuits such as radiofrequency (RF) or power modules. Thus, for the system to function, all 100 or so components need to be interconnected, powered, cooled, and protected. These components are interconnected on package substrates such as printed circuit boards (PCBs) with several copper wiring layers. Interconnections are the physical links that electrically, mechanically, and thermally connect different levels of packaging, such as semiconductor chips to substrates, as shown schematically in Fig. 1. Assembly refers to the process by which these interconnections are formed.

While the primary function of interconnections is electrical, this can only be achieved by using materials and processing techniques that feature appropriate mechanical, electrical, and thermal properties. Thus, three key considerations are: (a) interconnection materials with the required electrical, thermal, and mechanical properties, (b) processing of these materials to form electrical joints (i.e., assembly), and (c) mechanical aspects such as stresses and strains that develop in these joints due to thermal expansion mismatch between active devices, e.g., Si, GaAs, SiGe, GaN or SiC devices with coefficient of thermal expansion (CTE) between 3 ppm/K and 6 ppm/K and package substrates and organic boards with CTEs ranging from 3 ppm/K to 17 ppm/K.

Interconnections have three primary functions: (1) electrical: to provide a path for signal and power distribution in the packaged system; (2) mechanical: to provide mechanical reliability of the interconnected system; and (3) thermal: to provide a heat transfer path to efficiently dissipate the heat generated in the semiconductor devices through the substrate. Interconnections, therefore, play a critical role at chip, package, and board levels for the system’s overall performance and have to be carefully designed, taking into account material, geometry, processing, and manufacturability considerations. Ideal properties of an interconnection system can be defined as follows:

-

Electrical: Resistance, capacitance, and inductance are important properties of any interconnection technology. To achieve the highest signal transmission speed at low loss and low power and maintain signal integrity, the resistance, capacitance, and inductance of the interconnections need to be minimized. The amount of current that can be passed through an interconnection is fundamentally limited by the interconnection material and geometry. Excessive current densities can create failures in interconnections by electromigration.27,28

-

Thermal: Interconnections also serve as thermal interfaces to transfer heat between semiconductor devices and the package substrate. Heat is generated within chips as they operate, due to intrinsic power losses. Efficient removal of this heat through the substrate is critical for maintaining a reasonable temperature in the semiconductor, particularly in analog and power applications. Interconnections provide the necessary heat transfer path between devices and substrate, and high-thermal-conductivity materials are highly desirable. Metals and alloys, with both high electrical and thermal conductivities, therefore represent ideal candidate materials for interconnections.

-

Mechanical: The mechanical behavior of an interconnection is important because its potential failure can result in electrical failure. The interconnection materials and their temperature dependence are critical parameters as they directly impact on the reliability of the interconnections. Young’s modulus and yield strength are two critical properties that affect both themomechanical fatigue and drop performance. Thermomechanical reliability is governed by the ability of the interconnection material to prevent plastic deformation, therefore benefitting from higher modulus and yield strength values. On the contrary, drop performance relies on the ability of the interconnection material to absorb shock energy, necessitating more compliant (lower-modulus) materials.

-

Reliability: As electronic systems make their way into every part of our lives, from communication and computing systems to self-driving cars and more electric aircrafts, reliability and safety have become of utmost concern. Failures of mobile phones or laptops may be inconvenient, but malfunction of onboard electronic systems, for instance, in high-speed trains, electric cars or planes, can endanger lives. Electronic systems with poor reliability fail to perform their intended function and often require additional maintenance over the product life, which increases cost. Any electronic product is expected to perform reliably, sometimes in harsh environments, for its normal duration of use, which varies greatly from product to product.

Electronic systems must satisfy stringent and sometimes conflicting requirements for performance and reliability. Interconnections play a critical role in achieving high reliability. Interconnection materials and geometries must, therefore, be carefully selected to minimize mechanical stresses and strains induced, for example, by expansion mismatch that can cumulatively lead to catastrophic failure of the product.

Assembly is the process by which interconnections are formed, primarily through a metallurgical bond joining two metal interfaces. Metallurgical or metallic bonding relies on self- or inter- diffusion between metal interfaces. A metallurgical bond is formed between two interfaces made either of the same metal or of two or more different metals. When the two interfaces are made of the same metal, the metallurgical bond is formed through self-diffusion, resulting in a seamless bonded interface. When the two interfaces are made of two or more different metals, the metallurgical bond is formed through interdiffusion, resulting in formation of intermetallic compounds at the bonded interface based on the phase diagram of the reacting metals.

The reaction occurring during metallurgical bonding is enabled by the motion (transport) of atoms of one metal into another, provided external energy is brought into the system to overcome the energy barrier to diffusion, Ea, following an Arrhenius equation: \( D = D_{0} {\text{e}}^{{\left( {\frac{{ - E_{\text{a}} }}{RT}} \right)}} \), where R is the universal gas constant equal to 8.314 J/mol K, T is the temperature in K, and D0 is the initial diffusivity value of the diffusing metal in the base metal in m2/s. Atomic contact between the two metal interfaces to be bonded is required to achieve diffusion. While surface roughness, non-coplanarities, and oxidation tend to increase the energy barrier to diffusion, external application of heat, pressure, or ultrasonic energy can be used to reduce it. Diffusivity tends to increase with temperature, reaching its peak as the diffusing metals change phase and become liquid. Heat is typically applied to achieve metallurgical bonding, and metals and alloys with relatively low melting point Tm are preferred to form metallic bonds in the shortest time. The bonding time directly impacts the throughput of the process in units per hour (UPH), which in turn affects cost. Bonding parameters such as time, temperature, and applied pressure are critical factors in the development of a suitable assembly process respecting the thermal budget and throughput required by the product and application. These considerations are summarized in Fig. 2 as guidelines for selection of materials with desired properties during initial, assembly, and operating conditions. As can be seen, any new process should be compatible with existing lithography protocols. During assembly, interconnection materials need to have low to moderate compliance, but the end product needs to have low electrical resistivity, high thermal conductivity, and stability as close as possible to high-melting-point, dense (bulk) metals.

Interconnection Materials and Technology Overview

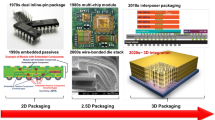

Based on these considerations, tin-lead solders with a variety of compositions having Pb content from 37% to 95% were used prolifically in industry due to their ease of fabrication, relatively low melting point (in particular, 183°C for the eutectic composition), and outstanding reliability performance during operation.29,30,31,32,33,–34 However, concerns over the toxicity of lead led to a worldwide ban of its use in electronics packaging. Tin-based lead-free alloys made of mixtures of Sn, Cu, and Ag, e.g., SnCu0.7 or SnAg3.5, were widely adopted as a replacement technology, despite their slightly higher melting points in the range of 220–230°C and slightly worse thermomechanical properties compared with leaded solders.34,35,–36 Solder-based interconnections using lead-free solders have become a near-universal solution for assembly of a wide-range of electronic systems, including digital, analog, and power devices, owing to their: (1) self-alignment capability through surface tension in molten phase, (2) low-temperature assembly at less than 250°C, and (3) corrosion resistance, among other benefits. Two types of interconnections have been pursued in parallel, as described in Fig. 3: bumped interconnections defined by their pitch, i.e., the distance between the centers of interconnections, for (digital, analog, and low-power) microelectronics applications, and large-area interconnections in power electronics.

High-performance computing has been driving advances in interconnection technologies from the digital side, to scale interconnection pitches following the transistor scaling trend governed by Moore’s law. Pitch scaling is accompanied by a necessary reduction in solder volume to prevent solder bridging and, subsequently, in the interconnection standoff height. This aggravates mechanical stresses and strains in the solder joints, resulting in reliability concerns and limiting further scaling of traditional solder bump interconnections.37 The next-generation technology, referred to as Cu pillar interconnection technology, shown in Fig. 4, was introduced in the 1990s for further pitch scaling. In this approach, Cu pillars with high aspect ratio, acting somewhat as compliant interconnections but with solder caps, were developed. The Cu post was introduced to increase the standoff height of the interconnections, thereby reducing strains in solders and, subsequently, improving the joints’ reliability. Cu pillar interconnections were first implemented in production in 2005 in RF power amplifiers and front-end modules to improve their electrical and thermal performance, reliability, and cost. Cu pillar technology has been demonstrated at pitches down to 35 µm in production today. However, further pitch scaling is hindered by aggravated risks of bridging, difficulties in controlling interfacial reactions with further reduced solder volumes, and fundamental material limitations, including maximum admissible current densities of 104 A/cm2 and operating temperatures of 150°C or below 0.3–0.5 × Tm to prevent catastrophic creep failure.38,39,40,–41

Solid–liquid interdiffusion (SLID) bonding, shown in Fig. 4, also known as transient liquid-phase (TLP) bonding or diffusion soldering, was proposed and developed as the next natural evolution to extend the applicability of solder-based technologies to finer pitches. It has been extensively researched and demonstrated in a wide range of material systems, including Ag-Sn, Ag-In, Au-Sn, Au-In, and Ni-Sn.42,43,–44 Intermetallic compounds have higher melting points and provide higher thermal stability and greater current-carrying capability than solders by an order of magnitude or more.45 SLID bonding retains the ease of processability of solders while enabling finer pitches and performance improvements. However, intermetallics are typically stiff and brittle, which results in thermomechanical stresses in active devices that must be managed to achieve reliability.46,47,48,–49

Beyond solder-based systems, all-Cu interconnections have been extensively pursued by the semiconductor industry as the ultimate interconnection node. Copper has outstanding electrical and thermal conductivities, thermal stability at temperatures exceeding 300°C, as well as excellent power-handling capability, two orders of magnitude higher than that of traditional solders. In addition, copper is relatively inexpensive and compatible with back-end-of-line processes and infrastructures, making it an ideal candidate interconnection material.50,51 As a solid-state interconnection and assembly (no molten phase in assembly) technology, all-Cu interconnections can be viewed to scale to ultrafine pitches of 5 µm and below. Direct Cu-Cu bonding faces many fundamental material and process challenges that have hindered technology development, including: (1) room-temperature oxidation, (2) low diffusivity at temperatures below 300°C, and (3) low tolerance to non-coplanarities and warpage due to relatively high elastic modulus. For standard Cu pillar technology, these fundamental challenges can be addressed through: (a) fluxing under assembly to prevent oxidation, (b) high diffusivity of solder in molten form at 250°C, and (c) high compliance and fatigue life due to the low elastic modulus of solders, respectively. However, such solutions cannot be applied to direct Cu-Cu bonding because: (a) of the incompatibility of fluxing with typical direct Cu-Cu bonding conditions, (b) Cu has a melting point of 1081°C and undergoes comparatively slower kinetics under solid-state diffusion, and (c) Cu has a relatively high modulus of ~ 121 GPa compared with that of solders.

Consequently, existing technologies rely heavily on selective activation of the bonding surface to ensure perfect contact and high diffusivity across the Cu-Cu interface for metallurgical bonding, as well as involving expensive planarization steps to eliminate non-coplanarities. Essentially, current state-of-the-art technologies in direct Cu-Cu bonding require high bonding forces, assembly in vacuum, inert or reducing environments with temperatures far greater (> 300°C) than that used for solder-based reflow, and long annealing times with expensive chemical–mechanical polishing steps.52,53,54,55,56,57,58,–59 This limits their adoption to wafer-level packaging (WLP). Direct Cu-Cu bonding using capillary bridging of nano-Cu inks under evaporation was recently proposed by IBM Zurich.60 This technology reintroduces a low-modulus viscous phase, playing a similar role to the solder caps in Cu pillar technology, to enhance wettability and compliance, two critical properties in assembly that are lost when shifting from solders to solid-state systems. Nanomaterials such as pastes and inks benefit from high surface area and can, therefore, sinter at low temperatures to achieve strong joints with high electrical and thermal performance after densification.61,62,63,64,–65

A similar technology evolution was observed for die-attach interconnections in high-power modules, as shown in Fig. 5, primarily motivated by the need for increased operating temperatures and increased reliability concerns. The rise of wide-bandgap semiconductors has accelerated development of alternative technological solutions to traditional solders with improved heat removal capability while still providing robust electrical connection. While high-temperature solder alloys such as Au-Ge and Au-Sn eutectic have been considered, the prohibitive cost of Au has limited their wide adoption. Like in digital applications, use of TLP/SLID bonding technologies has been proposed but faces many manufacturability and reliability challenges and has, therefore, only met with limited adoption in high-volume manufacturing by Infineon.66,67,68,–68 Sintering of nanosilver pastes has also gained momentum in the last decade as an alternative to high-lead solders in high-temperature applications,69,70,71,–71 as shown in Fig. 5.69 The resulting sintered joints have outstanding thermal and electrical conductivities as well as thermal stability at temperatures exceeding 200°C, outshining the performance of lead-free solders.69 Despite early adoption by key industry players such as Semikron, ABB, and Infineon, Ag sintering has only achieved, so far, limited production, as it faces manufacturability and cost challenges that have yet to be fully addressed.72 Silver sintering pastes typically require noble interfaces such as Au or Ag to form a strong bond, which increases the overall cost.73,74,75,–75 In addition, sintered joints suffer from retained porosity due to incomplete densification and voids caused by evaporation of organic volatiles, present to prevent agglomeration of the particles prior to sintering.76 Pores and voids degrade the mechanical, thermal, and electrical properties of the sintered joints. Furthermore, they are found to coalesce and grow during temperature cycling in operation, and can act as precracks and, ultimately, lead to early failure of the joints.74 Therefore, sintered joints with over 90% densification are highly desirable. However, higher densification also translates into high modulus, which can induce severe mechanical stresses in thin active power devices and limit scalability at large die sizes. Sintering of Cu nanoparticles has also received attention as a lower-cost alternative, with comparable electrical and thermal properties to Ag. However, it inherently faces the same limitations as Ag sintering. Moreover, oxidation of copper nanoparticles before, during, and after sintering is an additional challenge that is typically addressed through expensive surface treatments at nanoscale, possibly offsetting the cost advantage.77,78 To address the aforementioned challenges, a new class of Cu-based die-attach technologies is, therefore, required with the processability, compliance, and cost of solders, but electrical and thermal properties matching those of Ag sintering.

Evolution of interconnection materials after ban of lead solders. Image of metastable SLID die-attach in the Cu-Sn system. Image of nanosilver sintering shows the free surface of silver nanoparticle paste after sintering at 300°C. Nanosilver sintering image reprinted with permission from Ref. 69

Why Nanoporous Metals are Good Candidates

As previously mentioned, Cu is an ideal candidate that has the potential to provide a low-cost universal solution for many electronic applications. However, Cu lacks the compliance required in assembly (Fig. 2) to accommodate unavoidable non-coplanarities, making it difficult to achieve intimate atomic contact of the bonding interfaces, and ultimately, form a metallic joint through interdiffusion. The most intuitive way to lower the elastic modulus of a bulk material is to introduce porosity to form a sponge-like solid. Porosity is, however, undesirable in electronic materials as it degrades the electrical, thermal, and reliability performance and should, therefore, be eliminated during the assembly step. To that effect, porous metals have been demonstrated to sinter and densify to approach the properties of dense solids with bulk-like properties. In a similar manner to nanoparticle systems, NP metals with nanoscale feature sizes benefit from high surface area, making them more reactive and enabling sintering at temperatures below that of the melting point of the bulk material. Lastly, NP metals can be formed through chemical dealloying (etching) of a baseline alloy, which can be deposited by electrodeposition, sputtering, or through powder processing. Their fabrication process is, therefore, not only compatible with standard photolithography processes commonly used in wafer bumping, but also highly versatile with options for manufacturing of standalone die-attach films by arc or furnace melting. This opens the door for establishment of a modular supply chain, which is highly desirable for fabless end users. This makes nanoporous Cu an ideal candidate interconnection material with respect to the requirements of Fig. 2. During assembly, it will have high tolerance to non-coplanarities and warpage due to low elastic modulus, and bonding at temperatures below 250°C. After assembly, NP copper will sinter to form a strong metallic Cu joint with over 90% density, achieving bulk-like properties such as high shear strength, high electrical and thermal conductivities, thermal stability at temperatures exceeding 300°C, and outstanding electromigration and fatigue performance.

A demonstration of the high compliance of NP Cu before sintering is shown on the tilt scanning electron microscopy (SEM) images in Fig. 6a and b, before and after frustum indentation. The resulting normalized pressure versus normalized indent depth curve is shown in Fig. 6c.79 This particular NP copper has ligaments with size of 35 nm and modulus of 25 GPa. More information on this type of experiment and results can be found in Ref. 79. Similar properties were also reported for NP gold,3,80,81 confirming that, compared with other solid-state interconnection materials, NP metals, and in particular NP Cu, offer sub-40 GPa modulus as-fabricated, which can compensate for the lack of wettability compared with liquid-phase bonding materials.5,79,82 In addition, NP Cu offers the following advantages over paste approaches: (1) low-cost synthesis, (2) scalability in pitch due to solid state, (3) high design flexibility with fine control over bondline thickness and high scalability in feature sizes and aspect ratios, (4) absence of organic additives, minimizing risks of voiding due to volatiles, and subsequent corrosion and electromigration issues, and (5) better control over the densification process and associated stresses, as well as the final properties of the joints through the initial morphology. These key attributes are detailed in the following sections. Concept schematics of implementation of this technology in digital, analog, and low-to medium-power applications is shown in Fig. 7a, with Cu pillars with NP Cu caps proposed as the next node beyond standard Cu pillars. Implementation in power electronics as high-temperature, high-performance die-attach interconnections is illustrated in Fig. 7b as a low-cost alternative to Ag sintering.

Tilt SEM view of NP copper (a) before and (b) after frustum indentation. (c) Normalized pressure and normalized indent depth of the frustum indentation is shown in the early part of the deformation. The slope in the linear regime shows that the modulus is 25 GPa for the 35-nm ligament NP copper tested. Figure (c) reproduced with permission from Ref. 79

Synthesis and Compatibility with Existing Infrastructure

NP metals are typically fabricated by dealloying, i.e., controlled etching of one (or more) elements in an alloy while the remnant self-assembles into an interconnected network of nanosized ligaments with random spatial arrangement. Pore and ligament size distributions tend to be well defined. Table I lists precursor alloys and other conditions for synthesizing NP copper as reported in literature. Table I also highlights key parameters that can impact the ligament structure, such as the precursor alloy composition, etchant type (see, for example, Fig. 2 in Ref. 83), electrolyte bath temperature,84 free or electrochemical etching, and duration.

After etching, NP metal may retain the grain orientation and structure of the precursor, so that for the case of NP gold obtained from polycrystalline Au-Ag alloy, micron-sized grains will remain after etching.95 For the case of amorphous alloy precursors, after etching, nanocrystalline grains and even nanosized twins may form within the ligaments.4,5,15,96,97 The precursor alloy may be fabricated in a variety of ways from arc melting, melt-spinning to sputter or electrodeposition. For the case of deposition on wafers, precursor films that are either sputter-or electrodeposited are preferred, with the dealloying adding one additional step to the process. Depending on the precursor alloy used, it is possible that some of the alloy will remain behind. For example, in the case of Au-Ag for assembly of NP Au, up to 5 at.% of Ag may remain.98,99,100,–100 For NP copper, for the case of Cu-Si, there is no traceable amount of Si left in the NP copper,5 but there can be remnant Zn from etching Cu-Zn or other alloys.

Concept Demonstrations

Figure 8 shows some of the earliest demonstrations of the promise of NP metals in alleviating some of the non-coplanarities. Figure 8a and b shows 100-µm NP Ag, dealloyed from Ag-Al alloys, which have also been demonstrated as standalone large-area die-attach materials.101 These sheets were bonded under pressure of 20 MPa at 200–400°C to form metallic joints with shear strength close to that of solder alloys (30 MPa).76 Figure 8c shows bonding of an NP Au bump at low pressure (10 MPa) and bond temperature of 200°C. The bump was formed by dealloying Au-Ag alloy that was electroplated on a silicon wafer.102 More recently, Cu-Cu bonding of a nanoporous Cu insert, dealloyed from Cu40Al60 alloy, was demonstrated at 260°C and pressure of 10 MPa, giving a shear strength of 22 MPa.103

Examples of sintered NP metals from the literature: (a) SEM backscatter and (b) transmission electron microscopy (TEM) cross-section image of NP Ag joint. The dotted lines show regions where the Ag has densified. (c) NP Au–NP Au joint sintered at 200°C and pressure of 10 MPa. Images (a) and (b) reproduced with permission from Ref. 101. Image (c) reproduced with permission from Ref. 102

Figure 9 shows an example of an amorphous silicide alloy that was sputter deposited through a mask onto a ~ 100-mm silicon wafer. The mask was removed, then the alloy was etched in 3% HF for ~ 2 min. The resulting NP metal is shown in Fig. 9d. An additional example of a copper bump fabricated from amorphous alloy using a focused ion beam is shown in Fig. 9e and f, with the NP copper ligaments being clearly visible in Fig. 5f. Sputter deposition through a mask carries inherent complications, with the height of the overall amorphous film not achieving the same height as that of a blanket film for the same sputtering parameters and duration. In our prior work, we reported assembly demonstrations of NP copper from sputtered Cu-Si that resulted in relative densities > 85% after sintering at 200°C.24

Amorphous metal silicide films sputter-deposited through a mask on a 100-mm-diameter silicon wafer: (a) optical images of the wafer, with the insert showing smaller square scribed sections, (b) optical image of the amorphous metal silicide after mask removal, (c) SEM image of the features after etching of the amorphous silicide, (d) closeup top-view SEM image of the NP metal formed after etching the amorphous silicide. (e) Example of NP copper bump formed on a silicon substrate by focused ion beam. The precursor alloy was amorphous Cu0.41Si0.59 sputter deposited on silicon. The bump height is 2.2 µm with diameter of 3.9 µm. (f) Closeup near the base of the bump shows the NP copper morphology with ligaments of 20 nm in diameter

A process that is more in line with current interconnected device fabrication protocols is electrodeposition. Coelectrodeposition of Cu-Zn films has been a subject of considerable interest owing to their high corrosion resistance, applications in decorative and protective coatings, and production of shape-memory alloys.104 For codeposition of alloy films, it is imperative that simultaneous reduction of the two or more constituent metal cations takes place at the cathode. There are systems where the standard reduction potentials are very different, for example, for Cu-Zn alloy, the potentials are + 0.34 V for Cu2+ and − 0.76 V for Zn2+.105 In such systems, codeposition can be achieved by incorporating additives into the electrolyte bath to help modify the deposition kinetics of the two cations. In the last decade or so, several studies proposing various alternatives to cyanide-based electrolytic baths have been reported. The proposed alternative complexing agents/bath chemistries include pyrophosphates,4 polyligand pyrophosphates, where an auxiliary ligand is also added to pyrophosphate baths,105 citrates,106 sorbitol,107 ethylenediamine tetraacetic acid (EDTA),108 d-mannitol,109 and ionic liquid baths.110 An example of our more recent work is shown in Fig. 10, where Cu-Zn alloy was electrodeposited onto a mask placed on a silicon wafer with a copper seed layer. Figure 10a, b, c, and d shows before and after optical images of the patterned region, revealing excellent preservation of overall features despite some lateral shrinkage after dealloying (Fig. 10c and d). The through-thickness SEM image in Fig. 10e shows NP copper with some remnant Cu-Zn on top of the plated copper.

Electrodeposited Cu-Zn alloy through a mask onto a silicon wafer with a copper seed layer (a) optical images of coupon after electrodeposition. (b) a close up optical view of one of the features with width of 180 μm and neck region of 50 μm (c) optical image of the pattern after dealloying to form NP Copper (d) closeup optical image after dealloying with slightly reduced feature sizes width of 170 μm and neck of 40 μm. (e) SEM image of the through thickness view showing NP Copper with some remnant Cu-Zn on top of the plated Copper

Challenges and Promise

There has been tremendous progress in understanding how to synthesize NP metals with desired ligament dimensions using different types of electrolytes and environments. The compatibility of NP copper synthesis with existing semiconductor fabrication protocols and the ability to achieve materials with > 90% densification after low-temperature sintering is highlighted.

At the same time, several challenges remain to be overcome. Some of those include the shrinkage that can occur after dealloying that, if left uncontrolled, may result in crack formation or delamination. Figure 11a shows some of the possible mechanisms to alleviate stress buildup due to substantial shrinkage. Figure 11b and c shows some possible NP copper films that can develop cracks if tensile stress buildup is not carefully controlled. However, it is possible to eliminate or reduce some of the stresses through careful development of residual compressive stresses (Fig. 11d and e). Other proposed solutions, such as gentle dealloying,111 two-step dealloying,112 introduction of compressive stresses,96 or control over dealloying rate,113 may also allow the sample to undergo the necessary dimensional changes and eliminate crack formation. There may also be possibilities to alleviate tensile stress buildup by patterning instead of employing blanket thin films. With NP metals, there are multiple routes to optimize the pore arrangement, ligament morphology, etc. to achieve desirable functionalities.

(a) Dealloying can result in substantial through thickness shrinkage. Such dramatic changes in dimensions can be accommodated either enabling porosity evolution during dealloying. Otherwise, the material may relieve excessive stress buildup by grain boundary relaxation, surface perturbation or even crack formation. (b) Examples of NP Copper blanket films with little control of crack formation. A closeup of a region (c) highlighting NP Copper morphology. (d) Some control over the dealloying process can result in diminished cracks in NP Copper and the resulting closeup shows (e) a more intricate NP Copper morphology

References

A. Wittstock, J. Biener, J. Erlebacher, and M. Bäumer, Nanoporous Gold: From an Ancient Technology to a High-Tech Material (London: Royal Society of Chemistry, 2012).

R. Liu and A. Antoniou, Scr. Mater. 67, 12 (2012).

R. Liu and A. Antoniou, Acta Mater. 61, 7 (2013).

R. Liu, J. Gruber, D. Bhattacharyya, G.J. Tucker, and A. Antoniou, Acta Mater. 1, 103 (2016).

R. Liu, S. Zheng, J.K. Baldwin, M. Kuthuru, N. Mara, and A. Antoniou, Appl. Phys. Lett. 103, 24 (2013).

T. Rahman, R. Liu, E. Ortel, R. Kraehnert, and A. Antoniou, Appl. Phys. Lett. 104, 24 (2014).

J. Weissmüller and K. Sieradzki, MRS Bull. 43, 1 (2018).

J. Erlebacher and R. Seshadri, MRS Bull. 34, 8 (2011).

L.J. Gibson and M.F. Ashby, Cellular Solids: Structure and Properties (Cambridge: Cambridge University Press, 1999).

N.J. Briot and T.J. Balk, Philos. Mag. 95, 27 (2015).

N. Badwe, X. Chen, and K. Sieradzki, Acta Mater. 1, 129 (2017).

D. Farkas, A. Caro, E. Bringa, and D. Crowson, Acta Mater. 61, 9 (2013).

N. Huber, R.N. Viswanath, N. Mameka, J. Markmann, and J. Weißmüller, Acta Mater. 1, 67 (2014).

J. Snyder, T. Fujita, M. Chen, and J. Erlebacher, Nat. Mater. 9, 11 (2010).

R. Kraehnert, E. Ortel, B. Paul, B. Eckhardt, M. Kanis, R. Liu, and A. Antoniou, Catal. Sci. Technol. 5, 1 (2015).

S. Supansomboon, A. Porkovich, A. Dowd, M.D. Arnold, and M.B. Cortie, ACS Appl. Mater. Interfaces 6, 12 (2014).

M. Hakamada, S. Matsumura, and M. Mabuchi, Mater. Lett. 70, 1 (2012).

J. Biener, A. Wittstock, L.A. Zepeda-Ruiz, M.M. Biener, V. Zielasek, D. Kramer, R.N. Viswanath, J. Weissmuller, M. Baumer, and A.V. Hamza, Nat. Mater. 8, 1 (2009).

D.Y. Ding, Z. Chen, and C. Lu, Sensors Actuat. B Chem. 120, 1 (2006).

H.-J. Jin, X.-L. Wang, S. Parida, K. Wang, M. Seo, and J. Weissmuller, Nano Lett. 10, 187 (2010).

E.M. Bringa, J.D. Monk, A. Caro, A. Misra, L. Zepeda-Ruiz, M. Duchaineau, F. Abraham, M. Nastasi, S.T. Picraux, Y.Q. Wang, and D. Farkas, Nano Lett. 12, 7 (2012).

H.-J. Qiu, X. Li, H.-T. Xu, H.-J. Zhang, and Y. Wang, J. Mater. Chem. C 2, 46 (2014).

G. Gupta, K. Staggs, A.D. Mohite, J.K. Baldwin, S. Iyer, R. Mukundan, A. Misra, A. Antoniou, and A.M. Dattelbaum, J. Phys. Chem. B 119, 40 (2015).

K. Mohan, N. Shahane, P.M. Raj, A. Antoniou, V. Smet, and R. Tummala, in: Proceedings of the Applied Power Electronics Conference and Exposition (APEC), 2017 IEEE, pp. 3083–3090 (2017).

N. Shahane, K. Mohan, R. Behera, A. Antoniou, P.R. Markondeya, V. Smet, and R. Tummala, in: Proceedings of the Electronic Components and Technology Conference (ECTC), 2016 IEEE 66th, pp. 829–836 (2016).

N. Shahane, K. Mohan, G. Ramos, A. Kilian, R. Taylor, F. Wei, P. Raj, A. Antoniou, V. Smet, and R. Tummala, in: Proceedings of the Electronic Components and Technology Conference (ECTC), 2017 IEEE 67th, pp. 968–975 (2017).

E.C.C. Yeh, W.J. Choi, K.N. Tu, P. Elenius, and H. Balkan, Appl. Phys. Lett. 80, 4 (2002).

K.N. Tu, J. Appl. Phys. 94, 9 (2003).

M. Abtew and G. Selvaduray, Mater. Sci. Eng. R Rep. 27, 5 (2000).

A. Antoniou and A.F. Bastawros, J. Mater. Res. 18, 10 (2003).

Y.-S. Lai, K.-M. Chen, C.-L. Kao, C.-W. Lee, and Y.-T. Chiu, Microelectron. Reliab. 47, 8 (2007).

J.N. Lalena, N.F. Dean, and M.W. Weiser, J. Electron. Mater. 31, 11 (2002).

R.J. McCabe and M.E. Fine, Scr. Mater. 39, 2 (1998).

T. Siewert, S. Liu, D.R. Smith, and J. Madeni, Database for Solder Properties with Emphasis on New Lead-Free Solders, Release p. 4 (2002). NIST. https://www.nist.gov/publications/database-solder-properties-emphasis-new-lead-free-solders.

K. Suganuma, S.-J. Kim, and K.-S. Kim, JOM 61, 1 (2009).

T. Zhou, T. Bobal, M. Oud, and J. Songliang, (Coining Inc., 1999). https://www.ametek-ecp.com/-/media/ametek-ecp/files/cwtechnicalpapers/coining_english_gold_tin_paper.pdf.

M. Gerber, C. Beddingfield, S. O’Connor, Y. Min, L. MinJae, K. DaeByoung, P. SungSu, C. Zwenger, R. Darveaux, R. Lanzone, and P. KyungRok, in: Proceedings of the Electronic Components and Technology Conference (ECTC), 2011 IEEE 61st, pp. 612–618 (2011).

Y.J. Chen, T.L. Yang, J.J. Yu, C.L. Kao, and C.R. Kao, Mater. Lett. 110, 13 (2013).

K. Guth, N. Heuck, C. Stahlhut, A. Ciliox, N. Oeschler, L. Boewer, S. Tophinke, D. Bolowski, R. Speckels, and C. Kersting, in: Proceedings of the PCIM Europe 2015; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, pp. 1–8 (2015).

C.-P. Lin and C.-M. Chen, J. Alloys Compd. 547, 136 (2013).

H.L.J. Pang, K.H. Tan, X.Q. Shi, and Z.P. Wang, Mater. Sci. Eng. A 307, 1 (2001).

H.A. Mustain, W.D. Brown, S.S. Ang, and I.E.E.E. Trans, Compon. Packag. Technol. 33, 3 (2010).

S.W. Yoon, K. Shiozaki, S. Yasuda, and M.D. Glover, in: Proceedings of the 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 478–482 (2012).

R.W. Chuang and C.C. Lee, IEEE Trans. Compon. Packag. Technol. 25, 3 (2002).

H.Y. Chen, C.H. Tung, Y.L. Hsiao, J.L. Wu, T.C. Yeh, L.L.C. Lin, C. Chen, and D.C.H. Yu, in: Proceedings of the 2015 IEEE 65th Electronic Components and Technology Conference (ECTC), pp. 620–625 (2015).

H. Liu, K. Wang, K.E. Aasmundtveit, and N. Hoivik, J. Electron. Mater. 41, 9 (2012).

A. Garnier, C. Grémion, R. Franiatte, D. Bouchu, R. Anciant, and S. Chéramy, in: Proceedings of the 2013 IEEE 63rd Electronic Components and Technology Conference, pp. 2151–2156 (2013).

D.W. Henderson, J.J. Woods, T.A. Gosselin, J. Bartelo, D.E. King, T.M. Korhonen, M.A. Korhonen, L.P. Lehman, E.J. Cotts, S.K. Kang, P. Lauro, D.-Y. Shih, C. Goldsmith, and K.J. Puttlitz, J. Mater. Res. 19, 6 (2011).

T.A. Tollefsen, A. Larsson, O.M. Løvvik, and K. Aasmundtveit, Metall. Mater. Trans. B 43, 2 (2012).

Y.H. Hu, C.S. Liu, M.J. Lii, K.J. Rebibis, A. Jourdain, A.L. Manna, G. Beyer, E. Beyne, and C.H. Yu, in: Proceedings of the 2011 IEEE International 3D Systems Integration Conference (3DIC), pp. 1–4 (2012).

Y.-S. Tang, Y.-J. Chang, and K.-N. Chen, Microelectron. Reliab. 52, 2 (2012).

A. Shigetou, T. Itoh, K. Sawada, and T. Suga, in: Proceedings of the 58th Electronic Components and Technology Conference, 2008. ECTC 2008, pp. 1405–1409 (2008).

R. Reif, A. Fan, K.N. Chen, and S. Das, in: Proceedings of the International Symposium on Quality Electronic Design, 2002, pp. 33–37 (2002).

C.S. Tan, D.F. Lim, X.F. Ang, J. Wei, and K.C. Leong, Microelectron. Reliab. 52, 2 (2012).

C.S. Tan, D.F. Lim, S.G. Singh, S. Goulet, and M. Bergkvist, Appl. Phys. Lett. 95, 19 (2009).

C.M. Whelan, M. Kinsella, L. Carbonell, H. Meng Ho, and K. Maex, Microelectron. Eng. 70, 2 (2003).

W. Yang, H. Shintani, M. Akaike, and T. Suga, in: Proceedings of the 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), pp .2079–2083 (2011).

W. Blair and Ziptronix, in: Proceedings of the EMC-3D SE Asia Technical Symposium (2007).

A. Tay, M. Iyer, R. Tummala, V. Kripesh, E. Wong, M. Swaminathan, C. Wong, M. Rotaru, R. Doraiswami, S. Ang, and E. Kang, IEEE Trans. Adv. Packag. 27, 2 (2004).

J. Zürcher, K. Yu, G. Schlottig, M. Baum, M.M.V. Taklo, B. Wunderle, P. Warszyński, and T. Brunschwiler, in: Proceedings of the 2015 IEEE 65th Electronic Components and Technology Conference (ECTC), pp. 1115–1121 (2015).

D. Feng, Y. Feng, S. Yuan, X. Zhang, and G. Wang, Appl. Therm. Eng. 1, 45 (2013).

H. Jiang, K.-S. Moon, F. Hua, and C. Wong, Chem. Mater. 19, 18 (2007).

J.S. Kang, H.S. Kim, J. Ryu, H. Thomas Hahn, S. Jang, and J.W. Joung, J. Mater. Sci. Mater. Electron. 21, 11 (2010).

S.A. Little, T. Begou, R.W. Collins, and S. Marsillac, Appl. Phys. Lett. 100, 5 (2012).

J. Zhang, Y. Zheng, D. Zhao, S. Yang, L. Yang, Z. Liu, R. Zhang, S. Wang, D. Zhang, and L. Chen, J. Phys. Chem. C 120, 19 (2016).

H.A. Mustain, W.D. Brown, and S.S. Ang, IEEE Trans. Compon. Packag. Technol. 33, 3 (2010).

N. Heuck, K. Guth, M. Thoben, A. Mueller, N. Oeschler, L. Boewer, R. Speckels, S. Krasel, and A. Ciliox, in: Proceedings of the 2014 8th International Conference on Integrated Power Systems (CIPS), pp. 1–6 (2014).

K. Guth, N. Oeschler, L. Boewer, R. Speckels, G. Strotmann, N. Heuck, S. Krasel, and A. Ciliox, in: Proceedings of the 2012 7th International Conference on Integrated Power Electronics Systems (CIPS), pp. 1–5 (2012).

T. Wang, X. Chen, G.-Q. Lu, and G.-Y. Lei, J. Electron. Mater. 36, 10 (2007).

S. Fu, Y. Mei, G.-Q. Lu, X. Li, G. Chen, and X. Chen, Mater. Lett. 128, 1 (2014).

G.G. Umarji, S.A. Ketkar, G.J. Phatak, T. Seth, U.P. Mulik, and D.P. Amalnerkar, Mater. Lett. 59, 4 (2005).

X. Go, C. Bl, and J. Faltenbacher, in: Proceedings of the 2010 6th International Conference on Integrated Power Electronics Systems (CIPS), pp. 1–5 (2010).

P. Peng, A. Hu, A.P. Gerlich, G. Zou, L. Liu, and Y.N. Zhou, ACS Appl. Mater. Interfaces 7, 23 (2015).

R. Khazaka, L. Mendizabal, and D. Henry, J. Electron. Mater. 43, 7 (2014).

C. Chen, S. Nagao, H. Zhang, T. Sugahara, K. Suganuma, T. Iwashige, K. Sugiura, and K. Tsuruta, in: Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), pp. 2058–2062 (2016).

M.-S. Kim and H. Nishikawa, Mater. Sci. Eng. A 645, 264 (2015).

K. Schnabl, L. Wentlent, K. Mootoo, S. Khasawneh, A.A. Zinn, J. Beddow, E. Hauptfleisch, D. Blass, and P. Borgesen, J. Electron. Mater. 43, 12 (2014).

H.W.V. Zeijl, Y. Carisey, A. Damian, R. H. Poelma, A. Zinn, and C.Q. Zhang, in: Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), pp. 217–224 (2016).

R. Liu, S. Pathak, W.M. Mook, J.K. Baldwin, N. Mara, and A. Antoniou, Int. J. Plast. 98, 139 (2017).

R.W. Ertenberg, B. Andraka, and Y. Takano, Physica B Condensed Matter 2022, 284–288 (2000).

A. Mathur and J. Erlebacher, Appl. Phys. Lett. 90, 6 (2007).

X. Luo, R. Li, Z. Liu, L. Huang, M. Shi, T. Xu, and T. Zhang, Mater. Lett. 76, 3972 (2012).

J.R. Hayes, A.M. Hodge, J. Biener, A.V. Hamza, and K. Sieradzki, J. Mater. Res. 21, 10 (2006).

L. Qian and M. Chen, Appl. Phys. Lett. 91, 8 (2007).

S. An, S. Zhang, W. Liu, H. Fang, M. Zhang, and Y. Yu, Corros. Sci. 75, 1 (2013).

L. Kecheng, L. Xiaogang, C. Mingxiang, and L. Sheng, in: Proceedings of the 2014 15th International Conference on Electronic Packaging Technology (ICEPT), pp. 14–18 (2014).

C. Yang, Q.B. Zhang, M.Y. Gao, Y.X. Hua, and C.Y. Xu, J. Electrochem. Soc. 163, 9 (2016).

M. Li, Y. Zhou, and H. Geng, J. Porous Mater. 19, 5 (2011).

S.J. Nam, J.Y. Hwang, H.-K. Kim, and H.J. Choi, Acta Mater. 113, 170 (2016).

C. Zhao, Z. Qi, X. Wang, and Z. Zhang, Corros. Sci. 51, 9 (2009).

H.-B. Lu, Y. Li, and F.-H. Wang, Scr. Mater. 56, 2 (2007).

S. Zhang, S. Ye, and P. Yu, J. Non-Cryst. Solids 458, 1 (2017).

R. Liu and A. Antoniou, in preparation.

N. Shahane, K. Mohan, and A.A. Rakesh Behera, P.M. Raj, V. Smet, R. Tummala, in: Proceedings of the 2016 IEEE Electronic Components and Technology Conference (ECTC), Submitted (2016).

S.V. Petegem, S. Brandstetter, R. Maass, A.M. Hodge, B.S. El-Dasher, J. Biener, B. Schmitt, C. Borca, and H.V. Swygenhoven, Nano Lett. 9, 3 (2009).

A. Antoniou, D. Bhattacharrya, J.K. Baldwin, P. Goodwin, M. Nastasi, S. Picraux, and A. Misra, Appl. Phys. Lett. 95, 7 (2009).

J. Yu, Y. Ding, C. Xu, A. Inoue, T. Sakurai, and M. Chen, Chem. Mater. 20, 14 (2008).

Y. Sun and T.J. Balk, Metall. Mater. Trans. A Phys. Metall. Mater. Sci. 39A, 11 (2008).

S. Parida, D. Kramer, C.A. Volkert, H. Rosner, J. Erlebacher, and J. Weissmuller, Phys. Rev. Lett. 97, 3 (2006).

A.M. Hodge, J. Biener, J.R. Hayes, P.M. Bythrow, C.A. Volkert, and A.V. Hamza, Acta Mater. 55, 4 (2007).

M.-S. Kim and H. Nishikawa, Scr. Mater. 92, 43 (2014).

H. Oppermann and L. Dietrich, Microelectron. Reliab. 52, 2 (2012).

S. Sun, Q. Guo, H. Chen, M. Li, and C. Wang, Microelectron. Reliab. 1, 80 (2018).

J.C. Ballesteros, L.M. Torres-Martínez, I. Juárez-Ramírez, G. Trejo, and Y. Meas, J. Electroanal. Chem. 727, 104 (2014).

L.F. Senna, S.L. Díaz, and L. Sathler, J. Appl. Electrochem. 33, 12 (2003).

F.B.A. Ferreira, F.L.G. Silva, A.S. Luna, D.C.B. Lago, and L.F. Senna, J. Appl. Electrochem. 37, 4 (2007).

I.A. Carlos and M.R.H. de Almeida, J. Electroanal. Chem. 562, 2 (2004).

M.R.H. de Almeida, E.P. Barbano, M.F. de Carvalho, I.A. Carlos, J.L.P. Siqueira, and L.L. Barbosa, Surf. Coat. Technol. 206, 1 (2011).

R. Juškėnas, V. Karpavičienė, V. Pakštas, A. Selskis, and V. Kapočius, J. Electroanal. Chem. 602, 2 (2007).

A. Kitada, K. Yanase, T. Ichii, H. Sugimura, and K. Murase, J. Electrochem. Soc. 160, 9 (2013).

Y. Sun and T.J. Balk, Scr. Mater. 58, 9 (2008).

X.-L. Ye, N. Lu, X.-J. Li, K. Du, J. Tan, and H.-J. Jin, J. Electrochem. Soc. 161, 12 (2014).

O. Okman, D. Lee, and J.W. Kysar, Scr. Mater. 63, 1005 (2010).

Acknowledgements

Part of this work is funded by the Semiconductor Research Corporation (SRC, Task # 2661) and by the National Science Foundation through Grant Nos. CMMI-1301268 and CMMI-1351705. We are grateful to our SRC liaisons from Texas Instruments, Sadia Khan and Luu Nguyen. Cu-Si alloy deposition was performed at the Center for Integrated Nanotechnologies, an Office of Science User Facility operated for the US Department of Energy (DOE) Office of Science by Los Alamos National Laboratory (Contract DE-AC52-06NA25396).

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

About this article

Cite this article

Mohan, K., Shahane, N., Liu, R. et al. A Review of Nanoporous Metals in Interconnects. JOM 70, 2192–2204 (2018). https://doi.org/10.1007/s11837-018-3081-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11837-018-3081-z