Abstract

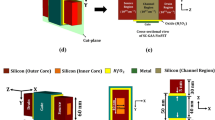

The paper presents a drain current model for double gate metal oxide semiconductor field effect transistors (DG MOSFETs) based on a new velocity saturation model that accounts for short-channel velocity saturation effect independently in the front and the back gate controlled channels under asymmetric front and back gate bias and oxide thickness. To determine the front and the back-channel velocity saturation, drain-induced barrier lowering is evaluated by effective gate voltages at the front and back gates obtained from surface potential at the threshold condition after considering symmetric and asymmetric front and back oxide thickness. The model also incorporates surface roughness scattering and ionized impurity scattering to estimate drain current for heavily / lightly doped channel for short-channel asymmetric DG MOSFET and a good agreement has been achieved with TCAD simulations, with a relative error of around 3–7%.

Similar content being viewed by others

References

F Balestra, S Cristoloveanu, M Benachir, J Brini and T Elewa, IEEE Electron. Device Lett. EDL-8, 410 (1987)

D Frank, S Laux and M Fischetti, Monte Carlo simulation of a 30 nm dual-gate MOSFET: how far can silicon go? 1992 IEDM Tech. Dig., p. 553

H-S P Wong, D J Frank and P M Solomon, Device design considerations for double-gate, ground-plane, and single-gate ultra-thin SOI MOSFET’s at the 25 nm gate length generation, IEDM Tech. Dig. (1998)

J P Colinge, Solid State Electron. 48 (6), 897 (2004)

Q Chen, K A Bowman, E M Harell and J D Meindl, IEEE Circuits Devices Mag. 19(1), 28 (2003)

An Analytic Solution of Channel Potential and Drain current for an Undoped Symmetric DG MOSFET using SiO\(_2\) and high K gate dielectrics

H Mahmoodi, S Mukhopadhyay and K Roy, High performance and low power domino logic using independent gate control in double-gate SOI MOSFETs, in Proceedings of IEEE International SOI Conference, 2004, pp. 67–68

J B Kuang, K Kim, C-T Chuang, H C Ngo, F H Gebara and K J Nowka, IEEE Trans. Very Large Scale Integr. Syst. 16 (12), 1657 (2008)

S Mukhopadhyay, H Mahmoodiand and K Roy, IEEE Trans. Very Large Scale Integr. Syst. 14 (2), 183 (2006)

Weimin Zhang, Jerry G Fossum, Leo Mathew and Yang Du, IEEE Trans. Electron Devices 52 (10), 2198 (2005)

M V R Reddy, D K Sharma, M B Patil and V R Rao, IEEE Electron Device Lett. 26 (9), 664 (2005)

M Shrivastava, M Baghini, A B Sachid, D K Sarma and V R Rao, IEEE Trans. Electron Devices 55 (11), 3274 (2008)

J R Brews, Solid State Electron. 21 (2), 345 (1978).

Y Taur, IEEE Trans. Electron Devices 48 (12), 2861 (2001)

H Lu and Y Taur, IEEE Trans. Electron Devices 53 (5), 1161, 1168 (2006)

K Suzuki, T Tanaka, Y Tosaka, H Horie and Y Arimoto, IEEE Trans. Electron Devices 40 (12), 2326 (1993)

S-H Oh, D Monore and J M Hergenrother, IEEE Electron. Device Lett. 21 (9), 445 (2000)

J P Colinge, J W Park and W Xiong, IEEE Electron. Device Lett. 24 (8), 515 (2003)

O Moldovan, A Cerdeira, D Jiménez, J-P Raskin, V Kilchytska, D Flandre, N Collaert and B Iñiguez, Solid State Electron. 51 (5), 655 (2007)

F Lime, B Iñiguez and O Moldovan, IEEE Trans. Electron Devices 55 (6), 1441 (2008)

V Hariharan, J Vasi and V R Rao, IEEE Trans. Electron Devices 55 (8), 2173 (2008)

F Liu, J He, J Zhang, Y Chen and M Chan, IEEE Trans. Electron Devices 55 (12), 3494 (2008)

M Reyboz, O Rozeau, T Poiroux, P Martin and J Jomaah, Solid-State Electron. 50 (1), 1276 (2006)

A Ortize-Conde and F J Garcia-Sanchez, Solid-State Electron. 50 (11/12), 1796 (2006)

F Liu, J He, Y Fu, J Hu, W Bian, Y Song, X Zhang and M Chan, IEEE Trans. Electron Devices 55 (3), 816 (2008)

J Zhang, L Zhang, J He and M Chan, J. Appl. Phys. 107, 054507 (2010)

M Reyboz, P Martin, T Poiroux and O Rozeau, Solid-State Electron. 53, 504 (2009)

A Dey, A Chakravorty, N Das Gupta and A Das Gupta, IEEE Trans. Electron Devices 55 (12), 3442 (2008)

Pradipta Dutta, Binit Syamal, N Mohankumar and C K Sarkar, Solid-State Electron. 56 (1), 148 (2011)

P Dutta, B Syamal, N Mohankumar and C K Sarkar, Int. J. Numer. Model.: Electron. Netw. Devices Fields 27 (4), 682 (2014)

C C McAndrew, B K Bhattacharyya and O Wing, IEEE Electron Device Lett. 12 (103), 565 (1991)

Y Taur and T H Ning, Fundamentals of modern VLSI devices (Cambridge University Press, Cambridge, 1998)

T Nishida and C-T Sah, IEEE Trans. Electron Devices ED-34(2), 310 (1987).

Acknowledgements

The authors would like to thank the Council of Scientific and Industrial Research and Department of Science and Technology, Govt. of India under SERC scheme for its financial assistance in carrying out research activities.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Dutta, P., Syamal, B., Koley, K. et al. Short-channel drain current model for asymmetric heavily / lightly doped DG MOSFETs. Pramana - J Phys 89, 33 (2017). https://doi.org/10.1007/s12043-017-1430-z

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s12043-017-1430-z

Keywords

- Asymmetric double gate

- drain current

- drain-induced barrier lowering

- velocity saturation

- drain saturation voltage