Abstract

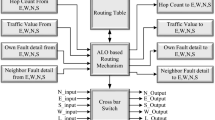

This paper presents a heterogeneous adaptable router to reduce latency in irregular mesh Network-on-Chip (NoC) architectures. Regular mesh-based NoC architecture may become irregular due to variable sized IPs and needs new routing algorithms to ensure throughput. Therefore, an irregular NoC mesh is considered and an adaptive algorithm is used for routing. The performance measures such as throughput, latency, and bandwidth are defined at design time to guarantee the performance of NoC. However, if the application has to change its communication pattern, parameters set at design time (say buffer size) may result in large area and power consumption or increased latency. Routers with large input buffers improve the efficiency of NoC communication, but they incur excessive power dissipation and hardware overheads. Routers with small buffers reduce power consumption, but result in high latency. In the proposed NoC router, input buffers can be dynamically allocated, thereby, latency can be reduced. In a 4 × 4 irregular mesh NoC with a buffer depth of 4 slots, 20% reduction in latency and 9% increase in throughput are attained using dynamic buffer allocation. An 8 × 8 irregular mesh NoC with the proposed router is exposed to the synthetic traffics like uniform, bit complement, tornado and hotspot traffics and it offered a 30.42% reduction in overall average latency and 18.33% increase in overall saturation throughput. The proposed router outperformed the static router by 22.63% less average latency for E3S benchmark applications. For the same performance, maximum of 55% reduction in buffer requirement and 53% less power consumption is achieved.

Similar content being viewed by others

References

Ahmad B, Ahmadinia A and Arslan T 2008 Dynamically reconfigurable NoC with bus based interface for ease of integration and reduced designed time. In: Proc. NASA/ESA Conf. Adapt. Hardw. Syst. (AHS): 309–314

Ahonen T and Nurmi J 2007 Hierarchically heterogenous network-on-chip. In: Proc. Int. Conf. Comput as a Tool (EUROCON): 2580–2586

Al Faruque M A and Henkel J 2008 Minimizing virtual channel buffer for routers in on-chip communication architectures. In: Proc. Conf. Des., Autom. Test Euro. (DATE): 1238–1243

Al Faruque M A, Ebi T and Henkel J 2008 ROAdNoC: Runtime observability for an adaptive network on chip architecture. In: Proc. IEEE/ACM Int. Conf. Comput.-Aided Des. (ICCAD): 543–548

Benini L and De Mircheli G 2002 Network on chips: A new SoC paradigm. IEEE Comput. 35 (1): 70–78

Dally W J and Towles B 2001 Route packets, not wires: On-Chip interconnection networks. In: Proc. 38th Design Automation Conf. (DAC 01), ACM Press: 684–689

Di Tomaso D, Morris R, Kodi A K, Sarathy A and Louri A 2012 Extending the energy efficiency and performance with channel buffers, crossbars, and topology analysis for Network-on-Chips. IEEE Trans. Very Large Scale Integr (VLSI) Syst. 21 (11): 2141–2154

Dick R Embedded System Synthesis Benchmark Suites (E3S) http://ziyang.eecs.umich.edu/~dickrp/e3s/

EEMBC Consortium http://www.eembc.org/

Jafari F, Zhonghai L., Jantsch A and Yaghmaee M H 2010 Buffer optimization in Network-on-Chip through flow regulation. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 29 (12): 1973–1986

Jingcao H, Ogras U Y and Marculescu R 2006 System-level buffer allocation for application-specific networks-on-chip router design. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 25 (12): 2919–2933

Lee S E and Bager Zadeh N 2006 Increasing the throughput of an adaptive router in network-on-chip (NoC). Proc. Int. Conf. Hardw. /Softw. Codes. Syst. Synth. 82–87

Matos D, Concatto C, Kreutz M, Kastensmidt F, Carro L and Susin A 2011 Reconfigurable routers for low power and high performance. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 19: 2045–2057

Michelogiannakis G and Dally W J 2013 Elastic buffer flow control for On-Chip Networks. IEEE Trans. Comput. 62 (2): 295–309

Michelogiannakis G, Balfour J and Dally W J 2009 Elastic buffer flow control for On-Chip networks. In: Proc. IEEE 15th Int. Symp. High-Performance Computer Architecture (HPCA ’09): 151–162

Nicopoulos C, Park K, Vijaykrishnan D N, Yousif S and Das C 2006 ViChaR: A dynamic virtual channel regulator for network-on-chip routers. In: Proc. 39th Annu. Int. Symp. Microarch. (MICRO): 333–346

Ramanujam R S, Soteriou V, Lin B. and Peh L. -S. 2011 Extending the effective throughput of NoCs with distributed shared-buffer routers. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 30 (4): 548–561

Sayed M S, Shalaby A, El-Sayed M and Goulart V 2012 Flexible router architecture for network-on-chip. J. Comput. Math. Appl. 64 (5): 1301–1310

Schonwald T, Zimmerman J, Bringmann O and Rosentiel W 2007 Fully adaptive fault-tolerant routing algorithm for Network-on-Chips architectures. Euromicro Conf. on Digital System Design Architectures, Methods and Tools(DSD): 527–534

Singh A 2005 Load-balanced routing in interconnection networks. PhD thesis in Electrical Eng., Stanford University

Su W, Shen J and Hsiung P 2011 Network-On-Chip router design with buffer stealing. In: Design Automation Conference (ASP-DAC): 160–164

Valinataj M and Mohammadi S 2010 A fault-aware, reconfigurable and adaptive routing algorithm for NoC applications. In: 18th IEEE/IFIP VLSI System On Chip Conference (VLSI-SoC): 13–18

Xuning C and Peh L 2003 Leakage power modeling and optimization in interconnection networks. In: Proc. Int. Symp. Low Power Electron. Des. (ISLPED): 90–95

Ye T T, Benini L and Micheli G D. 2002 Analysis of power consumption on switch fabrics in network routers. In: Proc. 39th Des. Autom. Conf. (DAC): 524–529

Yixuan Zhang, Randy Morris Jr. and Avinash K Kodi 2011 Design of a performance enhanced and power reduced dual-crossbar Network-on-Chip (NoC) architecture. Microprocess. Microsyst. 35 (2): 110–118

Zhonghai Lu 2005 Using wormhole switching for Networks on Chip: Feasibility analysis and microarchitecture adaptation. Licentiate thesis. Royal Institute of Technology

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

S, U., D, M. & PERINBAM J, R.P. Runtime buffer management to improve the performance in irregular Network-on-Chip architecture. Sadhana 40, 1117–1137 (2015). https://doi.org/10.1007/s12046-015-0378-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12046-015-0378-2