Abstract

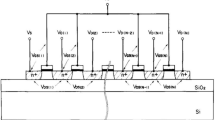

The 2D analytical models for electrostatic potential, threshold voltage, subthreshold swing, Drain Induced Barrier Lowering (DIBL) and drain current of the Dual Material Double Gate junctionless transistor with high k gate structure is revealed. The electric field is obtained by solving Poisson equation with the help of parabolic approximation technique. The high k gate stack engineered (JL DMDG stack MOSFET) exaggerate the ION current of 10−4 (A/μm) and IOFF current of 10−14(A/μm) gives a remarkable amount of leakage current reduction. The short channel effects are quashed with the symmetric high k gate stack structure to a good extent. The device characteristics have been analyzed for various different high k materials. The significant outcomes of analytical solutions are mapped with the numerical solutions from Synopsys TCAD device simulator to affirm and validate the device structure. The JL DMDG Stack MOSFET based inverter circuit was also implemented to empower the device performance in digital applications. The voltage transfer characteristics, noise margin, delay and power dissipation of the JL DMDG stack MOSFET inverter circuit is assessed through numerical simulator with the help of Verilog-A language show substantial improvement due to this gate stack engineering model.

Similar content being viewed by others

References

Mohsenifar S, Shahrokhabadi MH (2015) Gate stack high-κ materials for Si-based MOSFETs past, present, and futures. Microelectronics and Solid State Electronics 4(1):12–24

Datta S (2013) Recent advances in high performance CMOS transistors: from planar to non-planar. Electrochem Soc Interfac 22(1):41–46 https://doi.org/10.1149/2.F04131if

Colinge JP (2004) Multiple-gate SOI MOSFETs. Solid State Electron 48(6):897–905

Doyle BS, Datta S, Doczy M, Hareland S, Jin B, Kavalieros J, Linton T, Murthy A, Rios R, Chau R (2003) High performance fully-depleted tri-gate CMOS transistors. IEEE Electron Device Lett. 24(4):263–265 https://doi.org/10.1109/LED.2003.810888

Jiang C, Liang R, Wang J, Xu J (2015) A two-dimensional analytical model for short channel junctionless double-gate MOSFETs. AIP Adv 5(5):057122-1–057122-22

Venkateshwar Reddy G, Jagadesh Kumar M (2005) A new dual-material double-gate (DMDG) nanoscale SOI MOSFET-two-dimensional analytical modeling and simulation. IEEE Trans Nanotechnol 4(2):260–268

Tiwari PK, Dubey S, Singh K, Jit S (2012) Analytical modeling of subthreshold current and subthreshold swing of short-channel triple-material double-gate (TM-DG) MOSFETs. Superlattice Microst 51(5):715–724

Jiménez D, Sáenz JJ, Iniguez B, Suñé J, Marsal LF, Pallares J (2004) Modeling of nanoscale gate-all-around MOSFETs. IEEE Electron Device Lett. 25(5):314–316 https://doi.org/10.1109/LED.2004.826526

Chiang T-K (2013) A novel quasi-3-D threshold voltage model for fully depleted quadruple - gate (FDQG) MOSFETs: with equivalent number of gates (ENG) included. IEEE Trans Nanotechnol 12(6):1022–1025

Sallese J-M, Chevillon N, Lallement C, Iniguez B (2011) Charge-based modelling of junctionless double-gate field-effect transistor. IEEE Trans Electron Devices 58(8):2628–2637 https://doi.org/10.1109/TED.2018.2830972

Abhinav SR (2017) Reliability analysis of junction-less double gate (JLDG) MOSFET for analog/RF circuits for high linearity applications. Microelectron J 64:60–68

Trivedi N, Kumar M, Subhasis H, Deswal SS, Gupta M, Gupta RS (2016) Analytical modeling of junctionless accumulation mode cylindrical surrounding gate MOSFET (JAM-CSG). Int J Numer Model Electron Networks Devices Fields 29(6):1036–1043 https://doi.org/10.1002/jnm.2162

Trevisoli R, Doria RT, Souza M, Pavanello MA (2014) Substrate bias influence on the operation of junctionless nanowire transistors. IEEE Trans Electron Devices 61(5):1575–1582 https://doi.org/10.1109/TED.2014.2309334

Su C-J, Tsai T-I, Liou Y-L, Lin Z-M, Lin H-C, Chao T-S (2011) Gate-all-around junctionless transistors with heavily doped polysilicon nanowire channel. IEEE Electron Device Lett 32(4):521–523 https://doi.org/10.1109/LED.2011.2107498

Ghosh D, Parihar MS, Armstrong GA, Kranti A (2012) High - performance junctionless MOSFETs for ultralow-power analog/RF applications. IEEE Electron Device Lett 33(10):1477–1479 https://doi.org/10.1109/LED.2012.2210535

Pal A, Sarkar A (2014) Analytical study of dual material surrounding gate MOSFET to suppress short-channel effects (SCEs). Engineering Science and Technology an International Journal 17(4):205–212 https://doi.org/10.1016/j.jestch.2014.06.002

Wang P, Zhuang Y, Li C, Liu Y, Jiang Z (2015) Potential-based threshold voltage and subthreshold swing models for junctionless double-gate metal-oxide-semiconductor field-effect transistor with dual-material gate. Int J Numer Model Electron Networks Devices Fields 29(2):230–242 https://doi.org/10.1002/jnm.2067

Ghosh P, Haldar S, Gupta RS, Gupta M (2012) Analytical modeling and simulation for dual metal gate stack architecture (DMGSA) cylindrical /surrounded gate MOSFET. J Semicond Technol Sci 12(4):458–466 https://doi.org/10.5573/JSTS.2012.12.4.458

Adak S, Swain SK, Dutta A, Rahaman H, Sarkar CK (2016) Influence of channel length and high-K oxide thickness on subthreshold DC performance of graded channel and gate stack DG-MOSFETs. NANO: Brief Reports and Reviews 11(9):1650101-1–1650101-6 https://doi.org/10.1142/S1793292016501010

Intekhab Amin S, Sarin RK (2015) Charge-plasma based dual-material and gate stacked architecture of Junctionless transistor for enhanced analog performance. Superlattice Microst 88:582–590 https://doi.org/10.1016/j.spmi.2015.10.017

Intekhab Amin S, Sarin RK (2016) Enhanced analog performance of doping-less dual material and gate stacked architecture of junctionless transistor with high-k spacer. Applied Physics A Materials Science and Processing 122:380

Chiang TK (2009) A new two dimensional subthreshold behavior model for the short-channel asymmetrical dual-material double-gate (ADMDG) MOSFETs. Microelectron Reliab 49:693–698

Narendar V, Girdhardas KA (2018) Surface potential modeling of graded channel gate stack (GCGS) High-K Dielectric Dual-Material Double Gate (DMDG) MOSFET and analog/RF performance study. SILICON 10(6):2865–2875

Narendar V, Rai S, Tiwari S (2016) A two dimensional (2D) analytical surface potential and subthreshold current model for underlap dual-material double-gate (DMDG) FinFET. J Comput Electron 1–10

Chen Q, Harrell EM, Meindl JD (2003) A physical short-channel threshold voltage model for undoped symmetric double-gate MOSFETs. IEEE Trans Electron Devices 50(7):1631–1637 https://doi.org/10.1109/TED.2003.813906

Ding Z, Hu G, Gu J, Liu R, Wang L, Tang T (2011) An analytic model for channel potential and subthreshold swing of the symmetric and asymmetric double-gate. MOSFETs Microchem J 42(3):515–519 https://doi.org/10.1016/j.mejo.2010.11.002

Endo K, Ishikawa Y, Liu Y, Masahara M, Matsukawa T, O’uchi S-I, Ishii K, Yamauchi H, Tsukada J, Suzuki E (2007) Experimental evaluation of effects of channel doping on characteristics of FinFETs. IEEE Electron Device Lett 28(12):1123–1125 https://doi.org/10.1109/LED.2007.909841

Fonstad CG (2006) Microelectronic devices and circuits. McGraw-Hill, New York, ch. 16, sec. 3, 572–577

Yang Z, Yu N, Liou JJ (2018) Impact of the gate structure on ESD characteristics of Tunnel Field Effect Transistors the 7th IEEE International Symposium on Next-Generation Electronics 1–4

Yang Z, Yang Y, Yu N, Liou JJ (2018) Improving ESD protection robustness using SiGe Source/Drain regions in tunnel FET. Micromachines 9(12):657 https://doi.org/10.3390/mi9120657

Wilk GD, Wallace RM, Anthony JM (2001) High-k gate dielectrics: current status and materials properties considerations. J Appl Phys 89(10):5243–5275

Narendiran A, Akhila K, Bindu B (2015) A physics-based model of double-gate tunnel FET for circuit simulation. IETE J Res 62:387–393

Akhila K, Bindu B (2014) Design of tunnel FET based low power digital circuits 18th International Symposium on VLSI Design and Test (VDAT) 1–2

Alvarado J, Iniguez B, Estrada M, Flandre D, Cerdeira A (2010) Implementation of the symmetric doped double-gate MOSFET model in Verilog-A for circuit simulation. Int J Nume Model Electron Netw Devices Fields 23:88–106 https://doi.org/10.1002/jnm.725

Kundert K, Zinke O (2004) The designer’s guide to VerilogAMS. Kluwer Academic Publishers, Boston

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Darwin, S., Arun Samuel, T.S. A Holistic Approach on Junctionless Dual Material Double Gate (DMDG) MOSFET with High k Gate Stack for Low Power Digital Applications. Silicon 12, 393–403 (2020). https://doi.org/10.1007/s12633-019-00128-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-00128-2