Abstract

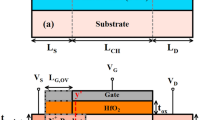

In this work, a pocket doped hetero source Silicon-on-insulator Tunneling Field Effect Transistor (SOI-TFET) with L shaped gate including back gate is proposed. The operation of this device is primarily dependent on band to band tunneling. Performance of a p-i-n TFET (proposed structure 1) is examined against the SOI double gate TFET (proposed structure 2). A brief investigation of the proposed device has been done by drain bias variation, EOT scaling, channel length modulation, pocket thickness variation, substrate dimension scaling and back gate voltage variation using Sentaurus TCAD software. The device performance is optimized for different source, drain, channel and pocket doping concentration and work function tuning of the front gate. It provides a high Ion/Ioff ratio, best reported 3.326 × 1011; steep Subthreshold Swing, SS best reported point SS 22.21 mV/decade (2 nm gate oxide) and average SS 31.74 mV/decade (3 nm gate oxide). The ON current is found to be high i.e. in the orders of mA. The proposed device is immune to short channel effects like DIBL and channel length modulation.

Similar content being viewed by others

References

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(7373):329–337

Hu C et al. (2010) Prospect of tunneling green transistor for 0.1V CMOS. Proc IEEE IEDM pp. 1–4

Wang Y, Cheng Y, Chi MH (2013) Green micro/Nano electronics. Science Press, Princeton Junction ch 5

Qiu Y, Wang R, Huang Q, Huang R (2014) A comparative study on the impacts of Interface traps on tunneling FET and MOSFET. IEEE Trans Electron Devices 61(5)

Choi WY, Park BG, Lee JD, Liu TJK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28(8):743–745

Jeon K et al. (2010) Si tunnel transistors with a novel silicided source and 46mV/dec swing. VLSI Symp Tech Dig 121–122

Dewey G et al. (2011) Fabrication, characterization, and physics of III-V heterojunction tunneling field effect transistors (H-TFET) for steep subthreshold swing. Proc IEEE IEDM 1–4

Anghel C, Chilagani P, Amara A, Vladimirescu A (2010) Tunnel field effect transistor with increased ON current, low-k spacer and high-k dielectric. Appl Phys Lett 96(12):122104-1–122104-3

Mayer F et al. (2008) Impact of SOI, Si1-x Gex OI and GeOI substrates on CMOS compatible tunnel FET performance. Proc IEEE IEDM pp 1–5

Jhaveri R, Nagavarapu V, Woo JCS (2011) Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans Electron Devices 58(1):80–86

Toh E-H, Wang GH, Samudra G, Yeo Y-C (2008) Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high performance applications. J Appl Phys 103(10):104 504-1–104 504-5

Rupam G, Brinda B, Srimanta B (2016) Effect of scaling on noise in circular gate TFET and its application as a digital inverter. Microelectron J 53:16–24

Li W, Hongxia L, Shulong W, Shupeng C, Zhaonian Y (2017) Design of High Performance Si/SiGe heterojunction tunneling FETs with a T-shaped gate. Nanoscale Res Lett 12:198. https://doi.org/10.1186/s11671-017-1958-3

Zhaonian Y (2016) Tunnel field-effect transistor with an L-shaped gate. IEEE Electron Device Letters 37:839–842. https://doi.org/10.1109/LED.2016.2574821

Vandana DW, Brinda B (2018) Optimisation of pocket doped junctionless TFET and its application in digital inverter. Micro Nano Lett 14:1–5. https://doi.org/10.1049/mnl.2018.5086

Schmidt M, Minamisawa RA, Richter S, Schafer A, Buca D, Hartmann JM, Zhao QT, Mantl S (2012) Unipolar behavior of asymmetrically doped strained Si0.5Ge0.5 tunneling field-effect transistors. Appl Phys Lett 101:123501

Mitra SK, Rupam G, Brinda B (2016) A hetero-dielectric stack gate SOI-TFET with Back gate and its application as a digital inverter. Superlattice Microst 92:37–51

Kushwaha AK (2011) On the modelling of dual-material double-gate fully-depleted silicon-on-insulator MOSFET. Ph.D. thesis, Department of Electronics and Communication Engineering, National Institute of technology, Kurukshetra deemed university, Kurukshetra, Haryana, India

Hasan Md. Mehedi (2010) Work function tuning in sub-20nm titanium nitride (tin) metal gate: mechanism and engineering. In Partial fulfillment of the requirements for the degree of master of science, King Abdullah University of Science and Technology, Thuwal, Kingdom of Saudi Arabia

Vitale A, Kedzierski J, Healey P, Wyatt W, Keast CL (2011) Work-function-tuned tin metal gate FDSOI transistors for subthreshold operation. IEEE Trans Electron Devices 58(2)

Robertson J (2004) High dielectric constant oxides. Eur Phys J Appl Phys 28:265–291. https://doi.org/10.1051/epjap:2004206

Ghosh P, Bhowmick B (2018) Low-frequency noise analysis of heterojunction SELBOX TFET. Appl Phys A Mater Sci Process 124:838. https://doi.org/10.1007/s00339-018-2264-3

Sentaurus Device User (2009) Synopsys 2009

Zhao QT, Yu WJ, Zhang B, Schmidt M, Richter S, Buca D, Hartmann J-M, Luptak R, Fox A, Bourdelle KK, Mantl S (2012) Tunneling field-effect transistor with a strained Si channel and a Si0.5Ge0.5 source. Solid State Electron 74(2012):97–101

Mori T, Fukuda K, Yasuda T, Tanabe A, Maeda T, O’uchi S-i, Liu Y, Mizubayashi W, Masahara M, Ota H (2012) EOT scaling in tunnel field-effect transistors: trade-off between subthreshold steepness and gate leakage. Extended abstracts of the 2012 international conference on solid state devices and materials, Kyoto, 2012, pp74–75

Su P, Fung SKH, Wyatt PW, Wan H, Niknejad AM, Chan M, Hu C (2003) On the body–source built-in potential lowering of SOI MOSFETs. IEEE Electron Device Lett 24(2)

Acknowledgements

This publication is an outcome of the R&D work undertaken in the project under the Visvesvaraya PhD Scheme of Ministry of Electronics & Information Technology,Government of India, being implemented by Digital India Corporation (formerly Media Lab Asia). The author give a vote of thanks to the Microelectronics Computational Laboratory, Department of Electronics and Communication Engineering, National Institute of Technology, Silchar for providing all facilities to perform our research work. We also acknowledge Prashanth Kumar, Suman Kr. Mitra, Rupam Goswami, Puja Ghosh, K Puitea and Wangkheirakpam Vandana Devi for their aid in proper handling of related software.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Goswami, P.P., Bhowmick, B. Optimization of Electrical Parameters of Pocket Doped SOI TFET with L Shaped Gate. Silicon 12, 693–700 (2020). https://doi.org/10.1007/s12633-019-00169-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-00169-7