Abstract

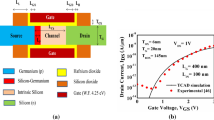

This paper proposes a novel TFET structure namely gate stacked (GS) heterojunction (HJ) partial-ground-plane (PGP) TFET with SELBOX (GSHJ-PGP-STFET) for improving the ON/OFF-state current ratio of the TFET by reducing the OFF-state current while maintaining the ON-state current nearly unaffected. Here we have done a comparative analysis of fully depleted SOI TFET and TFET on SELBOX structure with our proposed device. An extensive TCAD based simulation study has been carried out for investigating the effect of temperature on the subthreshold swing (SS), transfer characteristics, threshold voltage, and ION/IOFF ratio of the given TFET structures. The ION/IOFF ratio and SS are found to be ~1011 and 47 mV/dec respectively which is better over other two structures. Also, the proposed TFET device has improved reliability in terms of smaller effect of temperature on the performance of GSHJ-PGP-STFET as compared to the conventional SELBOX and FD-SOI TFET structures.

Similar content being viewed by others

References

Pearce CW, Yaney DS (1985) Shorts-channel effects in MOSFETs. IEEE Electron Device Lett 6:326–328. https://doi.org/10.1109/EDL.1985.26143

Roy K, Mukhopadhyay S, Mahmoodi MH (2003) Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proc IEEE 91:305–327. https://doi.org/10.1109/JPROC.2002.808156

Kilchytska V et al (2003) Influence of device engineering on the analog and RF performances of SOI MOSFETs. IEEE Trans Electron Devices 50:577–588. https://doi.org/10.1109/TED.2003.810471

Ionescu AM, Riel H (2011) Tunnel field-effect transistors energy-efficient electronic switches. Nature 479:329–337. https://doi.org/10.1038/nature10679

Kumar S, Goel E, Singh K, Singh B, Kumar MA (2016) Compact 2-D analytical model for electrical characteristics of double-gate tunnel field-effect transistors with a SiO2/HfO2 high-k stacked gate-oxide structure. IEEE Trans Electron Devices 63:3291–3299. https://doi.org/10.1109/TED.2017.2656630

Singh B, Nath T, Gola D, Singh K, Goel E, Kumar S, Jit S (2017) Ferroelectric stacked gate oxide heterojunction electro-statically doped source/drain double-gate tunnel field effect transistors: a superior structure. Mater Sci Semicond Process 71:161–165. https://doi.org/10.1016/j.mssp.2017.07.014

Anvarifard MK (2018) Enhancement of a nanoscale novel Esaki tunneling diode source TFET (ETDS-TFET) for low-voltage operations. Silicon:1–10. https://doi.org/10.1007/s12633-018-0043-6

Chandan BV, Dasari S, Nigam K, Yadav S, Pandey S, Sharma D (2018) Impact of gate material engineering on ED-TFET for improving DC/analogue-RF/linearity performances. IEEE Micro Nano Lett 13:1653–1656. https://doi.org/10.1049/mnl.2018.5131

Raad BR, Nigam K, Sharma D, Kondekar PN (2016) Performance investigation of band gap, gate material work function and gate dielectric engineered TFET with device reliability improvement. Superlattice Microst 94:138–146. https://doi.org/10.1016/j.spmi.2016.04.016

Liu C et al Simulation-based study of negative-capacitance double-gate tunnel field-effect transistor with ferroelectric gate stack. Jpn J Appl Phys 55:8–12 https://iopscience.iop.org/article/10.7567/JJAP.55.04EB08

Bhuwalka KK, Schulze J, Eisele I (2005) Scaling the vertical tunnel FET with tunnel Bandgap modulation and gate work function engineering. IEEE Trans Electron Devices 52:909–917. https://doi.org/10.1109/TED.2005.846318

Raad BR, Sharma D, Tirkey S (2018) Source engineered tunnel FET for enhanced device electrostatics with trap charges reliability. Microelectron Eng 194:79–84. https://doi.org/10.1016/j.mee.2018.03.007

Kim HW, Kim JH, Kim SW, Sun MC, Park E, Park BG (2014) Tunneling field-effect transistor with Si/SiGe material for high current drivability. Jpn J Appl Phys 53:6S https://pscience.iop.org/article/10.7567/JJAP.53.06JE12/meta

Lee M, Koo J, Chung E, Jeong D, Koo Y, Kim S (2009) Silicon nanowire-based tunneling field-effect transistors on flexible plastic substrates. Nanotechnology 20:45. https://doi.org/10.1088/0957-4484/20/45/455201

Kim SH, Jacobson ZA, Liu TJK (2010) Impact of body doping and thickness on the performance of germanium-source TFETs. IEEE Trans Electron Devices 57:1710–1713. https://doi.org/10.1109/TED.2010.2049215

Singh PK, Baral K, Kumar S, Chander S, Jit S (2019) Analytical drain current model of stacked oxide SiO2/HfO2 cylindrical gate tunnel FETs with oxide interface charge. Indian J Phys:1–9. https://doi.org/10.1007/s12648-019-01535-2

Qian C et al (2015) Investigation of self-heating effect in SOI tunnel field-effect transistor. ASICON. https://doi.org/10.1109/ASICON.2015.7517159

Garg S, Saurabh S (2019) Improving the scalability of SOI-based tunnel FETs using ground plane in buried oxide. IEEE J Electron Devices Soc 7:435–443. https://doi.org/10.1109/JEDS.2019.2907314

Narayanan MR, Nashash HA, Pal D, Chandra M (2013) Thermal model of MOSFET with SELBOX structure. J Comput Electron 12:803–811

Barah D, Singh AK, Bhowmick B (2019) TFET on Selective Buried Oxide (SELBOX) substrate with improved ION /IOFF ratio and reduced ambipolar current. Silicon:973–981. https://doi.org/10.1007/s1263

ATLAS (2013) Device simulator software. SILVACO Int, Santa Clara

Imenabadi RM, Saremi M, Vandenberghe WG (2017) A novel PNPN-like Z-shaped tunnel field- effect transistor with improved ambipolar behavior and RF performance. IEEE Trans Electron Devices 64:4752–4758. https://doi.org/10.1109/TED.2017.2755507

Loan SA, Qureshi S, Iyer SSK (2010) A novel partial-ground-plane-based MOSFET on selective buried oxide: 2-D simulation study. IEEE Trans Electron Devices 57:671–680. https://doi.org/10.1109/TED.2009.2039545

Narayanan MR (2008) Studies and minimization of kink effect in SOI MOSFET devices with SELBOX structure. ICM:232–235. https://doi.org/10.1109/ICM.2008.5393502

Ghosh P, Bhowmick B (2019) Reduction of the kink effect in a SELBOX tunnel FET and its RF/analog performance. J Comput Electron:1–10. https://doi.org/10.1007/s10825-019-01382-8

Choi WY, Park B, Lee JD, Liu TK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28:743–745. https://doi.org/10.1109/LED.2007.901273

Biswas A, Dan SS, Le Royer C, Grabinski W, Ionescu AM (2012) TCAD simulation of SOI TFETs and calibration of non-local band-to-band tunneling model. Microelectron Eng 98:334–337. https://doi.org/10.1016/j.mee.2012.07.077

Morita Y et al (2013) Performance limits of parallel electric field tunnel FET and improvement by modified gate and channel configurations. Proc IEEE ESSDERC:45–48. https://doi.org/10.1109/ESSDERC.2013.6818815

Barboni L, Siniscalchi M, Rodriguez BS (2015) TFET-based circuit design using the transconductance generation efficiency gm/Id method. Electron Device Soc 3:208–216. https://doi.org/10.1109/JEDS.2015.2412118

Yang Y, Tong X, Yang L, Guo P, Fan L, Yeo Y (2010) Tunneling field-effect transistor : capacitance components and modeling. IEEE Electron Device Lett 31:752–754. https://doi.org/10.1109/LED.2010.2047240

Dash S, Shankar G, Prasad G (2016) Improved cut-off frequency for cylindrical gate TFET using source delta doping. Procedia Technol 25:450–455. https://doi.org/10.1016/j.protcy.2016.08.131

Avci UE, Morris DH, Young IANA (2015) Tunnel field-effect transistors : prospects and challenges. IEEE J Electron Devices Soc 3:88–95. https://doi.org/10.1109/JEDS.2015.2390591

Chen S, Liu H, Wang S, Wang W, Li X, Zhao L (2018) Analog/RF performance of T-shape gate dual-source tunnel field-effect transistor. Nanoscale Res Lett 13:321. https://doi.org/10.1186/s11671-018-2723-y

Chander S, Kumar S, Kumar S, Kumar P, Baral K, Singh K, Jit S (2017) Temperature analysis of Ge/Si heterojunction SOI-tunnel FET. Superlattices Microstruct 110:162–170. https://doi.org/10.1016/j.spmi.2017.08.048

Devised I.S et al. (2015) International Technology Roadmap for Semiconductors (ITRS) 2. 0

Narang R, Saxena M, Gupta RS, Gupta M (2013) Impact of temperature variations on the device and circuit performance of tunnel FET: a simulation study. IEEE Trans Nanotechnol 12:951–957. https://doi.org/10.1109/TNANO.2013.2276401

Rahi SB, Ghosh B, Bishnoi B (2015) Temperature effect on hetero structure junctionless tunnel FET temperature effect on hetero structure junctionless tunnel FET. J Semicond 36:3–8. https://doi.org/10.1088/1674-4926/36/3/034002

Author information

Authors and Affiliations

Corresponding authors

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Singh, A.K., Tripathy, M.R., Chander, S. et al. Simulation Study and Comparative Analysis of Some TFET Structures with a Novel Partial-Ground-Plane (PGP) Based TFET on SELBOX Structure. Silicon 12, 2345–2354 (2020). https://doi.org/10.1007/s12633-019-00330-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-00330-2