Abstract

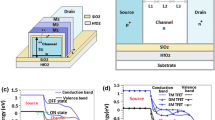

In this article, a two dimensional (2-D) threshold voltage modeling based gate and channel engineering are developed analytically for Dual Halo Gate Stacked Triple Material Dual Gate Tunnel FET (DH-GS-TM-DG-TFET) with effective surface charge. The model is derived by solving the 2-D Poisson equation in Silicon graded channel region using suitable boundary conditions. The proposed model incorporates the effects of various device parameters such as channel potential, electric field, DIBL, threshold voltage roll-off and drain current. Also, the fringing capacitance characteristics of the proposed DH-GS-TM-DG-TFET demonstrate superior performance over Triple material double gate and Single material double gate TFET structures. It is evident that the proposed device structure DH-GS-TM-DGTFET provides poor outflow current IOFF (10−16A/μm), and remarkable betterment in ON current (10−6A/μm). Moreover, the ION/IOFF ratio is 1010. To validate the robustness of model, the numerical results are compared with those obtained using Sentaurus TCAD.

Similar content being viewed by others

References

Vadthiya Narendar. Performance Enhancement of FinFET Devices with Gate -Stack (GS) High - K Dielectrics for Nanoscale Applications S i l i c o n ,Springer Nature,21 June 2018 https://doi.org/10.1007/s12633-018-9774-7

Ionescu A, Riel H (2011) Tunnel field-effect transistors as energy efficient electronic switches. Nature 479(73):329–337

Buvaneswari B, Balamurugan NB (2018) ‘Sensitivity analysis of double gate metal oxide semiconductor field effect transistor for bio-sensing applications'. Journal of Nanoelectronics and Optoelectronics

David Cavalheiro,Francesc Moll, StanimirValtchev. TFET-Based Power Management Circuit for RF Energy Harvesting .IEEE Journal of the Electron Devices Society.Jan. 2017;5(1):7–17

M. Venkatesh & N. B Balamurugan 2019,“New subthreshold performance analysis of germanium based dual halo gate stacked triple material surrounding gate tunnel field effect transistor”, Superlattices and Microstructures-Elsevier (130), 485–498 https://doi.org/10.1016/j.spmi.2019.05.016

Lu H, Seabaugh A. Tunnel field-effect transistors: state-of-the-art. IEEE J ElectronDevSoc 2014;2(4):44–49

Wu J, Min J, Taur Y (2015) Short-channel effects in tunnel FETs. IEEE Trans Electron Devices 62(9):3019–3024

Santhosh Kumar Gupta, Satyaveer Kumar, Analytical Modeling of a Triple Mateial Double Gate TFET with Hetero – Dielectric Gate stack, Silicon,Springer Nature; July 2018

Samiasafa,SamanthaLubabaNoor,Md.ZiaurRahmanKahan,“Physics-Based Generalized threshold voltage Model of Multiple Material Gate Tuneling FET structure, IEEE transactions on electron devices64 (4), April,2017

M.Venkatesh, M. Suguna and N. B Balamurugan (2019),” Subthreshold performance analysis of germanium source dual halo dual dielectric triple material surrounding gate tunnel field effect transistor for ultra low power applications”, Journal of Electronic Materials - Springer, https://doi.org/10.1007/s11664-019-07492-0

Bagga N (2015) Subir Kumar Sarkar, “an analytical model for tunnel barrier modulation in triple metal double gate TFET”. IEEE transactions on electron devices 62(7):2136–2142

Ajayan J, Nirmal D, Prajoon P, Charles PJ (2017) Analysis of nanometer-scaleInGaAs/InAs/InGaAs composite channel MOSFETs using high-K dielectrics for highspeed applications. AEU - Int J Electron Commun 79:1517. https://doi.org/10.1016/j.aeue.2017.06.004

M.Venkatesh, M. Suguna and N. B Balamurugan (2020),“Influence of Germanium Source Dual Halo Dual Dielectric Triple Material Surrounding Gate Tunnel FET for improved Analog/RF Performance”, Silicon-Springer https://doi.org/10.1007/s12633-020-00385-6

Sentaurus Device User Guide, Synopsys Inc.,Version D-2010.0

Magnone P, Crupi F, Alioto M, Kaczer B, De Jaeger B. Understanding the potential and the limits of germanium pMOSFETs for VLSI circuits from experimental measurements. IEEE Trans Very Large Scale Integr VLSI Syst2011;19(9):1569–1582

Strangio S, Palestri P, Lanuzza M, Esseni D, Crupi F, SelmiL. Benchmarks of a III-V TFET technology platform against the 10-nm CMOS FinFET technology node considering basic arithmetic circuits.Solid State Electronics. 2017;

Pradhan KP, Mohapatra SK, Agarwal PK, Sahu PK, Behera DK, Mishra J (2013) Symmetric DG-MOSFET with gate and channel engineering: a 2-D simulation study. MicroelectronSolid State Electron 2:1–9

Tsividis Y. Operation and Modelling of the MOS Transistor. 2ndedn.McGraw-Hill. New York .1989;

Kumar S, EktaGoel KS, Singh B, Singh PK, KamalakshaBaral SJ (2017) 7 2-D Analytical Modeling of the Electrical Characteristics of Dual-Material DoubleGate TFETs With a SiO2/HfO2 Stacked Gate-Oxide Structure. IEEE Trans Electron Devices 64(3)

SwetaChander, Baishya S (2015) A Two-dimensional Gate Threshold Voltage Model, for a Hetero-Junction SOI-Tunnel FET with Oxide/Source Overlap. IEEE Trans Electron Devices

Emerging Research Devices.Int.Technol.RoadmapSemicond. 2017

Suveetha P, BalamuruganN.B, ChakaravarthiG. C. V, RameshR.P,Kumar B. R. S. A 2D Analytical Modeling of single Halo Triple Material Surrounding Gate MOSFET.Journal of Electrical Engineering and Technology.2014;9(4):1355–1359

Suveetha P, Balamurugan NB (2014) A 2D Subthreshold current model for single halo triple material surrounding gate MOSFETs. Microelectronics Journal 45(6):574–577

Bentrcia T, Djeffal F, Benhaya AH (2012) Continuous analytic I-V model for GS DG MOSFETs including hot-carrier degradation effects. J Semicond 33:014001

Sarkar A, De S, Sarkar CK (2013) Asymmetric halo and singlehalo dual-material gate and double halo double material gate n-MOSFETs characteristic parameter modeling. Int J Numer Model 26:41–55

Park HJ, Ko PK, Hu C (1991) A charge sheet capacitance model of short channel MOSFET’s for spice. IEEE Trans Comput Aided Des 10(3):376–389

Young KK (1989) Short Channel Effect in fully depleted SOI MOSFETs. IEEE Trans Electron Devices 36(2):339–402

Yan RH, Ourmazd A, Lee KF (1992) Scaling the Si MOSFET: from bulk to SOI. IEEE Trans Electron Devices 39:1704–1710

Razavi P, Orouji AA (2008) Nanoscale triple material double gate (TM-DG) MOSFET for improving short channel effects. International Conference on Advances in Electronics and Microelectronics, pp 11–14

Kane EO (1961) Theory of tunneling. J Appl Phys 32(1):83–91

Hamid HAE, Guitart JR, Iniguez B (2007) Analytical model of the threshold voltage and subthreshold swing of undoped cylindrical gate-all-around-based MOSFETs. IEEE Trans. Electron Devices 54:572–579

Kumar A, Kedzierski J, Laux SE (2005) Quantam-based simulation analysis of scaling in ultrathin body device structures. IEEE Trans. Electron Devices 52:614–617

Vishnoi R, Kumar MJ (2014) compact analytical model of dual material gate tunnelling field effect transistor using interband tunnelling and channel transport. IEEE trans Electron Devices 61:1936–1942

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Venkatesh, M., Balamurugan, N.B. Influence of Threshold Voltage Performance Analysis on Dual Halo Gate Stacked Triple Material Dual Gate TFET for Ultra Low Power Applications. Silicon 13, 275–287 (2021). https://doi.org/10.1007/s12633-020-00422-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00422-4