Abstract

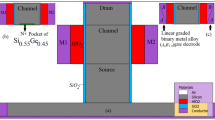

This paper proposes a novel linear graded binary metal alloy PαQ1-α gate electrode and middle N+ pocket of Si0.5Ge0.5 Vertical-TFET (LGN-VTFET) device structure. The device is gradually developed by considering initially the impact of middle N+ pocket of low band Si0.5Ge0.5 material at the channel side and then utilizing the linear graded electrodes work function of binary metal alloy instead of single metal work function. The designed device exhibits fascinating performance enhancement, as it shows 2 orders ON-current improvement over the single work function VTFET (SG-VTFET) keeping the same OFF-current and also, it renders 7 mV/Dec Sub-threshold Slope (SS), which is 79% lower than (SG-VTFET). Inclusion of N+ pocket of Si0.5Ge0.5 causes narrower tunneling band space and hence results in a high tunneling rate. Implementation of the linear graded work function of binary metal alloys causes abrupt decay in the tunneling rate unlike the gradual decay tunneling rate of single work function from the source channel interface towards the channel and in turns, offers steep sub-threshold Slope (SS). This device with a lower SS improves the transistor’s switching and encourages its applicability in high-speed circuits.

Similar content being viewed by others

References

Mookerjea S, Krishnan R, Datta S, Narayanan V (2009). IEEE Trans Electron Devices 56:2092. https://doi.org/10.1109/TED.2009.2026516

Ahish S, Sharma D, Kumar YBN, Vasantha MH (2015). IEEE Trans Electron Devices 63:288. https://doi.org/10.1109/TED.2015.2503141

Boucart K, Ionescu AM (2007). IEEE Trans Electron Devices 54:1725. https://doi.org/10.1109/TED.2007.899389

Settino F, Lanuzza M, Strangio S, Crupi F, Palestri P, Esseni D, Selmi L (2017). IEEE Trans Electron Devices 64:2736. https://doi.org/10.1109/TED.2017.2689746

Kumar N, Mushtaq U, Amin SI, Anand S (2019). Superlattices and Microstructures 125:356. https://doi.org/10.1016/j.spmi.2018.09.012

Beneventi GB, Gnani E, Gnudi A, Reggiani S, Baccarani G (2014). IEEE Trans Electron Devices 61:776. https://doi.org/10.1109/TED.2014.2298212

Kumar MJ, Janardhanan S (2013). IEEE Trans Electron Devices 60:3285. https://doi.org/10.1109/TED.2013.2276888

Bagga N, Dasgupta S (2017). IEEE Trans Electron Devices 64:606. https://doi.org/10.1109/TED.2017.2783911

Zhang JH (2016) STMicroelectronics lnc, U.S. Patent 9,385,195. US9385195B1

Tan C, Chen J, Wu XJ, Zhang H (2018). Nat Rev Mat 3:1. https://doi.org/10.1038/natrevmats.2017.89

Gandhi R, Chen Z, Singh N, Banerjee K, Lee S (2011). IEEE Electron Device Lett 32:1504. https://doi.org/10.1109/LED.2011.2165331

Deb S, Singh NB, Islam N, Sarkar SK (2011). IEEE Trans Nanotechnol 11:472. https://doi.org/10.1109/TNANO.2011.2177669

Dash S and Mishra GP (2020) J Comp Electron. 1:. https://doi.org/10.1007/s10825-020-01465-x

Jhaveri R, Nagavarapu V, Woo JC (2010). IEEE Trans Electron Devices 58:80. https://doi.org/10.1109/TED.2010.2089525

Sadek A, Ismail K, Armstrong MA, Antoniadis DA, Stern F (1996). IEEE Trans Electron Dev 43:1224. https://doi.org/10.1109/16.506773

Haddara YM, Ashburn P and Bagnall DM (2017) Springer Handbook of Electronic and Photonic Materials 1–1. DOI : https://doi.org/10.1007/978-3-319-48933-9_22

Haensch W, Nowak EJ, Dennard RH, Solomon PM, Bryant A, Dokumaci OH, Kumar A, Wang X, Johnson JB, Fischetti MV (2006) Silicon CMOS devices beyond scaling. IBM J Res Dev 50:339–361. https://doi.org/10.1147/rd.504.0339

Huang, H.S., Huang, P.R., Wang, M.C., Chen, S.Y., Wang, S.J., Chou, C.C., Huang, L.S. and Wang, W.L., (2019). https://doi.org/10.20944/preprints201902.0093.v1

Venkatesh, M., Suguna, M. and Balamurugan, N.B., Silicon L, (2020). https://doi.org/10.1007/s12633-020-00385-6

Venkatesh M, Suguna M, Balamurugan NB (2019) Subthreshold Performance Analysis of Germanium Source Dual Halo Dual Dielectric Triple Material Surrounding Gate Tunnel Field Effect Transistor for Ultra Low Power Applications. J Electron Mater 48:6724–6734. https://doi.org/10.1007/s11664-019-07492-0

Dash DK, Saha P, Banerjee P, Sarkar SK (2018) International conference on computing. Power Comm Technol (GUCON) 212. https://doi.org/10.1109/GUCON.2018.8675072

Tsui BY, Huang CF (2003) Wide range work function modulation of binary alloys for MOSFET application. IEEE Electron Device Lett 24:153–155. https://doi.org/10.1109/LED.2003.809528

Young KK (1989) Short-channel effect in fully depleted SOI MOSFETs. IEEE Trans Electron Devices 36:399–402. https://doi.org/10.1109/16.19942

Ishii R, Matsumura K, Sakai A, Sakata T (2001). Appl Surface Sci 169:658. https://doi.org/10.1016/S0169-4332(00)00807-2

Nigam K, Kondekar P, Sharma D (2016) High frequency performance of dual metal gate vertical tunnel field effect transistor based on work function engineering. Micro Nano Lett 11:319–322. https://doi.org/10.1049/mnl.2015.0526

Manna B, Sarkhel S, Islam N, Sarkar S, Sarkar SK (2012) Spatial Composition Grading of Binary Metal Alloy Gate Electrode for Short-Channel SOI/SON MOSFET Application. IEEE Trans Electron Devices 59:3280–3287. https://doi.org/10.1109/TED.2012.2220143

Kumar, P., Gupta, M. and Singh, K., 2019. Performance evaluation of transition metal Dichalcogenides based steep subthreshold slope tunnel field effect transistor. Silicon, pp.1-8

Kumar N, Amin SI, Anand S (2020) Design and performance optimization of novel Core–Shell Dopingless GAA-nanotube TFET with Si 0.5 Ge 0.5-based source. IEEE Trans Electron Devices 67(3):789–795

Kanungo S, Chattopadhyay S, Gupta PS, Sinha K, Rahaman H (2016) Study and Analysis of the Effects of SiGe Source and Pocket-Doped Channel on Sensing Performance of Dielectrically Modulated Tunnel FET-Based Biosensors. IEEE Trans Electron Devices 63:2589–2596. https://doi.org/10.1109/TED.2016.2556081

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Singh, J., Wadhawa, G. Novel Linear Graded Binary Metal Alloy PαQ1-α Gate Electrode and Middle N+ Pocket Si0.5Ge0.5 Vertical TFET for High Performance. Silicon 13, 2137–2144 (2021). https://doi.org/10.1007/s12633-020-00654-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00654-4