Abstract

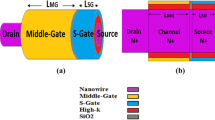

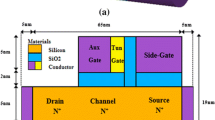

An integrated design based on Gate-All-Around (GAA) silicon Junctionless (JL) vertical profile Nanowire (NW) structure has been proposed for JL-NW-Tunnel-Field Effect Transistor (JL-NW-TFET). A uniform high doping concentration (10−19) has been used to make the device a Junctionless structure. The parametric variations of the JL-NW-TFET have been analyzed such as ON-current (ION), OFF-current (IOFF), ON-OFF ratio of current (ION/OFF) and Subthreshold-Slope (SS). Therefore, work function of gate metal (4.4 eV to 4.8 eV), thickness of oxide (1.0 nm to 2.0 nm), diameter of Nanowire (10 nm to 30 nm) and channel length (22 nm to 65 nm) has been varied by implementing device structure in SILVACO Atlas Tools. The optimum parameters of the device have been observed as: maximum ION (3.73 × 10−6 A/μm), minimum IOFF (2.97 × 10−20 A/μm), Low SS (19.40 mV/dec) and high ION/OFF (3.35 × 1013). It has been proposed that these optimum parameter characteristics are immune to short channel effects and preferred for low power applications in nano regime.

Similar content being viewed by others

Data Availability

Data used for the results are available in the manuscript.

References

Baccarani G, Wordeman MR, Dennard RH (1984) Generalized scaling theory and its application to a ¼ micrometer MOSFET design. IEEE Trans Electron Devices 31:452–462

Narang R, Gupta M, Saxena M (2013) Investigation of dielectric-modulated double-gate junctionless MOSFET for detection of biomolecules. In: 2013 Annual IEEE India conference (INDICON). IEEE, pp 1–6

Sharma S, Raj B, Khosla M (2016) Comparative analysis of MOSFET CNTFET and NWFET for high performance VLSI circuit design. A Rev J VLSI Des Tools Technol 6:19–32

Duvvury C (1986) A guide to short-channel effects in MOSFETs. IEEE Circuits Devices Mag 2:6–10

Roy K, Mukhopadhyay S, Mahmoodi-Meimand H (2003) Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proc IEEE 91:305–327

Cheung KP (2010) On the 60 mV/dec@ 300 K limit for MOSFET subthreshold swing. Proceedings of 2010 international symposium on VLSI technology. System and Application, IEEE, pp 72–73

Long W, Ou H, Kuo J-M, Chin KK (1999) Dual-material gate (DMG) field effect transistor. IEEE Trans Electron Devices 46:865–870

Kumar P, Gill SS (2018) Performance analysis of impact of source/drain doping gradients well as roll-off widths on gate induced drain leakage of double gate metal oxide semiconductor field effect transistor. J Nanoelectron Optoelectron 13:1705–1710

Kumar S, Raj B (2016) Analysis of I ON and Ambipolar current for dual-material gate-drain overlapped DG-TFET. J Nanoelectron Optoelectron 11:323–333

Sharma SK, Kumar P, Raj B, Raj B (2021) In1-xGaxAs double metal gate-stacking cylindrical nanowire MOSFET for highly sensitive photo detector

Xu M, Zhu H, Zhao L, Yin H, Zhong J, Li J, Zhao C, Chen D, Ye T (2015) Improved short channel effect control in bulk FinFETs with vertical implantation to form self-aligned halo and punch-through stop pocket. IEEE Electron Device Lett 36:648–650

Vallabhuni RR, Yamini G, Vinitha T, Reddy SS (2020) Performance analysis: D-latch modules designed using 18nm FinFET technology. In: 2020 international conference on smart electronics and communication (ICOSEC). IEEE, pp 1169–1174

Colinge J-P, Lee C-W, Afzalian A, Akhavan ND, Yan R, Ferain I, Razavi P, O'Neill B, Blake A, White M, Kelleher AM, McCarthy B, Murphy R (2010) Nanowire transistors without junctions. Nat Nanotechnol 5:225–229

Sharma SK, Raj B, Khosla M (2016) A Gaussian approach for analytical subthreshold current model of cylindrical nanowire FET with quantum mechanical effects. Microelectron J 53:65–72

Sharma SK, Raj B, Khosla M (2017) Subthreshold performance of in 1–x Ga x as based dual metal with gate stack cylindrical/surrounding gate nanowire MOSFET for low power analog applications. J Nanoelectron Optoelectron 12:171–176

Sharma SK, Singh J, Raj B, Khosla M (2018) Analysis of barrier layer thickness on performance of In1–x Ga x as based gate stack cylindrical gate nanowire MOSFET. J Nanoelectron Optoelectron 13:1473–1477

Kumar MJ, Janardhanan S (2013) Doping-less tunnel field effect transistor: design and investigation. IEEE Trans Electron Devices 60:3285–3290

Kumar S, Raj B (2016) Simulations and modeling of TFET for low power design. In: Handbook of Research on Computational Simulation and Modeling in Engineering. IGI Global, pp. 640–667,

Chawla T, Khosla M, Raj B (2021) Design and simulation of triple metal double-gate germanium on insulator vertical tunnel field effect transistor. Microelectron J 105125

Zhang Y, Li Z (2020) Analytical drain current model of strained junctionless nanowire tunnel field-effect transistor fabricated on ${\text S}{\text i} _ {1-x}{\text G}{\text e} _x $ S i 1− x G e x virtual substrate. IET Circuits, Devices Syst 14:1195–1200

Wang W, Sun Y, Wang H, Xu H, Xu M, Jiang S, Yue G (2016) Investigation of light doping and hetero gate dielectric carbon nanotube tunneling field-effect transistor for improved device and circuit-level performance. Semicond Sci Technol 31:35002

Ahangari Z (2021) Performance optimization of a nanotube core–shell semi-junctionless p+ p+ n heterojunction tunnel field effect transistor. Indian J Phys 95:1091–1099

Acharya B, Mishra GP (2021) Linearity performance analysis of junctionless nanotube tunnel field effect transistor. Mater Today Proc 43:3911–3915

Lu H, Seabaugh A (2014) Tunnel field-effect transistors: state-of-the-art. IEEE J Electron Devices Soc 2:44–49

Kumar S, Raj B (2015) Compact channel potential analytical modeling of DG-TFET based on evanescent-mode approach. J Comput Electron 14:820–827

Ghosh B, Akram MW (2013) Junctionless tunnel field effect transistor. IEEE Electron Device Lett 34:584–586

Chen ZX, Yu HY, Singh N, Shen NS, Sayanthan RD, Lo GQ, Kwong DL (2009) Demonstration of tunneling FETs based on highly scalable vertical silicon nanowires. IEEE Electron Device Lett 30:754–756

Panchore M, Singh J, Mohanty SP (2016) Impact of channel hot carrier effect in junction-and doping-free devices and circuits. IEEE Trans Electron Devices 63:5068–5071

Kumar N, Raman A (2019) Design and investigation of charge-plasma-based work function engineered dual-metal-heterogeneous gate Si-Si 0.55 Ge 0.45 GAA-cylindrical NWTFET for ambipolar analysis. IEEE Trans Electron Devices 66:1468–1474

Wadhwa G, Raj B (2018) Parametric variation analysis of symmetric double gate charge plasma JLTFET for biosensor application. IEEE Sensors J 18:6070–6077

Kumar P, Sharma SK (2020) Comparative analysis of nanowire tunnel field effect transistor for biosensor applications. Silicon:1–8

Kumar MJ, Nadda K (2012) Bipolar charge-plasma transistor: a novel three terminal device. IEEE Trans Electron Devices 59:962–967

Goudon T, Miljanović V, Schmeiser C (2007) On the Shockley–Read–hall model: generation-recombination in semiconductors. SIAM J Appl Math 67:1183–1201

Shockley W, Read Jr WT (1952) Statistics of the recombinations of holes and electrons. Phys Rev 87:835–842

Slotboom JW, De Graaff HC (1977) Bandgap narrowing in silicon bipolar transistors. IEEE Trans Electron Devices 24:1123–1125

Lombardi C, Manzini S, Saporito A, Vanzi M (1988) A physically based mobility model for numerical simulation of nonplanar devices. IEEE Trans Comput Des Integr Circuits Syst 7:1164–1171

Acknowledgements

We thank the Group, department of Electronics and Communication Engineering, NIT Jalandhar and VLSI Design Group NITTTR Chandigarh for their interest in this work and useful comments to draft the final form of the paper. The support of SERB, Government of India, Project (EEQ/2018/000444) is gratefully acknowledged. We would like to thank NIT Jalandhar and NITTTR Chandigarh for lab facilities and research environment to carry out this work.

Funding Statement

The authors declare that they have no funding available for the publication chargers of open access. We have received financial support from Science and Engineering Research Board, Government of India for computation and simulation tools to carry out the proposed work.

Author information

Authors and Affiliations

Contributions

We has been proposed Junctionless Nanowire Tunnel-Field Effect Transistor (JL-NW-TFET), which are immune to short channel effects and preferred for low power applications in nano regime.

Corresponding author

Ethics declarations

Not applicable.

Consent to Participate

We here give our consent to participate and communicate paper in this journal.

Consent for Publication

We here give our consent to publish paper in this journal.

Conflict of Interest

Authors declare that there is no conflict of Interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, P., Raj, B. Parametric Investigation and Design of Junctionless Nanowire Tunnel Field Effect Transistor. Silicon 14, 6031–6037 (2022). https://doi.org/10.1007/s12633-021-01371-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01371-2