Abstract

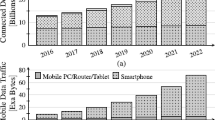

This paper reviews the need of a high performance wireline communication in the background of wirelessly connected billions of sensor nodes by 2020s. It compares the performance of the state-of-the-art wireline transceivers and underlines the challenges in improving the performance in the midst of tapering in CMOS technology scaling. This paper elaborates on the ongoing research to track the increasing bandwidth requirements in processing platforms with an affordable power budget. Energy efficient design techniques for clock recovery in multilane receivers, receiver frontend in digital CDRs, reconfigurable voltage-mode transmitter, and PAM4 equalizer in full-duplex transceivers are discussed.

Similar content being viewed by others

References

Fluhr EJ et al (2015) The 12-core POWER8 processor with 7.6 Tb/s IO bandwidth, integrated voltage regulation, and resonant clocking. IEEE J Solid-State Circuits 50(1):10–23

Singh U et al (2014) A 780 mW 4x28 Gb/s transceiver for 100 GbE Gearbox PHY in 40 nm CMOS. IEEE J Solid-State Circuits 49(12):3116–3129

Naved R et al (2015) A 28 Gb/s multistandard serial link transceiver for backplane applications in 28 nm CMOS. IEEE J Solid-State Circuits 50(4):3089–3100

Saxena S et al (2015) A 2.8mW/Gb/s 14 Gb/s serial link transceiver in 65 nm CMOS. In:IEEE VLSI circuits sym. tech. papers, pp 1–2

Saxena S et al (2017) A 2.8 mW/Gb/s, 14 Gb/s serial link transceiver. IEEE J Solid-State Circuits 52(5):1399–1411

Ibrahim S et al (2011) Low-power CMOS equalizer design for 20-Gb/s systems. IEEE J Solid-State Circuits 46(6):1321–1336

Agrawal A et al (2012) A 19-Gb/s serial link receiver with both 4-tap FFE and 5-tap DFE functions in 45-nm SOI CMOS. IEEE J Solid-State Circuits 47(12):3220–3231

Abts D et al (2010)“Energy proportional datacenter networks. In: Proceedings of international symposium on computer architecture (ISCA), pp 338–347

Barroso LA et al (2007) The case for energy-proportional computing. Computer 40(12):33–37

Anand T et al (2015) A 7 Gb/s embedded clock transceiver for energy proportional links. IEEE J Solid-State Circuits 50(12):3101–3119

Shu G et al (2016) A 16 Mb/s-8 Gb/s, 14.1-7.2pJ/bit source synchronous transceiver using DVFS and rapid on/off in 65 nm CMOS. In: ISSCC digest of technical papers, pp 398–399

Bandarupalli JD et al (2019) A reconfigurable 0.1-10 Gb/s voltage-mode transmitter with 0.2-1 V output swings. IEEE Solid-State Circuits Lett 2(7):53–56

Tomito Y et al (2007) A 20-Gb/s simultaneous bidirectional transceiver using a resistor transconductor hybrid in 0.11-μm CMOS. IEEE J Solid-State Circuits 42(3):627–636

Cechhi D et al (2001) A 2 GB/s high speed link with differential simultaneous bi-directional IO. In: Proceedings of IEEE custom integrated circuits conference, pp 505–508

Jalalifar M et al (2017) An energy-efficient and high-speed mobile memory I/O interface using simultaneous bi-directional. IEEE Trans Circuits Syst II Express Briefs 64(8):897–901

Mukherjee S et al (2020) An energy-efficient 3 Gb/s PAM4 full-duplex transmitter with 2-tap feed forward equalizer. IEEE Trans Circuits Syst II Express Briefs 67(5):916–920

Acknowledgement

The authors would like to acknowledge the Young Faculty Research Fellowship of Visvesvaraya PhD programme of MeitY for financial support in procuring soldering station that is used in populating our PCB boards for testing ICs developed during our research.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Saxena, S. Wireline communication: the backbone of data transfer. CSIT 8, 147–156 (2020). https://doi.org/10.1007/s40012-020-00297-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40012-020-00297-1