Abstract

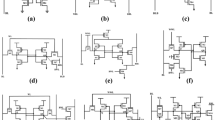

Cache memory is a key component for most microprocessors in embedded system. The increasing processing load has resulted in an upsurge in the demand for low power, high performance SRAM bit cells. Consequently, in this paper a 7T bit cell is designed for feature size 32 nm and 300 mV supply voltage. The improvement in the performance of the proposed cell is validated against the results obtained for pre-existing 6T, 7T, 8T, 9T, and 10T cells. The read and hold noise margin for the cell is obtained to be 96 and 68 mV respectively, whereas the static margin for the write operation is 170 mV. To perform a successful write operation, a pulse-width of 30 ns is utilized. The power analysis reveals that the proposed cell has minimal read/write power consumption. The leakage power for the cell is 8.4 pW and 1.2 pW for Q = ‘0’ and ‘1’ respectively. Tolerance analysis justifies that the cell maintains its functionality and yields credible outputs under process-voltage-temperature variations for static performance metrics. The layout for the proposed 7T cell occupies 0.584 µm2 area. This is 5.55% smaller than a single ended 6T. The area for other 7T counterparts, 8T, 9T, and 10T cells is larger than the proposed cell.

Similar content being viewed by others

Data availability

Data sharing not applicable to this article as no datasets were generated or analyzed during the current study.

References

Gavaskar, K., Narayanan, M. S., Nachammal, M. S., & Vignesh, K. (2021). Design and comparative analysis of SRAM array using low leakage controlled transistor techniques with improved delay. Journal of Ambient Intelligence and Humanized Computing. https://doi.org/10.1007/s12652-021-03353-z

Prasad, G., & Anand, A. (2015). Statistical analysis of low-power SRAM cell structure. Analog Integrated Circuits and Signal Processing, 82, 349–358.

Mukherjee, R., Saha, P., Chakrabarti, I., Dutta, P. K., & Ray, A. K. (2018). Fast adaptive motion estimation algorithm and its efficient VLSI system for high definition videos. Expert Systems with Applications, 101, 159–175.

Gavaskar, K., Ragupathy, U. S., & Malini, V. (2019). Design of novel SRAM cell using hybrid VLSI techniques for low leakage and high speed in embedded memories. Wireless Personal Communications, 108(4), 2311–2339.

Gavaskar, K., & Ragupathy, U. S. (2014). An efficient design and comparative analysis of low power memory cell structures. In 2014 International Conference on Green Computing Communication and Electrical Engineering (ICGCCEE) (pp. 1–5). IEEE.

Lorenzo, R., & Pailly, R. (2020). Single bit-line 11T SRAM cell for low power and improved stability. IET Computers and Digital Techniques, 14(3), 114–121.

Rathod, A. P. S., Lakhera, P., Baliga, A. K., Mittal, P., Kumar, B. (2015). Performance comparison of pass transistor and CMOS logic configuration based de-multiplexers. In International Conference on Computing, Communication & Automation (pp. 1433–1437)

Lorenzo, R., & Chaudhury, S. (2017). A novel 9T SRAM architecture for low leakage and high performance. Analog Integrated Circuits and Signal Processing, 92, 315–325.

Boley, J., Wang, J., & Calhoun, B. H. (2012). Analyzing sub-threshold bitcell topologies and the effects of assist methods on SRAM VMIN. Journal of Low Power Electronics and Applications, 2, 143–154.

Nayak, D., Acharya, D. P., & Mahapatra, K. (2016). An improved energy efficient SRAM cell for access over a wide frequency range. Solid State Electronics, 126, 14–22.

Kranti, A., & Armstrong, G. A. (2008). 6-T SRAM cell design with nanoscale double-gate SOI MOSFETs: impact of source/drain engineering and circuit topology. Semiconductor Science and Technology, 23, 075049.

Mittal, P., Negi, Y. S., & Singh, R. K. (2016). A depth analysis for different structures of organic thin film transistors: modeling of performance limiting issues. Microelectronics Engineering, 150, 7.

Gavaskar, K., Ragupathy, U. S., & Malini, V. (2019). Proposed design of 1 kb memory array structure for cache memories. Wireless Personal Communications, 109(2), 823–847.

Raj, K., Kumar, B., & Mittal, P. (2009). FPGA implementation of mask level CMOS layout design of redundant binary signed digit comparator. International Journal of Computer Science and Network Security, 9(9), 107–115.

Kumar, T. S., & Tripathi, S. L. (2021). Process evaluation in FinFET based 7T SRAM cell. Analog Integrated Circuits and Signal Processing, 109, 545–551.

Lorenzo, R., & Chaudhury, S. (2017). A novel SRAM cell design with a body-bias controller circuit for low leakage, high speed and improved stability. Wireless Personal Communications, 94, 3513–3529.

Tu, M. H., Lin, J. Y., Tsai, M. C., Jou, S. J., & Chuang, C. T. (2011). Single-ended subthreshold SRAM with asymmetrical write/read assist. IEEE Transactions on Circuits Systems I: Regular Papers, 57(2011), 3039–3047.

Kumar, B., Kaushik, B. K., Negi, Y. S., Mittal, P., & Mandal, A. (2011). Organic thin film transistors characteristics parameters, structures and their applications. IEEE Recent Advances in Intelligent Computational Systems, 2011, 706–711.

Anitha, D., Manjunathachari, K., Kumar, P. S., & Prasad, G. (2017). Design of low leakage process tolerant SRAM cell. Analog Integrated Circuits and Signal Processing, 93, 531–538.

Mittal, P., & Kumar, N. (2020). Comparative analysis of 90nm MOSFET and 18nm FinFET based different multiplexers for low power digital circuits. International Journal of Advanced Science and Technology, 29, 4089–4096.

Surana, N., & Mekie, J. (2019). Energy efficient single-ended 6-T SRAM for multimedia applications. IEEE Transactions on Circuits and Systems II: Express Briefs, 66, 1023.

Liu, J. S., Clavel, M. B., & Hudait, M. K. (2017). An energy-efficient tensile strained Ge/InGaAs TFET 7T SRAM cell architecture for ultra-low voltage applications. IEEE Transactions on Electron Devices, 64, 2193–2200.

Yang, Y., Jeong, H., Song, S. C., Wang, J., Yeap, G., & Jung, S. O. (2016). Single bit-line 7T SRAM cell for near-threshold voltage operation with enhanced performance and energy in 14 nm FinFET technology. IEEE Transactions on Circuits and Systems I: Regular Papers, 63, 1023.

Singh, P., & Vishvakarma, S. K. (2017). Ultra-low power high stability 8T SRAM for application in object tracking system. IEEE Access, 6, 2279–2290.

Cho, K., Park, J., Oh, T. W., & Jung, O. K. (2020). One sided Schmitt-Trigger Based 9T SRAM cell for near threshold operation. IEEE Transactions on Circuits and Systems I: Regular Papers, 67, 1551.

Kulkarni, J. P., & Roy, K. (2012). Ultralow-voltage process-variation-tolerant schmitt-trigger-based SRAM design. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 20, 319.

Kulkarni, J. P., Kim, K., & Roy, K. (2007). A 160 mV robust schmitt trigger based subthreshold SRAM. IEEE Journal of Solid-State Circuits, 42, 2303–2313.

Negi, S., Rana, A., Baliga, A.K., Mittal, P., Kumar, B. (2015). Performance analysis of dual gate organic thin film transistor and organic SR latch application. In: International Conference on Computing, Communication & Automation, pp. 1427–1432.

Rawat, B., & Mittal, P. (2020). Analysis of varied architectural configuration for 7T SRAM bit cell. In: 4th International Conference on Recent Trend in Communication & Electronics.

Kang, S., Leblebici, Y., & Kim, C. (2015). CMOS digital integrated circuits, 3rd ed. New York; McGraw-Hill, pp.204, 422.

Krishna, R., & Duraiswamy, P. (2021). Low leakage 10T SRAM cell with improved data stability in deep sub-micron technologies. Analog Integrated Circuits and Signal Processing, 109, 153–163.

Mann, R. W., Wang, J., Nalam, S., Khanna, S., Braceras, G., Pilo, H., & Calhoun, B. H. (2010). Impact of circuit assist method on margin and performance in 6T SRAM. Solid State Electronics, 54, 1398–1407.

Reddy, B. K. N., Ramalingaswamy, C., Nagulapalli, R., & Ramesh, D. (2019). A novel 8T SRAM with improved cell density. Analog Integrated Circuits and Signal Processing, 98, 357–366.

Rawat, B., & Mittal, P. (2021). A 32 nm single ended single port 7T SRAM for low power utilization. Semiconductor Science and Technology, 36, 095006.

Singh, J., Mohanty, S. P., & Pradhan, D. K. (2013). Robust SRAM designs and analysis. Springer.

Ahmad, S., Gupta, M. K., Alam, N., & Hasan, M. (2016). Single-ended Schmitt trigger based robust low power SRAM cell. IEEE Transaction on Very Large Scale Integration (VLSI) Systems, 20, 2634.

Islam, A., & Hasan, M. (2012). Leakage characterization of 10T SRAM cell. IEEE Transactions on Electron Devices, 59, 631–638.

Islam, A., & Hasan, M. (2011). Single-ended 6T SRAM cell to improve dynamic power dissipation by decreasing activity factor. The Mediterranain Journal of Electronics and Communication, 7, 172–181.

Gavaskar, K., & Ragupathy, U. S. (2019). Low power self-controllable voltage level and low swing logic based 11T SRAM cell for high speed CMOS circuits. Analog Integrated Circuits and Signal Processing, 100(1), 61–77.

Lin, S., Kim, Y.B., & Lombardi, F. (2008). A highly-stable nanometer memory for low power design. Proc. IEEE International Workshop Design Test of Nano Devices, Circuits Systems 17.

Doorn, T., Maten, E.T., Croon, J., Bucchianico, J.D., & Wittich, O. (2008). Importance sampling Monte Carlo simulations for accurate estimation of SRAM yield. In ESSCIRC 2008 - 34th European Solid-State Circuits Conference.

Ding, J., & Asenov, A. (2020). The analysis of static random access memory stability under the influence of statistical variability and bias temperature instability-induced ageing. Semiconductor Science and Technology, 36, 025008.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Rawat, B., Mittal, P. A low power single bit-line configuration dependent 7T SRAM bit cell with process-variation-tolerant enhanced read performance. Analog Integr Circ Sig Process 115, 77–92 (2023). https://doi.org/10.1007/s10470-023-02147-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-023-02147-x