Abstract

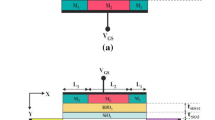

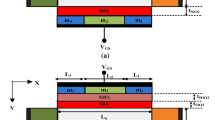

The influence of hetero dielectric gate oxide and work function engineering on DC and Analog/RF performance of dual material hetero dielectric double gate tunnel field-effect transistors (DMHDDGTFET) is investigated in this research. We examined an optimised hetero gate dielectric to reduce ambipolar current conduction, leakage current, and boost ON-current for this purpose (ION). In addition, the entire gate electrode of the proposed device structure DMHDDGTFET has consisted of three sections named as tunneling gate (M1) with work function (ϕ1), control gate (M2) with work function (ϕ2), and auxiliary gate (M3) with work function (ϕ3). To preserve dual work functionality, all possible arrangements of these work functions were incorporated. The technology computer-aided design (TCAD) simulations were carried out for these probable arrangements and matched with single material hetero dielectric double gate tunnel field-effect transistor (HDDGTFET) and conventional double gate TFET (ϕ1 = ϕ2 = ϕ3). Simulation results show that the work function grouping (ϕ1 = ϕ3 < ϕ2) provides better device performance such as improved switching characteristics and sub-threshold slope (SS). Further, based on the utmost performed work function combination the analog/RF performance analysed. This work shows improved analog/RF parameters like transconductance (gm), the gate to source capacitance (Cgs), the gate to drain capacitance (Cgd), and cut-off frequency (fT). The influence of incorporating hetero dielectric and work function engineering shows a significant enhancement in ON-state current ION (1.93 × 10−4 A/μm) and lower leakage current IOFF (2.49 × 10−17 A/μm), ION/IOFF (7.76 × 1012), smaller subthreshold swing SS (6.8 mV/decade), higher transconductance (1.12 ms) and cut-off frequency (228.4 GHz) making this device suitable for low power and high-frequency applications.

Similar content being viewed by others

Data Availability

The data and material are available within the manuscript.

References

Pearce CW, Yaney DS (1985) Shorts-channel effects in MOSFETs. IEEE Electron Device Lett 6:326–328

Roy K, Mukhopadhyay S, Mahmoodi MH (2003) Leakage current mechanisms and leakage reduction techniques in deep submicrometer CMOS circuits. Proc IEEE 91:305–327

Kilchytska V et al (2003) Influence of device engineering on the analog and RF performances of SOI MOSFETs. IEEE Trans Electron Devices 50:577–588

Wang PF, Hilsenbeck K, Nirschl T (2004) Complementary tunneling transistor for low power application. Solid State Electron 48(12):22812286

Colinge J-P, Lee C-W, Afzalian A (2010) Nanowire transistors without junctions. Nat Nanotechnol 5:225229

Ionescu AM, Riel H (2011) Tunnel field-effect transistors energy-efficient electronic switches. Nature 479:329–337

The international technology roadmap for semiconductors. http://www.itrs.net

Ram MS, Abdi DB (2015) Dopingless PNPN tunnel FET with improved performance: design and analysis. Superlattice Microst 82:430–437

Dagtekin N, Ionescu AM (2014) Impact of super-linear onset, off region due to uni-directional conductance and dominant Cgd on the performance of TFET-based circuits. IEEE J Electron Devices Soc 3:233–239

Madan J, Chaujar R (2016) Interfacial charge analysis of heterogeneous gate dielectric-gate all around-tunnel FET for improved device reliability. IEEE Trans Device Mater Reliab 16:227–234

Chandan BV, Dasari S, Nigam K, Yadav S, Pandey S, Sharma D (2018) Impact of gate material engineering on ED-TFET for improving DC/analogue-RF/linearity performances. IEEE Micro Nano Lett 13:1653–1656

Gupta A, Rai S (2017) Reliability analysis of junction-less double gate (JLDG) MOSFET for analog/RF circuits for high linearity applications. Microelectron J 64:60–68

Raad BR, Nigam K, Sharma D, Kondekar PN (2016) Performance investigation of the bandgap, gate material work function and gate dielectric engineered TFET with device reliability improvement. Superlattice Microst 94:138–146

Kumar S, Goel E, Singh K, Singh B, Kumar M, Jit S (2016) A compact 2-D analytical model for electrical characteristics of double-gate tunnel field-effect transistors with a SiO2/high-stacked gate-oxide structure. IEEE Trans Electron Devices 63(8):3291–3299

Goel E, Kumar S, Singh K, Singh B, Kumar M, Jit S (2016) 2-D analytical modeling of threshold voltage for graded-channel dual-material double-gate MOSFETs. IEEE Trans Electron Devices 63(3):966–973

Bhuwalka KK, Schulze J, Eisele I (2005) Scaling the vertical tunnel FET with tunnel bandgap modulation and gate work function engineering. IEEE Trans Electron Devices 52:909–917

Patel N, Ramesha A, Mahapatra S (2008) Drive current boosting of n-type tunnel FET with strained SiGe layer at source. Microelectron J 39(12):1671–1677

Liu C et al (2016) Simulation-based study of negative-capacitance double-gate tunnel field-effect transistor with ferroelectric gate stack. Jpn J Appl Phys 55:8–12

Kim HW, Kim JH, Kim SW, Sun MC, Park E, Park BG (2014) Tunneling field-effect transistor with Si/SiGe material for high current drivability. Jpn J Appl Phys 53:6S

Upasana K, Narang R, Saxena M, Gupta M (2016) Investigation of dielectric pocket induced variations in tunnel field-effect transistor. Superlattice Microst 92:380–390

Garg S, Saurabh S (2018) Suppression of ambipolar current in tunnel FETs using drain pocket: proposal and analysis. Superlattice Microst 113:261–270

Luo Z, Wang H, An N, Zhu Z (2015) A tunnel dielectric-based tunnel FET. IEEE Electron Device Letters 36:966–968

Upasana K, Narang R, Saxena M, Gupta M (2018) Exploring the applicability of well-optimized dielectric pocket tunnel transistor for future low power applications. Superlattice Microst 92:380–390

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling field-effect transistors. IEEE Trans Electron Devices 57(9):2317–2319

Talukdar J, Rawat G, Choudhuri B, Singh K, Mummaneni K (2020) Device physics based analytical modeling for electrical characteristics of single gate extended source tunnel FET (SG-ESTFET). Superlattice Microst 148:106725

Talukdar J, Rawat G, Singh K, Mummaneni K (2019) A novel extended source TFET with δp+-SiGe layer. Silicon 33:1–9

Talukdar J, Rawat G, Singh K, Mummaneni K (2020) Low frequency noise analysis of single gate extended source tunnel FET. Silicon 13:3971–3980

Anand S, Sarin RK (2017) Dual material gate doping-less tunnel FET with hetero gate dielectric for enhancement of analog/RF performance. J Semicond 38(2):024001

Choi WY, Lee HK (2016) Demonstration of hetero-gate-dielectric tunneling field-effect transistors (HG TFETs). Nano Converg 3:13

Gracia D, Nirmal D, Nisha Justeena A (2017) Investigation of Ge based double gate dual metal tunnel FET novel architecture using various hetero dielectric materials. Superlattice Microst S0749-6036(17):30824–30828

Sahu SA, Goswami R, Mohapatra SK (2019) Characteristic enhancement of hetero dielectric DG TFET using SiGe pocket at source/channel interface: proposal and investigation. Silicon 12(3):513–520. https://doi.org/10.1007/s12633-019-00159-9

Rani C, Bagan KB, Nirmal D, Roach RS (2019) Enhancement of performance in TFET by reducing high-K dielectric length and drain electrode thickness. Silicon 12(10):2337–2343. https://doi.org/10.1007/s12633-019-00328-w

Karbalaei M, Dideban D, Heidari H (2020) A simulation study of the influence of a high-k insulator and source stack on the performance of a double-gate tunnel FET. J Comput Electron 19(3):1077–1084

Nigam K, Kondekar PN, Sharma D (2016) Approach for ambipolar behavior suppression in tunnel FET by work function engineering. Micro Nano Lett 11(8):460–464

Kondekar PN, Nigam K, Pandey S, Sharma D (2017) Design and analysis of polarity controlled electrically doped tunnel FET with bandgap engineering for analog/RF applications. IEEE Trans Electron Devices 64(2):412–418

Chandan BV, Dasari S, Yadav S (2018) Approach to suppress ambipolarity and improve RF and linearity performances on ED tunnel FET. Micro Nano Lett 13(5):684–689

ATLAS device simulation software. (2012) Silvaco Inc.: Santa Clara

Raad BR, Tirkey S, Sharma D, Kondekar P (2017) A new design approach of doping less tunnel FET for enhancement of device characteristics. IEEE Trans Electron Devices 64:1830–1836

Shaker A, El Sabbagh M, El-Banna MM (2017) Influence of drain doping engineering on the ambipolar conduction and high-frequency performance of TFETs. IEEE Trans Electron Devices 64:3541–3547

Kumar S, Loan SA, Alamoud AM (2016) Design of a novel high performance Schottky barrier based compact transmission gate. Superlattice Microst 92:337–347

Teng S-C, Su Y-S, Wu Y-H (2019) Design and simulation of improved swing and Ambipolar effect for tunnel FET by band engineering using metal silicide at drain side. IEEE Trans Nanotechnol 18:274–278

Singh AK, Jit S (2020) Impact of interface trap charges on device level performances of a lateral/vertical gate stacked Ge/Si TFET-on-SELBOX-substrate. Appl Phys A Mater Sci Process 126(9):1–11. https://doi.org/10.1007/s00339-020-03869-9

Gupta SK, Kumar S (2018) Analytical modeling of a triple material double gate TFET with hetero-dielectric gate stack. Silicon 11(3):1355–1369

Rai MK, Gupta A, Rai S (2021) Comparative Analysis & Study of various leakage reduction techniques for Short Channel devices in Junctionless transistors: a review and perspective. Silicon. https://doi.org/10.1007/s12633-021-01181-6

Singh AK, Jit S (2020) Simulation study and comparative analysis of some TFET structures with a novel partial-ground-plane (PGP) based TFET on SELBOX structure. Silicon 12(10):2345–2354. https://doi.org/10.1007/s12633-019-00330-2

Acknowledgements

We acknowledge the VLSI Lab, Department of Electronics Engineering MNNIT Allahabad, Prayagraj, India for providing resources and also thankful to Mr. Manish Kumar Rai for useful discussion.

Funding

This work did not receive a financial support.

Author information

Authors and Affiliations

Contributions

All authors have made substantial contributions to the conception and design, or acquisition of data, or analysis and interpretation of data; have been involved in drafting the manuscript or revising it critically for important intellectual content; and have given final approval of the version to be published. Each author has participated sufficiently in the work to take public responsibility for appropriate portions of the content. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Ethics Approval

The authors declare that all procedures followed were in accordance with the ethical standards.

Consent to Participate

All the authors declare their consent to participate in this research article.

Consent for Publication

All the authors declare their consent for publication of the article on acceptance.

Competing Interests

The authors declare that there is no conflict of interest regarding the publication of this paper.

Research Involving Human Participants and/or Animals

Not applicable.

Informed Consent

Not applicable.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kavi, K.K., Tripathi, S., Mishra, R.A. et al. Design, Simulation, and Work Function Trade for DC and Analog/RF Performance Enhancement in Dual Material Hetero Dielectric Double Gate Tunnel FET. Silicon 14, 10101–10113 (2022). https://doi.org/10.1007/s12633-022-01765-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-01765-w