Abstract

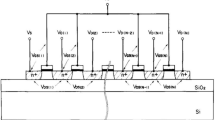

Low dimension and low power consumption are major parameters of concern for transistor-level design. Multi-gate MOSFET is one of the potential transistors showing better subthreshold performance that is suitable for low power VLSI design. In this paper, a p + pocket double gate MOSFET is designed with 14 nm gate length using gate engineering and channel engineering techniques to achieve improvement in subthreshold performance. The addition of pocket region results in enhanced barrier subthreshold conduction in transistor OFF-state condition with negligible effect on ON-state current. Pocket region length is also varied from 3 to 5 nm for performance enhancement. The paper mainly covers the DC analysis of proposed p + pocket DGMOSFET for calculation of subthreshold parameters such as ON/OFF current ratio, subthreshold slope and DIBL values. The proposed DGMOSFET shows steep subthreshold performance with ON/OFF current ratio (~ 1010), subthreshold slope (< 60mV/V) and negligible DIBL values. 2-D visualization of the proposed transistor is extracted in terms of channel electron density, energy band diagram, electrostatic potential and electric field etc. The transistor performance is also evaluated for temperature variations ranging from 250 to 400 K in steps of 25 K that show the reliability of the transistor in varying operating conditions. Material engineering is applied for the performance enhancement of the proposed p + pocket DGMOSFET with the different channel, gate and oxide materials. A similar p-channel transistor is also explored for future CMOS-based logic and memory applications. The transistor design and performance evaluation are carried out using TCAD 2D/3D device simulator by Cogenda.

Similar content being viewed by others

Data Availability

The associated data will be made available on request.

Code Availability

The proposed device is designed and simulated on Visual TCAD.

References

Colinge JP (2007) Multi-gate SOI MOSFETs. Microelectron Eng 84:2071

Sarkar A, Das AK, De S, Sarkar CK (2012) Effect of gate engineering in double-gate MOSFETs for analog/RF applications. Microelectron J 43:873

Bashir MY, Raushan MA, Ahmad S et al (2021) Investigation of gate material engineering in junctionless transistor for digital and analog applications. Silicon. https://doi.org/10.1007/s12633-021-01066-8

Mendiratta N, Tripathi SL (2020) A review on performance comparison of advanced MOSFET structures below 45 nm technology node. J Semicond 41:061401. https://doi.org/10.1088/1674-4926/41/6/061401

Kumar S, Raj B, Raj B (2021) Dual-material gate-drain overlapped DG-TFET device for low leakage current design. Silicon 13:1599–1607

Basak A, Sarkar A (2020) Impact of back gate work function for enhancement of analog/RF performance of AJDMDG Stack. MOSFET Solid State Electron Lett 2:117–123

Tripathi SL, Mishra R, Mishra RA (2012) Characteristic comparison of connected DG FINFET, TG FINFET and independent gate FINFET on 32 nm technology 2012 2nd International Conference on Power, Control and Embedded Systems, 1–7. https://doi.org/10.1109/ICPCES.2012.6508037

Tripathi SL, Verma S, Patel GS (2019) Subthreshold performance evaluation of JLDG-MOSFET 2019 5th International Conference on Signal Processing, Computing and Control (ISPCC), pp 181–184. https://doi.org/10.1109/ISPCC48220.2019.8988371

Lü W, Chen X, Liu B, Xie Z, Guo X, Zhao M (2022) Comprehensive performance enhancement of a negative-capacitance nanosheet field-effect transistor with a steep sub-threshold swing at the sub-5-nm node. Microelectron J 120:105363. https://doi.org/10.1016/j.mejo.2022.105363

Colinge JP, Lee CW, Afzalian A, Akhavan ND, Yan R, Ferain I, Razavi P, O’Neill B, Blake A, White M, Kelleher AM, McCarthy B, Murphy R (2010) Nanowire transistors without junctions. Nat Nanotechnol 5(3):225–229

Sahay S, Kumar MJ (2016) Insight into lateral band-to-band-tunneling in nanowire Junctionless FETs. IEEE Trans Electron Devices 63(10):4138–4142

Abhinav RS (2017) Reliability analysis of Junction-less Double Gate (JLDG) MOSFET for analog/RF circuits for high linearity applications. Microelectron J 64:60

Narang RA, Saxena M, Gupta M (2017) Modeling of gate underlap junctionless double gate MOSFET as bio-sensor. Mater Sci Semicond Process 71:240

Nowbahari A, Roy A, Marchetti L (2020) Junctionless transistors: State-of-the-art. Electronics 9:1174. https://doi.org/10.3390/electronics9071174

Tripathi SL, Sinha SK, Patel GS (2020) Low-power efficient p + Si0.7Ge0.3 pocket Junctionless SGTFET with varying operating conditions. J Elec Mater 49(7):4291–4299. https://doi.org/10.1007/s11664-020-08145-3

Tripathi SL, Patel GS (2019) Design of low power Si0.7Ge0.3 pocket junction-less tunnel FET using below 5nm technology. Wireless Personal Communication, vol 111. Springer, Berlin, ISSN: 0929–6212, pp 2167–2176

Tripathi SL, Patel R, Vimal Kumar Agrawal (2019) Low leakage pocket junction-less DGTFET with bio-sensing cavity region. Turk J Elec Eng Comput Sci 27(4):2466–2474. ISSN: 1300 – 0632. https://doi.org/10.3906/elk-1807-186

Kumar R, Tripathi SL, Singh AM (2021) Impact of channel engineering on 16nm, 18nm & 20nm doping-less DG MOSFET. 2021 Devices for Integrated Circuit (DevIC), 120–123. https://doi.org/10.1109/DevIC50843.2021.9455867

Kranti A, Armstrong GA (2006) Performance assessment of nanoscale double- and triple-gate FinFETs. Semicond Sci Technol 21:409–421

Gupta P, Tripathi SL (2017) Low power design of bulk driven operational transconductance amplifier. 2017 Devices for Integrated Circuit (DevIC), 241–246. https://doi.org/10.1109/DEVIC.2017.8073944

Tripathi SL (2019) Low power high performance tunnel FET: Analysis for IOT applications. Handbook of research on the internet of things applications in robotics and automation, IGI Global Publisher. ISBN:9781522595748. https://doi.org/10.4018/978-1-5225-9574-8.ch002

Maiti S, De A, Sarkar SK (2021) Analytical modelling of symmetric gate underlap quadruple gate multichannel Junctionless MOSFET Biosensor. Silicon. https://doi.org/10.1007/s12633-021-01415-7

Chanda M, De S, Sarkar CK (2015) Modeling of characteristic parameters for nano-scale junctionless double gate MOSFET considering quantum mechanical effect. J Comput Electron 14:262–269. https://doi.org/10.1007/s10825-014-0648-y

Chanda M, De S, Sarkar CK (2013) Modeling of parameters for nano-scale surrounding-gate MOSFET considering quantum mechanical effect. Int J Numer Model 27:883–895. https://doi.org/10.1002/jnm.1965

Abhisek Dixit N, Collaert, Jurczak M (2012) Measurement and analysis of source/drain contact resistance in FinFETs. Proc. SPIE 8549, 16th International Workshop on Physics of Semiconductor Devices, 85493L. https://doi.org/10.1117/12.927370

Duffy SJ et al (2017) Low source/drain contact resistance for AlGaN/GaN HEMTs with High Al concentration and Si-HP [111] substrate. ECS J Solid State Sci Technol 6:S3040

Basak A, Chanda M, Sarkar A (2021) Drain current modelling of unipolar junction dual material double-gate MOSFET (UJDMDG) for SoC applications. Microsyst Technol 27:3995–4005. https://doi.org/10.1007/s00542-019-04691-x

Asra R, Shrivastava M, Murali KVRM, Pandey RK, Gossner H, Rao VR (2011) A tunnel FET for VDD scaling below 0.6 V with a CMOS-comparable performance. IEEE Trans Electron Devices 58(7):1855–1863. https://doi.org/10.1109/TED.2011.2140322

Bhattacharya S, Tripathi SL (2022) Implementation of low power inverter using Si1 – xGex pocket N & P-channel junction-less double gate TFET. Silicon. https://doi.org/10.1007/s12633-021-01628-w

Ghoshhajra R, Biswas K, Sarkar A (2022) Device performance prediction of nanoscale junctionless FinFET using MISO artificial neural network. Silicon. https://doi.org/10.1007/s12633-021-01562-x

Zhao S, Blaabjerg F, Wang H (2021) An overview of artificial intelligence applications for power electronics. IEEE Trans Power Electron 36(4):4633–4658. https://doi.org/10.1109/TPEL.2020.3024914

Namrata Mendiratta SL, Tripathi S, Padmanaban, Hossain E (2020) Design and analysis of heavily doped n + pocket asymmetrical junction-less double gate MOSFET for biomedical applications. Appl Sci MDPI 10(7):2499. ISSN 2076–3417

Acknowledgements

We acknowledge for the support and lab facility provided by department of VLSI design, School of Electronics and Electrical Engineering, Lovely Professional University, Punjab India.

Author information

Authors and Affiliations

Contributions

NA.

Corresponding author

Ethics declarations

Conflict of Interest

There is no conflict of interest at any stage.

Competing Interest

No funding was received to assist with the preparation of this manuscript.

Ethics Approval

NA. It is a simulation-based design and analysis. So, it does not produce any environmental hazards.

Consent to Participate

Yes, we are ready to participate.

Consent for Publication

We are ready for publication with your journal.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Tripathi, S.L., Pathak, P., Kumar, A. et al. Improved Drain Current with Suppressed Short Channel Effect of p + Pocket Double-Gate MOSFET in Sub-14 nm Technology Node. Silicon 14, 10881–10891 (2022). https://doi.org/10.1007/s12633-022-01816-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-01816-2