Abstract

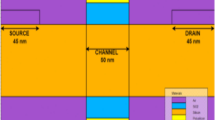

In this paper, the electrical performances for of vertical GaN junctionless metal–oxide–semiconductor-field-effect-transistors based on GaN substrate were investigated to improve the device characteristics. To improve the breakdown voltage (BV), the optimization process is performed using two-dimensional simulation technology computer-aided design. Because BV is strongly affected by the undoped GaN drift layer, gate length, and fin width, and it should be designed in views of them. The optimized device has 30.63 kA/cm2 of the on-state drain current density 30.63 kA/cm2 and 2,009 V of BV. As a result, the device characteristics for high-power and high-voltage applications can be further improved through the optimization and characterization used in this paper.

Similar content being viewed by others

References

Chowdhury S, Wong MH, Swenson BL, Mishra UK (2011) CAVET on bulk GaN substrates achieved with MBE-regrown AlGaN/GaN layers to suppress dispersion. IEEE Electron Device Lett 33:41–43

Chowdhury S, Swenson BL, Mishra UK (2008) Enhancement and depletion mode AlGaN/GaN CAVET with Mg-ion-implanted GaN as current blocking layer. IEEE Electron Device Lett 29:543–545

Ji D, Agarwal A, Li W, Keller S, Chowdhury S (2018) Demonstration of GaN current aperture vertical electron transistors with aperture region formed by ion implantation. IEEE Trans Electron Devices 65:483–487

Ji D, Agarwal A, Li H, Li W, Keller S, Chowdhury S (2018) 880 V/2.7 mΩ⋅cm2 MIS Gate Trench CAVET on Bulk GaN substrates. IEEE Electron Device Lett 39:863–865

Ben-Yaacov I, Seck YK, Mishra UK, DenBaars SP (2004) AlGaN/GaN current aperture vertical electron transistors with regrown channels. J Appl Phys 95:2073–2078

Ji D, Laurent MA, Agarwal A, Li W, Mandal S, Keller S, Chowdhury S (2016) Normally OFF trench CAVET with active Mg-doped GaN as current blocking layer. IEEE Trans Electron Devices 64:805–808

Mandal S, Agarwal A, Ahmadi E, Bhat KM, Ji D, Laurent MA, Keller S, Chowdhury S (2017) Dispersion free 450-V p GaN-gated CAVETs with Mg-ion implanted blocking layer. IEEE Electron Device Lett 38:933–936

Yeluri R, Lu J, Hurni CA, Browne DA, Chowdhury S, Keller S, Speck JS, Mishra UK (2015) Design, fabrication, and performance analysis of GaN vertical electron transistors with a buried p/n junction. Appl Phys Lett 106:183502

Otake H, Chikamatsu K, Yamaguchi A, Fujishima T, Ohta H (2008) Vertical GaN-based trench gate metal oxide semiconductor field-effect transistors on GaN bulk substrates. Appl Phys Express 1:011105

Li W, Nomoto K, Lee K, Islam SM, Hu Z, Zhu M, Gao X, Pilla M, Jena D, Xing HG (2018) Development of GaN vertical trench-MOSFET with MBE regrown channel. IEEE Trans Electron Devices 65:2558–2564

Liu C, Khadar RA, Matioli E (2017) GaN-on-Si quasi-vertical power MOSFETs. IEEE Electron Device Lett 39:71–74

Li R, Cao Y, Chen M, Chu R (2016) 600 V/1.7 Ω normally-Off GaN vertical trench metal–oxide–semiconductor field-effect transistor. IEEE Electron Device Lett 37:1466–1469

Ji D, Gupta C, Agarwal A, Chan SH, Lund C, Li W, Keller S, Mishra UK, Chowdhury S (2018) Large-area in-situ oxide, GaN interlayer-based vertical trench MOSFET (OG-FET). IEEE Electron Device Lett 39:711–714

Gupta C, Lund C, Chan SH, Agarwal A, Liu J, Enatsu Y, Keller S, Mishra UK (2017) In situ oxide, GaN interlayer-based vertical trench MOSFET (OG-FET) on bulk GaN substrates. IEEE Electron Device Lett 38:353–355

Oka T, Ina T, Ueno Y, Nishii J (2015) 1.8 mΩ· cm2 vertical GaN-based trench metal–oxide–semiconductor field-effect transistors on a free-standing GaN substrate for 12-kV-class operation. Appl Phys Express 8:054101

Ji D, Li W, Agarwal A, Chan SH, Haller J, Bisi D, Labrecque M, Gupta C, Cruse B, Keller S, Mishra UK, Chowdhury S (2018) Improved dynamic RON of GaN vertical trench MOSFETs (OG-FETs) using TMAH Wet Etch. IEEE Electron Device Lett 39:1030–1033

Oka T, Ina T, Ueno Y, Nishii J (2016) Over 10 a operation with switching characteristics of 1.2 kV-class vertical GaN trench MOSFETs on a bulk GaN substrate. In: 2016 28th International symposium on power semiconductor devices and ICs (2016), pp 459–462

Liu S, Song X, Zhang J, Zhao S, Luo J, Zhang H, Zhang Y, Zhang W, Zhou H, Liu Z, Hao Y (2020) Comprehensive design of device parameters for GaN vertical trench MOSFETs. IEEE Access 8:57126–57135

Sun M, Zhang Y, Gao X, Palacios T (2017) High-performance GaN vertical fin power transistors on bulk GaN substrates. IEEE Electron Device Lett 38:509–512

Ruzzarin M, De Santi C, Chiocchetta F, Sun M, Palacios T, Zanoni E, Meneghesso G, Meneghini M (2019) Characterization of charge trapping mechanisms in GaN vertical Fin FETs under positive gate bias. Microelectron Reliab 100:113488

Xiao M, Palacios T, Zhang Y (2019) ON-resistance in vertical power FinFETs. IEEE Trans Electron Devices 66:3903–3909

Zhang Y, Palacios T (2020) (Ultra) Wide-bandgap vertical power FinFETs. IEEE Trans Electron Devices 67:3960–3971

Xiao M, Gao X, Palacios T, Zhang Y (2019) Leakage and breakdown mechanisms of GaN vertical power FinFETs. Appl Phys Lett 114:163503

Wang H, Xiao M, Sheng K, Palacios T, Zhang Y (2020) Switching performance analysis of vertical GaN FinFETs: impact of inter-fin designs. IEEE J Emerg Sel Topics Power Electron. https://doi.org/10.1109/JESTPE.2020.2980445

Li W, Chowdhury S (2016) Design and fabrication of a 1.2 kV GaN-based MOS vertical transistor for single chip normally off operation. Phys Status Solidi a 213:2714–2720

Nandy S, Srivastava S, Rewari S, Nath V, Gupta RS (2019) Dual metal Schottky barrier asymmetric gate stack cylindrical gate all around (DM-SB-ASMGS-CGAA) MOSFET for improved analog performance for high frequency application. Microsystem Technologies 1–10

Goel A, Rewari S, Verma S, Gupta RS (2021) Modeling of shallow extension engineered dual metal surrounding gate (SEE-DM-SG) MOSFET gate-induced drain leakage (GIDL). Indian J Phys 95(2):299–308

Goel A, Rewari S, Verma S, Gupta RS (2021) Novel dual-metal junctionless nanotube field-effect transistors for improved analog and low-noise applications. J Electron Mater 50(1):108–119

Rewari S (2021) Core-shell nanowire junctionless accumalation mode field-effect transistor (CSN-JAM-FET) for high frequency applications-analytical study. SILICON 13(12):4371–4379

Ganesh A, Goel K, Mayall JS, Rewari S (2021) Subthreshold analytical model of asymmetric gate stack triple metal gate all around MOSFET (AGSTMGAAFET) for improved analog applications. Silicon 1–11

Jackson CM, Arehart AR, Cinkilic E, McSkimming B, Speck JS, Ringel SA (2013) Interface trap characterization of atomic layer deposition Al2O3/GaN metal-insulator-semiconductor capacitors using optically and thermally based deep level spectroscopies. J Appl Phys 113:204505

Narita T, Tokuda Y, Kogiso T, Tomita K, Kachi T (2018) The trap states in lightly Mg-doped GaN grown by MOVPE on a freestanding GaN substrate. J Appl Phys 123:161405

Baliga BJ (2010) Fundamentals of power semiconductor devices. Springer Science & Business Media

Meneghini M, Meneghesso G, Zanoni E (2017) Power GaN Devices. Springer International Publishing, Cham

Acknowledgements

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (No. NRF-2020R1A2C1005087). This study was supported by the BK21 FOUR project funded by the Ministry of Education, Korea (4199990113966). This research was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (NRF-2021R1A6A3A13039927). This research was supported by National R&D Program through the National Research Foundation of Korea (NRF) funded by Ministry of Science and ICT (2021M3F3A2A03017764). This investigation was financially supported by Semiconductor Industry Collaborative Project between Kyungpook National University and Samsung Electronics Co. Ltd. The EDA tool was supported by the IC Design Education Center (IDEC), Korea.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

An, H.D., Lee, S.H., Park, J. et al. Analysis and Optimization for Characteristics of Vertical GaN Junctionless MOSFETs Depending on Specifications of GaN Substrates. J. Electr. Eng. Technol. 17, 3487–3498 (2022). https://doi.org/10.1007/s42835-022-01122-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42835-022-01122-2