Abstract

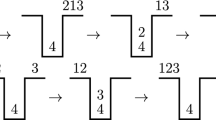

Configurations of adders, subtracters, or arithmetic logic units andregisters, which are available in many data paths, can be utilized togenerate patterns and to compact test responses. This paper analyzesthe pattern sequences generated by configurations with differenttypes of adders and subtracters. For many different seeds andconstant input values, these pattern generators can produce asequence of all possible patterns. Moreover, k-bit patterngenerators that take into account the overflow or underflow bit cangenerate bit sequences that all have period 2k-1. Thus, theperiodicity of these pattern generators is the same as that of a k-bit linear feedback shift register with a primitivecharacteristic polynomial. Experimental results show that theproduced pattern sequences achieve similar fault coverage aspseudorandom sequences and require about the same testlength. Compared to the well-known self-test methods that insert testregisters, the approach using available arithmetic units saves theadditional gates that are needed to implement test registers, and itavoids performance degradation due to additional delays.

Similar content being viewed by others

References

M.S. Abadir and M.A. Breuer, “A Knowledge-Based System for Designing Testable VLSI Chips,” IEEE Design & Test of Computers, Vol. 2, No.3, pp. 56–68, Aug.1985.

A. Krasniewski and A. Albicki, “Automatic Design of Exhaustively Self-Testing Chips with BILBO Modules,” Proc. International Test Conference, 1985, pp. 362–371.

C. Papachristou, S. Chiou, and H. Harmanani, “A Data Path Synthesis Method for Self-Testable Designs,” Proc. Design Automation Conference, 1991, pp. 378–384.

A.P. Stroele and H.-J. Wunderlich, “Configuring Flip-Flops to BIST Registers,” Proc. International Test Conference, 1994, pp. 939–948.

B. Koenemann, J. Mucha, and G. Zwiehoff, “Built-in Logic Block Observation Techniques,” Proc. Test Conference, NJ, 1979, pp. 37–41.

L.-T. Wang and E.J. McCluskey, “Concurrent Built-in Logic Block Observer (CBILBO),” Proc. International Symposium on Circuits and Systems, 1986, pp. 1054–1057.

M.J. Ohletz, T.W. Williams, and J.P. Mucha, “Overhead in Scan and Self-Test Designs,” Proc. International Test Conference, 1987, pp. 460–470.

S. Gupta, J. Rajski, and J. Tyszer, “Test Pattern Generation Based on Arithmetic Operations,” Proc. International Conference on Computer-Aided Design, 1994, pp. 117–124.

N. Mukherjee, M. Kassab, J. Rajski, and J. Tyszer, “Accumulator Built-in Self Test for High-Level Synthesis,” Proc. VLSI Test Symposium, 1995, pp. 132–139.

I. Voyiatzis, A. Paschalis, D. Nikolos, and C. Halatsis, “Accumulator-Based BIST Approach for Stuck-Open and Delay Fault Testing,” Proc. European Design&Test Conference, 1995, pp. 431–435.

S.W. Golomb, Shift Register Sequences, Holden-Day, San Francisco, 1967.

J. Rajski and J. Tyszer, “Test Response Compaction in Accumulators with Rotate Carry Adders,” IEEE Transactions on CAD, Vol. 12, No.4, pp. 531–539, April 1993.

J. Rajski and J. Tyszer, “Accumulator-Based Compaction of Test Responses,” IEEE Transactions on Computers, Vol. 42, No.6, pp. 643–650, June 1993.

A.P. Stroele, “Test Response Compaction Using Arithmetic Functions,” Proc. VLSI Test Symposium, 1996, pp. 380–386.

A.P. Stroele, “ASelf-Test Approach Using Accumulators as Test Pattern Generators,” Proc. International Symposium on Circuits and Systems, 1995, pp. 2120–2123.

R.L. Graham, D.E. Knuth, and O. Patashnik, Concrete Mathematics, Addison-Wesley, Reading, 1989.

F. Brglez and H. Fujiwara, “A Neutral Netlist of 10 Combinational Benchmark Circuits and a Target Translator in FORTRAN,” International Symposium on Circuits and Systems, 1985.

P.H. Bardell, “Design Considerations for Parallel Pseudorandom Pattern Generators,” Journal of Electronic Testing: Theory and Applications, Vol. 1, No.1, pp. 73–87, Feb. 1990.

H.K. Lee and D.S. Ha, “An Efficient Forward Fault Simulation Algorithm Based on the Parallel Pattern Single Fault Propagation,” Proc. International Test Conference, 1991, pp. 946–955.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Stroele, A.P. BIST Pattern Generators Using Addition and Subtraction Operations. Journal of Electronic Testing 11, 69–80 (1997). https://doi.org/10.1023/A:1008299817888

Issue Date:

DOI: https://doi.org/10.1023/A:1008299817888