Abstract

Bottom-up synthesized graphene nanoribbons and graphene nanoribbon heterostructures have promising electronic properties for high-performance field-effect transistors and ultra-low power devices such as tunneling field-effect transistors. However, the short length and wide band gap of these graphene nanoribbons have prevented the fabrication of devices with the desired performance and switching behavior. Here, by fabricating short channel (L ch ~ 20 nm) devices with a thin, high-κ gate dielectric and a 9-atom wide (0.95 nm) armchair graphene nanoribbon as the channel material, we demonstrate field-effect transistors with high on-current (I on > 1 μA at V d = −1 V) and high I on /I off ~ 105 at room temperature. We find that the performance of these devices is limited by tunneling through the Schottky barrier at the contacts and we observe an increase in the transparency of the barrier by increasing the gate field near the contacts. Our results thus demonstrate successful fabrication of high-performance short-channel field-effect transistors with bottom-up synthesized armchair graphene nanoribbons.

Similar content being viewed by others

Introduction

The electronic, optical and magnetic properties of graphene nanoribbons (GNRs) can be engineered by varying their width and edge structure1,2,3,4,5,6,7,8,9,10,11,12,13. However, traditional methods to pattern GNRs, such as unzipping carbon nanotubes or lithographically defining GNRs from bulk graphene, yield GNRs with rough edges that degrade electronic transport14. Recent experiments have demonstrated bottom-up chemical synthesis of ultra-narrow ( < 2 nm) GNRs with uniform width and atomically-precise edges, in which the width and edge structure of the GNR is determined by the oligophenylene used in the polymerization step1, 2, 4, 7, 9, 10. This synthetic uniformity produces GNRs with high structural and electronic homogeneity, which is required for integration of GNR field-effect transistors (FETs) into large-scale digital circuits15. However, the wide band gap and short length of bottom-up synthesized GNRs have prevented the realization of high-performance FETs16,17,18,19.

Here, we show FETs with 9-atom and 13-atom wide armchair GNRs (9AGNRs and 13AGNRS, respectively). The band gap of ultra-narrow GNRs is very sensitive to its dielectric environment. For instance, the band gap of 7AGNRs obtained via scanning tunneling spectroscopy can vary by as much as 1 eV, depending on whether the substrate is conductive or insulating8. Since our GNR devices are on an insulating substrate, the band gap of the GNRs will be closest to the density functional theory band gap with GW correction8, 12. With a predicted band gap of 2.10 eV for the isolated 9AGNR and 2.35 eV for the 13AGNR12, these are the narrowest band gap GNRs that have been synthesized on a surface with useful length for device fabrication (5AGNRs have a smaller band gap but are only ~ 10 nm long with current synthetic methods6). Thus, we were able to demonstrate high on-current (I on > 1 μA at V d = −1 V) and high I on /I off ~ 105 FETs at room temperature by using 9AGNRs as the channel material and a thin high-κ gate dielectric.

Results

Synthesis and transfer of GNRs

To synthesize the GNRs, the requisite monomer was evaporated onto a Au(111) surface under ultra-high vacuum and heated until it polymerized. Heating the substrate further causes individual polymers to planarize into GNRs (cyclodehydrogenation). The high quality of the GNRs is verified by high-resolution scanning tunneling microscope (STM)1, 2 imaging as shown in Fig. 1a, b.

High-resolution STM GNR characterization and FET structure. a STM image of synthesized 9AGNR on Au with a scale bar of 10 nm (V s = 1 V, I t = 0.3 nA). Inset: High-resolution STM image of 9AGNR on Au (V s = 1 V, I t = 0.5 nA) with a scale bar of 1 nm. b High-resolution STM image of 13AGNR on Au with a scale bar of 2 nm (V s = −0.7 V, I t = 7 nA). c Schematic of the short channel GNRFET with a 9AGNR channel and Pd source-drain electrodes. d Scanning electron micrograph of the fabricated Pd source-drain electrodes with a scale bar of 100 nm

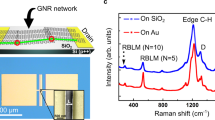

Fabrication of GNRFETs requires the transfer of GNRs from the Au growth surface onto an insulating surface and subsequent device fabrication steps, as described in the Methods. Unfortunately, standard imaging techniques (atomic force microscopy, scanning electron microscopy, transmission electron microscopy, etc.) were not useful in imaging single GNRs on insulating surfaces due to the GNR’s small dimensions ( ~ 30 nm long, ~ 1 nm wide and < 1 nm thick). Instead, we used Raman spectroscopy in order to verify that the structural integrity of the GNRs is maintained throughout the transfer and device fabrication process. As shown in Fig. 2a, the Raman spectrum with 785 nm wavelength excitation of the processed 9AGNRs looks identical to the spectrum taken of the as-grown 9AGNRs on Au. The presence of the radial breathing-like mode (RBLM) peak (311.5 cm−1) is evidence that the GNR width and edge structure is intact throughout device processing20, 21. Unlike 9AGNRs, the RBLM is not visible for the 13AGNR spectrum for either 532 or 785 nm excitation wavelengths due to off-resonance of the excitation (Fig. 2b and Supplementary Fig. 2). Still, the 13AGNRFETs were processed with the same fabrication steps as the 9AGNRFETs and both types of devices exhibit similar transport characteristics (Fig. 3).

Raman spectra of as-grown GNRs on Au and GNRs after transfer and device processing. Raman spectra of a 9AGNRs and b 13AGNRs on the Au(111) growth substrate and after device fabrication shows that the GNRs remain intact. Since the excitation is off-resonance with the 13AGNR absorption, the Raman signal is weak on Au and the RBLM is not visible

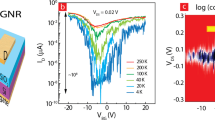

Transport characteristics of 9AGNRs and 13AGNRs gated with 50 nm SiO2 gate oxide. The presence of a SB is confirmed by non-linear current behavior at low drain bias and lack of current saturation at high drain bias for both a 9AGNRs and b 13AGNRs. The weak temperature dependence in the I d −V g behavior in c 9AGNRs and d 13AGNRs indicates that tunneling through the Pd-GNR SBs is the limiting transport mechanism of the device

13AGNRFETs and 9AGNRFETs with thick gate dielectrics

First, we fabricated devices with a nominal 20 nm channel length and a 50 nm SiO2 gate dielectric as illustrated in Fig. 3a. Using the same fabrication methods we made two different types of samples: one with 9AGNRs and one with 13AGNRs. After patterning ~ 300 pairs of electrodes in the transferred GNR area, each defined channel was biased and tested for gate modulation of the current to find devices bridged by a GNR. Of the 300 devices, 28 devices and 29 devices were successfully fabricated for 9AGNR and 13AGNRs, respectively. Taking into account the length distribution of GNRs on the surface, this ~ 10% ratio of bridged contacts to open devices indicates that almost all of the devices found contain one GNR in the channel as demonstrated by Supplementary Fig. 1 and Supplementary Note 1. Finally, GNR-GNR transport was ruled out by confirming that pairs of electrodes with gaps 30 nm or longer showed no conduction.

These 9AGNRFETs and 13AGNRFETs, as shown in Fig. 3 and Supplementary Fig. 3, showed similar electrical behavior due to their similar band gap. The presence of a Schottky barrier (SB) at the Pd-GNR interface is evident by the non-linear behavior at low bias in the I d –V d characteristics22, shown in Fig. 3a, b. To determine the contributions of thermionic vs. tunneling current across the SB, we measured the devices in vacuum at 77, 140, 210, and 300 K. As demonstrated in Fig. 3c, d, there is no significant change in the characteristics at these different temperatures for either 13AGNRFETs or 9AGNRFETs and the off-state current is at the gate leakage level (Supplementary Fig. 4). The weak temperature dependence in the current-voltage characteristics suggests that the limiting transport mechanism is tunneling through the barrier as opposed to thermionic emission over the barrier at the contacts23, 24. If thermionic emission was a significant transport mechanism across the SB, the current should be exponentially dependent on the inverse of temperature. Furthermore, the ambipolar behavior observed at low temperatures is only realistically possible with tunneling contacts, since thermally activated current is suppressed for electrons in a semiconductor with a band gap of > 2 eV. Tunneling contacts with weak temperature dependence have been observed for carbon nanotube FETs and other low-dimensional materials and verified via simulations23,24,25,26. Yet, the I on ~ 100 nA in the devices shown in Fig. 3 is too low for high-performance applications, so the transmission through the SBs must be enhanced to improve the current.

Ionic liquid gating of 9AGNRFETs

Ionic liquid (IL) gating has been previously used to improve the transparency of the SBs in MoS2 27. Thus, we used the IL N,N-diethyl-N-(2-methoxyethyl)-N-methylammonium bis(trifluoromethylsulphonyl-imide) (DEME-TFSI) to improve the electrostatic coupling between the gate electrode and the GNR channel, increase the field at the Pd-GNR interface and improve the transmission through the barriers. The I d –V g behavior of a 9AGNRFET with IL gating is shown in Fig. 4b. This device shows clear enhancement in the on-current to ~ 200 nA at −0.2 V drain bias (as opposed to 3 nA at −0.4 V for the 50 nm SiO2 dielectric device presented in Fig. 4a). The transistor also switches at smaller gate voltages due to the high gate efficiency of the IL.

Ionic liquid gating of a 9AGNRFET at room temperature. a I d −V g characteristics of the device gated by the thick 50 nm SiO2 gate oxide. b I d −V g characteristics of the device gated with the ionic liquid which shows clear ambipolar behavior and improved on-state performance. Inset: ionic liquid (DEME-TFSI) gated 9AGNRFET device schematic

9AGNRFETs with a thin gate dielectric

Since solid dielectric gates must be used for logic device applications, we fabricated scaled 9AGNR devices with a thin HfO2 gate dielectric (effective oxide thickness of around 1.5 nm) as shown in Fig. 5. Resembling the IL device, the local HfO2 back gate is more efficient at improving transmission through the SB than the thick SiO2 global back gate28. As demonstrated by the I d vs. V g shown in Fig. 5, the device exhibits excellent switching characteristics, I on/I off ~ 105, and a high I on ~ 1 μA at V d = −1 V. The SB is still prominent as indicated by the non-linear I d vs. V d characteristics at low bias and the large subthreshold swing (SS) in this device ( ~ 350 mV/dec). Even if tunneling is enhanced by using the thin gate oxide, large SB devices tend to suffer from SS and I on degradation22, 24.

Assuming most of the current is transported by an individual GNR in the channel, the local back gated device performance corresponds to a 0.95 nm GNR-width (100 nm electrode width) normalized current drive of ~ 1000 μA/µm ( ~ 10 μA/µm) at −1 V drain bias. Although some top-down GNRs have higher normalized conductance, the GNRs used here have much larger band gaps29,30,31,32. Therefore, we were able to scale our devices to short channel lengths without affecting the I on/I off. At the same time, the impact of the large SBs on I on was minimized with the improved gate efficiency of the thin high-k dielectric. The expected value of > 20 mA/µm in GNR devices with no SB33 could be attainable by integrating bottom-up synthesized GNRs with smaller band gaps ( ~ 1 eV) and densely aligned GNRs34.

Discussion

We thus successfully demonstrate short-channel FETs with bottom-up synthesized armchair GNRs with excellent switching behavior and on-state performance by aggressively scaling the gate dielectric. Bottom-up GNR devices are, therefore, good candidates for high-performance logic applications, especially with advances in densely aligned GNR synthesis34 as well as narrow band gap GNR growth6. These results motivate the study of GNR growth mechanism in order to improve the average length of GNRs and increase device yield. Our methodology can be applied to other exotic device structures as well, such as tunnel FETs, which incorporate atomically precise GNR heterostructures9, 10, 35.

Methods

9AGNR growth

9AGNRs were synthesized from 3′,6′-dibromo-1,1′:2′,1″-terphenyl precursor monomers7. First, the Au(111)/mica substrate (200 nm Au; PHASIS, Geneva, Switzerland) was cleaned in ultra-high vacuum by two sputtering/annealing cycles: 1 kV Ar+ for ten minutes followed by a 470 °C anneal for ten minutes. Next, the monomer was sublimed onto the Au(111) surface at a temperature of 60–70 °C, with the substrate held at 180 °C. After 2 min of deposition (resulting in approximately half monolayer coverage), the substrate temperature was increased to 200 °C for ten minutes to induce polymerization, followed by annealing at 410 °C for ten minutes in order to cyclodehydrogenate the polymers and form 9-AGNRs.

13AGNR growth

13AGNRs were synthesized using 2,2′-Di((1,1′-biphenyls)-2-yl)-10,10′-dibromo-9,9′-bianthracene building blocks2. Similar to the 9AGNR substrate, the Au(111)/mica substrate (200 nm Au; PHASIS, Geneva, Switzerland) is cleaned in ultra-high vacuum by two sputtering/annealing cycles: 1 kV Ar+ for ten minutes followed by a 450 °C anneal for ten minutes. The monomer was sublimed at 222 °C onto the clean substrate held at room temperature. The sample was then slowly annealed stepwise to 340 °C to form 13AGNRs.

Preparation of 50 nm SiO2 back gates

Using dry oxidation, 50 nm SiO2 was grown on heavily doped 150 mm silicon wafers. Alignment markers and large pads for electrical probing were patterned using standard photolithography and lift-off patterning of 3 nm Cr and 25 nm Pt. The wafer was then diced and individual chips were used for GNR transfer and further device processing.

Preparation of 6.5 nm HfO2 local back gates

Using dry oxidation, 100 nm SiO2 was grown on 150 mm silicon wafers. The local back gates were lithographically patterned and dry etched into the SiO2 followed by lift-off of 3 nm Ti and 17 nm Pt36. 6.5 nm HfO2 was grown in an atomic layer deposition system at 135 °C. Alignment markers and large pads for electrical probing were patterned using standard photolithography and lift-off of 3 nm Cr and 25 nm Pt. The wafer was then diced and individual chips were used for GNR transfer and further device processing.

GNR transfer and patterning of source-drain electrodes

GNR/Au/mica was floated in 38% HCl in water, which caused the mica to delaminate with the Au film remaining floating on the surface of the acid10. The floating gold film was picked up with the target substrate, with the GNRs facing the dielectric surface. Subsequent gold etching in KI/I2 yielded isolated, randomly distributed GNRs with sub-monolayer coverage on the target substrate. After the GNR transfer, poly-methyl methacrylate (molecular weight 950 K) was spun on the chips at 4 Krpm and followed by a 10 min bake at 180 °C. ~ 300 source drain electrodes (100 nm wide, 20 nm gaps) were patterned using a JEOL 6300-FS 100 kV e-beam lithography system and subsequently developed in 3:1 IPA:MIBK at 5 °C. In all, 10 nm Pd was deposited using e-beam evaporation and lift-off was completed in Remover PG at 80 °C.

Raman characterization

Raman characterization of the 9AGNR was performed with a Bruker SENTERRA Raman microscope using a 785 nm diode laser with 10 mW power and a 50× objective lens, resulting in a 1–2 micrometer spot size. No thermal effects were observed under these measurement conditions and an average of three spectra from different points was made for each sample. Raman measurements of the 13AGNR were made with a Horiba Jobin Yvon LabRAM ARAMIS Raman microscope using 532 and 785 nm diode lasers with 10 mW power each and a 50× objective lens, resulting in a 1–2 micrometer spot size. No thermal effects were observed under these measurement conditions and an average of five spectra from different points was made for each sample.

Electrical characterization

Devices were first screened in ambient conditions using a cascade probe station and an Agilent B1500A parameter analyzer. Vacuum and variable temperature measurements were then performed in a Lakeshore probe station. IL devices were measured with a V g sweep speed of 50 mV/s.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Cai, J. et al. Atomically precise bottom-up fabrication of graphene nanoribbons. Nature 466, 470–473 (2010).

Chen, Y.-C. et al. Tuning the band gap of graphene nanoribbons synthesized from molecular precursors. ACS Nano 7, 6123–6128 (2013).

Narita, A. et al. Synthesis of structurally well-defined and liquid-phase-processable graphene nanoribbons. Nat. Chem. 6, 126–132 (2014).

Narita, A., Wang, X.-Y., Feng, X. & Müllen, K. New advances in nanographene chemistry. Chem. Soc. Rev. 44, 6616–6643 (2015).

Ruffieux, P. et al. On-surface synthesis of graphene nanoribbons with zigzag edge topology. Nature 531, 489–492 (2016).

Kimouche, A. et al. Ultra-narrow metallic armchair graphene nanoribbons. Nat. Commun. 6, 10177 (2015).

Talirz, L. et al. On-surface synthesis and characterization of 9-atom wide armchair graphene nanoribbons. ACS Nano 11, 1380–1388 (2017).

Talirz, L., Ruffieux, P. & Fasel, R. On-surface synthesis of atomically precise graphene nanoribbons. Adv. Mater. 28, 6222–6231 (2016).

Chen, Y.-C. et al. Molecular bandgap engineering of bottom-up synthesized graphene nanoribbon heterojunctions. Nat. Nanotechnol. 10, 156–160 (2015).

Cai, J. et al. Graphene nanoribbon heterojunctions. Nat. Nanotechnol. 9, 896–900 (2014).

Nakada, K., Fujita, M., Dresselhaus, G. & Dresselhaus, M. S. Edge state in graphene ribbons: nanometer size effect and edge shape dependence. Phys. Rev. B 54, 17954–17961 (1996).

Yang, L., Park, C.-H., Son, Y.-W., Cohen, M. L. & Louie, S. G. Quasiparticle energies and band gaps in graphene nanoribbons. Phys. Rev. Lett. 99, 186801 (2007).

Hsu, H. & Reichl, L. E. Selection rule for the optical absorption of graphene nanoribbons. Phys. Rev. B 76, 45418 (2007).

Yoon, Y. & Guo, J. Effect of edge roughness in graphene nanoribbon transistors. Appl. Phys. Lett. 91, 73103 (2007).

Franklin, A. D. Electronics: the road to carbon nanotube transistors. Nature 498, 443–444 (2013).

Bennett, P. B. et al. Bottom-up graphene nanoribbon field-effect transistors. Appl. Phys. Lett. 103, 253114 (2013).

Abbas, A. N. et al. Deposition, characterization, and thin-film-based chemical sensing of ultra-long chemically synthesized graphene nanoribbons. J. Am. Chem. Soc. 136, 7555–7558 (2014).

Abbas, A. N. et al. Vapor-phase transport deposition, characterization, and applications of large nanographenes. J. Am. Chem. Soc. 137, 4453–4459 (2015).

Gao, J. et al. Ambipolar transport in solution-synthesized graphene nanoribbons. ACS Nano 10, 4847–4856 (2016).

Verzhbitskiy, I. A. et al. Raman fingerprints of atomically precise graphene nanoribbons. Nano Lett. 16, 3442–3447 (2016).

Vandescuren, M., Hermet, P., Meunier, V., Henrard, L. & Lambin, P. Theoretical study of the vibrational edge modes in graphene nanoribbons. Phys. Rev. B 78, 195401 (2008).

Hazeghi, A., Krishnamohan, T. & Wong, H. S. P. Schottky-barrier carbon nanotube field-effect transistor modeling. IEEE Trans. Electron Devices 54, 439–445 (2007).

Appenzeller, J., Radosavljević, M., Knoch, J. & Avouris, P. Tunneling versus thermionic emission in one-dimensional semiconductors. Phys. Rev. Lett. 92, 48301 (2004).

Appenzeller, J. et al. Field-modulated carrier transport in carbon nanotube transistors. Phys. Rev. Lett. 89, 126801 (2002).

Chen, Z., Appenzeller, J., Knoch, J., Lin, Y. & Avouris, P. The role of metal−nanotube contact in the performance of carbon nanotube field-effect transistors. Nano Lett. 5, 1497–1502 (2005).

Perebeinos, V., Tersoff, J. & Haensch, W. Schottky-to-Ohmic crossover in carbon nanotube transistor contacts. Phys. Rev. Lett. 111, 236802 (2013).

Zhang, Y., Ye, J., Matsuhashi, Y. & Iwasa, Y. Ambipolar MoS2 thin flake transistors. Nano Lett. 12, 1136–1140 (2012).

Franklin, A. D. et al. Sub-10 nm carbon nanotube transistor. Nano Lett. 12, 758–762 (2012).

Jiao, L., Zhang, L., Wang, X., Diankov, G. & Dai, H. Narrow graphene nanoribbons from carbon nanotubes. Nature 458, 877–880 (2009).

Li, X., Wang, X., Zhang, L., Lee, S. & Dai, H. Chemically derived, ultrasmooth graphene nanoribbon semiconductors. Science 319, 1229–1232 (2008).

Wang, X. & Dai, H. Etching and narrowing of graphene from the edges. Nat. Chem 2, 661–665 (2010).

Jacobberger, R. M. et al. Direct oriented growth of armchair graphene nanoribbons on germanium. Nat. Commun. 6, 8006 (2015).

Luisier, M., Lundstrom, M., Antoniadis, D. A. & Bokor, J. Ultimate device scaling: intrinsic performance comparisons of carbon-based, InGaAs, and Si field-effect transistors for 5 nm gate length. 2011 International Electron Devices Meeting, Washington, DC, 2011, pp. 11.2.1-11.2.4.

Linden, S. et al. Electronic structure of spatially aligned graphene nanoribbons on Au(788). Phys. Rev. Lett. 108, 216801 (2012).

Zhao, P., Chauhan, J. & Guo, J. Computational study of tunneling transistor based on graphene nanoribbon. Nano Lett. 9, 684–688 (2009).

Franklin, A. D. & Chen, Z. Length scaling of carbon nanotube transistors. Nat. Nanotechnol. 5, 858–862 (2010).

Acknowledgements

This work was supported in part by the Office of Naval Research BRC program under Grant N00014-16-1-2229, DARPA, the U.S. Army Research Laboratory and the U.S. Army Research Office under contract/grant number W911NF-15-1-0237, the Swiss National Science Foundation, the DFG Priority Program SPP 1459 and Graphene Flagship (No. CNECT-ICT-604391). Work at the Molecular Foundry was supported by the Office of Science, Office of Basic Energy Sciences, of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231. Additional support was received from the Director, Office of Science, Office of Basic Energy Sciences, Materials Sciences and Engineering Division, of the U.S. Department of Energy under Contract No. DE-AC02-05-CH11231, within the sp2-Bonded Materials Program (KC2207), which provided for development of the IL gating method. J.P.L. is supported by the Berkeley Fellowship for Graduate Studies and by the NSF Graduate Fellowship Program. We would like to thank Dr P. Bennett for useful discussions.

Author information

Authors and Affiliations

Contributions

J.P.L., B.Y.C., R.B., and J.B. fabricated and measured the devices on SiO2. J.P.L., J.L., K.L., S.W., J.B., and E.Y. fabricated and measured the devices on HfO2. W.S. and A.Z. performed the IL gating experiments. A.F., G.B.B., P.R., and R.F. performed growth, transfer, STM, and Raman spectroscopy of 9AGNRs. N.K., W.C., C.C., Z.P., and M.C. performed growth and STM measurements of 13AGNRs. J.P.L. and J.B. transferred and performed Raman spectroscopy of 13AGNRs. F.F. synthesized the 13AGNR precursor molecule. T.D., A.N., X.F., and K.M. synthesized the 9AGNR precursor molecule. All the authors discussed and wrote the paper.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Llinas, J., Fairbrother, A., Borin Barin, G. et al. Short-channel field-effect transistors with 9-atom and 13-atom wide graphene nanoribbons. Nat Commun 8, 633 (2017). https://doi.org/10.1038/s41467-017-00734-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-017-00734-x

This article is cited by

-

Stepwise on-surface synthesis of nitrogen-doped porous carbon nanoribbons

Communications Chemistry (2024)

-

Graphene nanoribbons grown in hBN stacks for high-performance electronics

Nature (2024)

-

Porphyrin-fused graphene nanoribbons

Nature Chemistry (2024)

-

Influence of Film Thickness on Nanofabrication of Graphene Oxide

Nanomanufacturing and Metrology (2024)

-

Design and synthesis of graphene nanoribbons from organic precursors

Chemical Papers (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.