Abstract

The origin of threshold voltage instability with gate voltage in MoS2 transistors is poorly understood but critical for device reliability and performance. Reversibility of the temperature dependence of hysteresis and its inversion with temperature in MoS2 transistors has not been demonstrated. In this work, we delineate two independent mechanisms responsible for thermally assisted hysteresis inversion in gate transfer characteristics of contact resistance-independent multilayer MoS2 transistors. Variable temperature hysteresis measurements were performed on gated four-terminal van der Pauw and two-terminal devices of MoS2 on SiO2. Additional hysteresis measurements on suspended (~100 nm air gap between MoS2 and SiO2) transistors and under different ambient conditions (vacuum/nitrogen) were used to further isolate the mechanisms. Clockwise hysteresis at room temperature (300 K) that decreases with increasing temperature is shown to result from intrinsic defects/traps in MoS2. At higher temperatures a second, independent mechanism of charge trapping and de-trapping between the oxide and p+ Si gate leads to hysteresis collapse at ~350 K and anti-clockwise hysteresis (inversion) for temperatures >350 K. The intrinsic-oxide trap model has been corroborated through device simulations. Further, pulsed current–voltage (I–V) measurements were carried out to extract the trap time constants at different temperatures. Non-volatile memory and temperature sensor applications exploiting temperature dependent hysteresis inversion and its reversibility in MoS2 transistors have also been demonstrated.

Similar content being viewed by others

Introduction

Among two-dimensional materials, graphene1,2 was the first to be isolated and studied with respect to electronic applications. Due to lack of an energy bandgap in graphene, other 2D materials such as layered transition metal dichalcogenides (TMDs) comprising a wide selection of materials with different bandstructures, and therefore different electrical and optical properties, have garnered significant attention.3,4,5 Molybdenum disulfide (MoS2) has emerged as a prospective candidate for transistor applications. The presence of a direct bandgap (~1.8 eV) in monolayer form and an indirect bandgap (~1.2 eV) in multilayer MoS2 makes it a promising channel material for field effect transistors (FETs).6 High I ON /I OFF ratio (>106), low sub-threshold swing, absence of dangling bonds, negligible OFF current and high effective mass (to reduce short channel effects) are some of the key advantages reported for MoS2 transistors in various studies.7,8,9 Other than logic applications, MoS2 is also being actively researched for use in display technology, optoelectronics, memories and energy harvesting.10

Reliability and performance of MoS2 transistor devices used in these various applications are highly dependent on the measure of threshold voltage instability with changing gate voltage (V GS) sweep directions.11,12,13,14 The occurrence of hysteresis screens out intrinsic properties of MoS2 and limits its potential in realizing expected device performance.15 Comparison of previous reports on hysteresis in MoS2 devices with this work is listed in Table 1. Hysteresis observed in previous studies16,17,18 has been attributed to several possibilities such as adsorption of water molecules,18,19,20,21 oxide traps close to MoS2,22 oxide–MoS2 interface traps23,24 and gate voltage stress effects.25 A lack of uniformity in the hysteresis data and consensus on its origin among the reports listed in Table 1 results, at least partly, from differences in measurement conditions as well as device architecture. Impact of temperature, temperature-dependent contact resistance, ambient conditions, sweep rate, ON pulse width (drain/gate) and presence of interface and oxide traps through dielectric proximity to MoS2 (suspended vs. supported devices) are critical to the understanding of hysteresis in MoS2 devices. As can be seen in Table 1, some of these aspects have not been looked at in detail in previous reports. Further, reversibility of hysteresis inversion (clockwise to anti-clockwise) with temperature in MoS2 transistors has not yet been demonstrated.

This work reports a comprehensive study that isolates and identifies the contributions of two different and independent mechanisms to hysteresis in multilayer MoS2 FETs. We demonstrate, for the first time, temperature dependent reversible hysteresis inversion (from clockwise (CW) at 300 K to anti-clockwise (ACW) for >350 K) in four-terminal contact resistance-independent, MoS2 van der Pauw (vdP) devices. VdP correction allows to compensate for the errors that might occur in hysteresis analysis due to arbitrarily shaped MoS2 flakes.26,27 Effect of contact resistance on hysteresis was also studied by comparing two-terminal and four-terminal gated devices (Fig. S6 in Supplementary Information). Almost similar magnitude of hysteresis, in both two and four-terminal MoS2 devices indicates that the contact resistance has negligible impact on hysteresis. Further, similar evolution of hysteresis with temperature in two and four-terminal MoS2 devices indicates that the contact resistance does not change significantly with temperature. Thermally assisted hysteresis inversion requires hysteresis crossover at a critical temperature that is shown to vary with the maximum applied gate voltage. Measurements were carried out at different temperatures, ambient conditions as well as in both supported and suspended transistor configurations to examine the effect of traps and adsorbates on hysteresis in the MoS2 FETs. Analysis of the hysteresis data reveals that two different mechanisms are at play, one involving intrinsic defects/traps native to MoS2 (i.e. atomic interlayer and intralayer point defects—for e.g. molybdenum and/or sulfur vacancies28) at room temperature, and the second due to extrinsic charge exchange between SiO2 and p+ Si gate at higher temperatures (>350 K).29 Trap time constants at different temperatures were extracted using pulsed I–V measurements. Moreover, trap densities in MoS2 and the gate oxide were extracted from the experimental data and used in simulations to reproduce the experimental inversion of hysteresis, thereby validating the intrinsic-oxide trap model.

Although hysteresis is usually seen as an obstacle for device applications, a recent work has shown that hysteresis can be exploited for thermally assisted non-volatile memory applications.29 The requirement of high temperature (495 K)29 to perform read and write operations is still a roadblock for the realization of fully functional heat-assisted memories. By exploiting hysteresis and its inversion, we have demonstrated thermally assisted programmable non-volatile memory at a much lower temperature (375 K) than previously reported.29 Further, the variation in difference of forward (FS) and reverse sweep (RS) conductances over a wide temperature range of 100 K, as well as the reversibility of the hysteresis, can be harnessed for temperature sensing applications.

Results and discussion

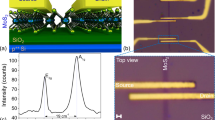

A schematic of back-gated MoS2 vdP devices used in this work is shown in Fig. 1a. MoS2 sheets were mechanically exfoliated1,5,6 from MoS2 crystal using adhesive tape on a heavily doped p-type silicon substrate with a 280 nm SiO2 layer. MoS2 flakes were then identified using an optical microscope. Further, the thickness and the number of layers were confirmed using Atomic Force Microscopy (AFM) and Raman spectroscopy. Figure 1b shows an AFM line scan across the MoS2 flake, with the AFM image as inset. This was followed by patterning of source/drain contacts using electron beam lithography and metal deposition. Optical micrograph of a typical MoS2 vdP device is shown in Fig. 1c. Contact resistance and its temperature dependence30 can affect the magnitude of the hysteresis data as well as its evolution with temperature. At the same time it can screen out contributions to hysteresis from other mechanisms. Therefore, devices were fabricated in vdP configuration to eliminate the contact resistance using four-terminal measurements.31,32,33 Fig. 1d shows the measurement schematics of the vdP MoS2 device in A and C configurations. In A (C) configuration, current (I + = I − = I) is passed between terminals 1 and 2 (2 and 4) by applying a fixed set voltage of 1 V. The resulting potential drop (V + − V −) is measured between terminals 3 and 4 (1 and 3). More details on van der Pauw measurements are given in Supplementary Information S1. Sheet conductance \(\left( {\sigma _S = \rho _S^{ - 1}} \right)\) was calculated using vdP equation, \(e^{ - \pi {\textstyle{{R_{\mathrm{A}}} \over {\rho _{\mathrm{S}}}}}} + e^{ - \pi {\textstyle{{R_{\mathrm{C}}} \over {\rho _{\mathrm{S}}}}}} = 1\), where R A and R C are the resistances measured in configurations A and C, respectively26 (shown in Fig. 1d).

a 3D schematic of an MoS2 FET in van der Pauw configuration. b AFM line scan (green line) across the edge of the MoS2 flake shown in the inset. c Optical micrograph of a multilayer MoS2 van der Pauw device. d Different van der Pauw configurations used to measure the sheet resistance (ρ S) for varying V GS

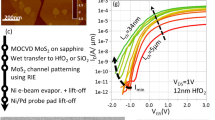

Figure 2 shows transfer characteristics (σ S−V GS) of a supported (on SiO2) multilayer MoS2 vdP device at different temperatures. These measurements were done in nitrogen ambient. From the transfer characteristics, we estimate a field effect mobility (μ FE) of ~16–80 cm2/Vs using μ FE = \(\frac{{\partial \sigma _S}}{{\partial V_{GS}}} \times \frac{1}{{\left( {C_{ox}} \right)}}\), where gate oxide capacitance per unit area \(C_{ox} = \epsilon _0\epsilon _r{\mathrm{/}}d\), \(\epsilon _r = 3.9\) and the oxide thickness, d = 280 nm. ΔV TH is the difference between RS (V GS = +100 to −100 V) and FS (V GS = −100 to +100 V) threshold voltages. Clockwise hysteresis at 300 K (positive ΔV TH) shown in Fig. 2a, reduces as the temperature increases to 325 K (Fig. 2b), and crosses zero at ~350 K (shown in Fig. 2c). Further increase in temperature results in anti-clockwise hysteresis (negative ΔV TH) as shown in Fig. 2d, indicating hysteresis inversion. The hysteresis direction (clockwise at room temperature18,22,23 and anti-clockwise at high temperature29) is the same as stated in earlier reports. However, the reasons given for hysteresis in these reports such as adsorbates, oxide and interface traps do not explain hysteresis inversion and its reversibility. The critical crossover temperature at which ΔV TH = 0 is found to vary with the maximum gate voltage \(\left( {V_{GS}^{max}} \right)\). For example, hysteresis crossover occurred at a higher temperature (425 K) for small \(V_{GS}^{max}\) (−40 to +80 V) compared to 350 K for \(V_{GS}^{max}\) of ±100 V, as shown in Supplementary Information S2. Figure 2f shows ΔV TH for increasing (300–500 K) and decreasing (500–300 K) temperature sweeps. Hysteresis changes from clockwise at 300 K to anti-clockwise at 500 K for increasing temperature sweep (300–500 K). The transition of hysteresis from anti-clockwise at 500 K back to clockwise at room temperature for decreasing temperature sweep implies that the hysteresis inversion is reversible.

Transfer characteristics of a four-terminal MoS2 vdP device for varying temperature (300–400 K), show a clockwise hysteresis at 300 K, b hysteresis reduction with increase in temperature, c nearly zero hysteresis at 350 K, and, anti-clockwise hysteresis at d 375 K and e 400 K. f Experimentally extracted ΔV TH variation with increasing and decreasing temperature sweeps from 300–500 K shows reversible hysteresis inversion

To understand the origin of the hysteresis phenomena described above, we examine different hysteresis mechanisms (shown in Fig. 3 and Table 1) considered in previous studies.16,17,18,19,22,23,25 Adsorbate mediated hysteresis mechanism18,19 is shown in Fig. 3a. For large positive gate bias, water and oxygen molecules get attracted towards the MoS2 surface. These adsorbed molecules capture electrons from MoS2, which leads to electron depletion and an increase in the threshold voltage. For large negative gate bias these trapped electrons are released from adsorbed molecules into the MoS2 channel which reduces V TH.19 This leads to a positive ΔV TH and therefore, clockwise hysteresis. However, our results do not support adsorbate mediated hysteresis because, (1) for measurements done in a dry vacuum/nitrogen ambiance increasing the temperature should reduce the amount of absorbates on MoS2, and hence decrease the hysteresis until it collapses (shown in Fig. 3a). However, further increase in temperature would not result in anti-clockwise hysteresis (negative ΔV TH), and, (2) loss of absorbates implies that hysteresis cannot be recovered by decreasing temperature to room temperature (shown in Fig. 2f). Hysteresis due to mobile ions34,35 (Na+ and K+) in the oxide is shown in Fig. 3b. Depending on the gate voltage, mobile ions come close to MoS2 (onset of RS, V GS = 100 V) or close to gate (onset of FS, V GS = −100 V). This results in anti-clockwise hysteresis at 300 K that increases at higher temperature which is inconsistent with hysteresis collapse and inversion observed in our devices. Another possible hysteresis mechanism due to oxide traps close to MoS2 is shown in Fig. 3c. V TH increases for large positive gate bias due to electron trapping in SiO2, whereas electron release from the oxide traps into MoS2 at large negative gate bias decreases the V TH. This mechanism leads to a positive ΔV TH (i.e. clockwise hysteresis) at room temperature and ΔV TH increases with temperature due to enhanced thermally assisted trapping and de-trapping22 which does not explain the hysteresis inversion seen in our devices. To further understand the exchange of electrons between SiO2 and MoS2 (shown in Fig. 3c), we compared the hysteresis behavior of two-terminal supported and suspended transistors. Comparable magnitude of hysteresis in suspended (~44 V) and supported devices (~65 V) at 300 K (Supplementary Information S3) indicates that the contribution to hysteresis from exchange of electrons between oxide and MoS2, and from the reduced effective gate voltage due to the additional ~100 nm air-gap between SiO2 and the MoS2 flake is small. Clockwise nature of the hysteresis at 300 K and its reduction with increase in temperature due to intrinsic traps is consistent with similar results for suspended devices. However, variable temperature measurements on suspended devices do not show hysteresis crossover for the same applied voltage and temperature values as in the case of supported ones, likely due to reduced effect of trapped oxide charges, gate field, and temperature (as air has low thermal conductivity than SiO2) with the additional ~100 nm air-gap. Hysteresis mechanisms due to oxide traps close to p+ Si gate is shown in Fig. 3d. In a recent study, He et al. have shown zero hysteresis at room temperature and negative hysteresis (anti-clockwise) at high temperatures (>350 K) in monolayer MoS2 FET due to charge tunneling between the oxide and the p+ Si gate.29 The possibility of the existence of oxide traps nearer to the p+ Si gate is more than their existence close to MoS2, due to the thermal oxidation process on p+ Si for gate oxide formation.36 We will refer to oxide traps near p+ Si as ‘oxide traps’ in further discussion. Hysteresis due to intrinsic/interface defects is illustrated in Fig. 3e. It reduces with increasing temperature and eventually becomes zero for high temperature as shown in Fig. 3e. First consider the case of low temperatures for intrinsic/interface defects/traps. At the onset of FS (V GS = −100 V), the channel is fully depleted and there is insufficient thermal energy for bound electrons to get trapped. Conversely, at the onset of RS (V GS = 100 V), the channel has significant free carriers which quickly fill traps causing a decrease in conduction, and clockwise hysteresis is observed. However, at higher temperatures, the traps become thermally available at all values of V GS and therefore any hysteresis is no longer observed above a threshold temperature. Though, both interface (MoS2/SiO2) and intrinsic (MoS2) traps distributed in energy bandgap show clockwise hysteresis at RT and collapse at HT, significant hysteresis in suspended transistors (Supplementary Information S3) suggests that intrinsic traps are the primary cause of hysteresis in MoS2 at RT. A more detailed explanation of hysteresis due to intrinsic and oxide traps is given in Fig. 5.

Schematic representation of different models used to explain hysteresis with band diagrams and their corresponding effect on transfer curves at room temperature (RT) and high temperature (HT). a Electron capture/release by adsorbates, where a large positive gate voltage attracts adsorbates on MoS2 surface that act as dopants. This effect should diminish at higher temperatures due to desorption. b Gate voltage dependent spatial distribution of mobile ions in the oxide gives anti-clockwise hysteresis at RT. c Thermally activated oxide traps (close to MoS2) that can capture and release electrons from MoS2. A negative gate bias releases electrons trapped at the SiO2–MoS2 interface into the MoS2 channel, leading to positively charged traps, whereas a large positively biased gate results in electron capture, resulting in electrically neutral traps. d charge exchange between the gate and the oxide results in anti-clockwise hysteresis mainly at HT. e Intrinsic/interface defects/traps in MoS2 cause hysteresis primarily at RT and collapses at HT

Van der Pauw measurements in different configurations (Fig. 1d) reinforce the presence of intrinsic traps/defects in the multilayer MoS2 channel, which could be both, interlayer and intralayer defects (i.e. atomic point defects such as molybdenum and/or sulfur vacancies), unlike monolayer MoS2 which does not show any clockwise hysteresis at room temperature29 likely due to the absence of interlayer traps and smaller number of intralayer defects. The advantage of using R A/R C measurements is that they allow the gate-dependent homogeneity of charges to be determined.27 This information can let us know at what temperatures doping inhomogeneities exist (Fig. 4a), and therefore at what temperatures they may contribute to hysteresis behaviour. Resistance calculated in configurations A and C must be equal for defect/trap free MoS2.27 However, non-uniform sheet conductance due to defects in MoS2 makes the current path different in A and C configurations resulting in different R A and R C values.27 Large changes in R A/R C ratio at 300 K (shown in Fig. 4a) for varying gate voltage confirms non-uniformity in local sheet conductance as shown in Fig. 4b i, which is most likely due to non-uniform intrinsic defects in the MoS2 flake.27,37 Constant R A/R C ratio with varying gate voltage at high temperatures results from increase in charge density due to both de-trapping and increase in intrinsic concentration (shown in Fig. 4c ii). This increase in free carriers significantly reduces the effect of defects resulting in uniform charge density (sheet conductance) as shown in Fig. 4b ii.

a Change in R A/R C with gate voltage indicates defect-induced variation in local sheet conductance. For defect-free MoS2, R A/R C ratio will be constant. b Schematic charge density plots at RT and HT where yellow regions represent low charge density (high defect density) areas. c Energy band diagram at ~400 K shows increase in charge density through de-trapping and increased intrinsic carrier concentration which reduces the effect of defects as shown in (b) ii

A detailed analysis of the transfer characteristics at 300 K (Fig. 2a) and 400 K (Fig. 2e) is shown through corresponding band diagrams for FS and RS in Fig. 5a, b (i) and (ii), respectively. To explain clockwise hysteresis at RT that collapses at higher temperatures, we propose a model based on temperature dependent trapping/de-trapping of electrons associated with intrinsic traps in the MoS2 channel that can only be observed in devices with a fully depleted channel.38 Schematic energy band diagrams perpendicular to the channel are shown in Fig. 5 for V GS = 100 and −100 V. Onset of RS (100 V) and FS (−100 V) will affect the entire RS and FS range, respectively, considering deep level traps that require times longer than the sweep times to trap/de-trap electrons. The different amount of trapped charges at the onset of FS and RS result in clockwise hysteresis at 300 K as shown in Fig. 5a i. When the temperature is increased, filled-traps close to the conduction band (onset of RS) get empty, while empty-traps close to the valence band (onset of FS) get filled (Fig. 5a ii). Hence, reduction in the difference of trapped charges in FS and RS reduces hysteresis. As the temperature is increased further, a situation arises when all the traps above the intrinsic energy-level (E i) are empty and completely filled below E i in both FS and RS (same probability of trapping and de-trapping at E i ensures no further change in trapped charges with temperature). Equal number of filled and empty traps in FS and RS implies similar V TH values leading to a collapse of the hysteresis (ΔV TH = 0 V).

Energy band diagram schematics at the onset of FS (V GS = −100 V) and RS (V GS = +100 V) for 300 and 400 K showing key mechanisms responsible for hysteresis. a Temperature dependent trapping (1) in FS and de-trapping (2) in RS of intrinsic traps in MoS2 channel. (i) Trapped (de-trapped) charges for reverse (forward) sweep at 300 K result in increase (decrease) in V TH and hence, clockwise hysteresis. (ii) Increase in temperature enhances the de-trapping in RS and trapping in FS. Further, increase in temperature (~400 K) results in equal number of trapped charges in both FS and RS resulting in hysteresis collapse (ΔV TH = 0 V). b Temperature dependent tunneling into oxide from p+ Si gate (3) and tunneling from oxide into p+ Si gate (4). (i) Lack of tunneling at 300 K indicates mechanisms 3–4 are insignificant and there is no hysteresis due to oxide traps. (ii) At high temperatures (~400 K) electrons will tunnel into (out of) gate oxide for large negative (positive) bias which results in increase (decrease) in V TH for forward (reverse) sweep and hence, anti-clockwise hysteresis

However, Fig. 2f shows ΔV TH going from positive to negative values at a crossover temperature and becoming zero at a temperature lower than what is expected solely from intrinsic traps. This suggests another hysteresis mechanism arising from charge exchange between the gate and gate oxide29 at play, which starts at a temperature lower than the crossover temperature but with an opposite sign of ΔV TH. Anti-clockwise hysteresis emerges when the temperature is increased beyond 350 K. At room temperature, carriers in the gate do not have sufficient energy to access traps within the oxide and hence they do not contribute to the hysteresis at 300 K (shown in Figs. 3e and 5b i). However, increased thermal energy at higher temperatures (>350 K) allows these sites to participate in carrier trapping/de-trapping (shown in Figs. 3d and 5b ii). The activation energy associated with filling of deep traps in SiO2 has been estimated to be ~130 meV.29 This is gained in the form of thermal energy at higher temperatures leading to electron injection from the gate into the oxide for large negative V GS. These trapped charges in the oxide cause a shift towards more positive V TH for FS. On the contrary, a large positive V GS transfers the trapped charge carriers back into the gate resulting in a shift towards more negative V TH for RS. Higher V TH for FS as compared to RS implies a negative ΔV TH or anti-clockwise hysteresis. Variation of the FS and RS transconductance peaks with V GS and temperature as shown and analyzed in Supplementary Information S5 further validates the intrinsic-oxide trap model.

Hysteresis primarily occurs due to charge trapping and de-trapping at interface/intrinsic or oxide traps. Pulsed I − V measurements were performed on two-terminal devices to extract the time response of traps at different temperatures, where one of the contacts is defined as source and the other as drain. Since traps have a certain time constant, they will not respond when the ON pulse width is smaller than this value, resulting in reduced hysteresis.39 Therefore, we extracted the trap time constants at different temperatures, to determine the minimum ON pulse (drain/gate) width for traps to respond. Figure 6a shows the gate and drain pulses and biases applied to MoS2 FETs. Change in drain current during the first 40 μs of the 100 μs drain pulse is shown in Fig. 6b, c for 300 and 475 K, respectively. The drain current (I DS) is best fitted (red line) with I DS = I 0 + A.exp(−(t − t 0)/τ), where I 0 is the steady state drain current, A is a fitting parameter, t is the time, t 0 is the beginning time of the drain pulse and τ is the trap time constant. This equation yields trap time constant values of ~1.5 μs for intrinsic traps at 300 K and ~6.5 μs for oxide traps close to p+ Si at 475 K. The extracted oxide trap time constant is similar to values reported in previous reports on oxide traps close to the p+ Si–SiO2 interface40 but smaller than the oxide trap time constant close to the MoS2–SiO2 interface.41 The pulse width should be larger than these trap time constants to ensure participation of all traps in hysteresis. Another important factor which affects the hysteresis is the sweep rate (S) of transfer characteristics, S = \(\frac{{\Delta V}}{{t_{\mathrm{s}}}}\), which was varied from 0.3 to 30 V/s by changing the voltage step size (ΔV) for a given sampling time t s. Low sweep rate ensures that nearly all the traps are taking part in the hysteresis phenomenon.42 We also varied the measurement frequency, f = \(\frac{1}{{N \times t_{\mathrm{s}}}}\) from 0.002 to 0.27 Hz, where N is the number of voltage step points.42 However, we did not see any significant change in ΔV TH.

a Schematic diagram of gate and drain pulse applied to MoS2 transistor. b, c Change in drain current in response to drain pulse time shown in Fig. 6a at 300 and 475 K, respectively

Inversion of hysteresis with temperature mediated by the two independent mechanisms of intrinsic and oxide traps is illustrated in the schematic shown in Fig. 7a. The solid red line shows the effect of hysteresis due to intrinsic traps in MoS2. Here, ΔV TH reduces with increasing temperature and eventually becomes zero for high temperature. The solid green line shows ΔVTH to be zero at room temperature and negative at high temperature resulting from charge tunneling between the oxide and the gate. The algebraic sum of these two hysteresis curves (black dotted line) is qualitatively similar to the data shown in Figs. 2f and 7b. The difference between RS and FS V TH, ΔV TH = \(q\frac{{\Delta N_{\mathrm{T}}}}{{C_{{\mathrm{ox}}}}}\) was used to extract the trap density ΔN T in cm−2 (shown in Fig. 7b).22 Trap density extracted at room temperature was normalized with MoS2 flake thickness to give the total intrinsic trap density considering that hysteresis at low temperature stems from intrinsic MoS2 traps. On the contrary, anti-clockwise hysteresis at 400 K has been attributed to the charge stored in the gate oxide depending on the gate voltage. Therefore, trap density calculated at 400 K was normalized to oxide thickness to give the total oxide trap density. To further validate the proposed intrinsic-oxide trap model for hysteresis, technology computer-aided design (TCAD) device simulations were performed using the experimental intrinsic and oxide trap densities as described in more detail in Supplementary Informations S7 and S8. Consistent with the experimental data, Fig. 8a shows clockwise hysteresis at room temperature that collapses at a crossover temperature of ~350 K as shown in Fig. 8b. Figure 8c shows anti-clockwise hysteresis due to exchange of charge between the gate and the oxide traps, thereby reproducing the experimentally observed thermally assisted hysteresis inversion.

a Schematic showing expected evolution of ΔV TH for two different hysteresis mechanisms with temperature. The solid red line shows clockwise hysteresis due to intrinsic traps and the solid green line shows anti-clockwise hysteresis at high temperature which results from charge exchange between the gate and the oxide. The dotted black line shows the combined effect due to both intrinsic (MoS2 and MoS2–SiO2) and oxide traps. b Experimentally extracted ΔV TH for monolayer29 and various vdP multilayer (this work) MoS2 devices and extracted trap density variation with temperature. Error bars indicate variation in the ΔV TH values

Device simulations using experimental intrinsic and oxide trap densities show, a clockwise hysteresis due to intrinsic traps at RT (300 K), b hysteresis collapse at a crossover temperature of 350 K, and, c anti-clockwise hysteresis due to charge exchange between oxide traps and the p+ Si gate, thereby validating the intrinsic-oxide trap model for hysteresis

We demonstrate two possible applications using thermally assisted hysteresis inversion in MoS2. The hysteresis transfer curve can be exploited for non-volatile memory applications. At 375 K, the dominating mechanism is tunneling of electrons into the gate oxide from the gate which gives fairly uniform transfer characteristics throughout the operating window. We would like to emphasize that the working temperature of 375 K is lower compared to MoS2 devices demonstrated in previous studies.29 More details are available in Supplementary Information S9. Hysteresis inversion can be exploited for power reduction in heavy-‘0’ and heavy-‘1’ digital applications where the occurrence of one state (state ‘0’/‘1’) is more frequent than the other. Depending on the case, one can assign an operating temperature for the device which has lower read conductance for the more frequent state, ‘0’ or ‘1’. For the devices in this work, heavy-‘0’ and heavy-‘1’ conditions can be operated at 375 and 300 K respectively. More details are available in Supplementary Information S10. This device can also be used as a temperature sensor by mapping the differential conductance (Δσ S = σ FS − σ RS) at a given V GS to different operating temperatures. More details are available in Supplementary Information S9. This data can be used as a look-up table to calibrate the sensor as well as read out the existing temperature using appropriate intra/extra-polation techniques.

In conclusion, this work demonstrates thermally assisted reversible hysteresis inversion in contact resistance-independent, gated few layer MoS2 vdP devices. By analyzing measurements in varying ambient (vacuum vs. nitrogen) conditions and configurations (supported vs. suspended), as well as accounting for the nature of hysteresis (CW vs. ACW) and its reversibility using temperature, we exclude the role of adsorbates, interface traps and oxide traps close to MoS2 in giving rise to hysteresis. Instead, we show that intrinsic MoS2 traps give rise to CW hysteresis at RT that decreases with temperature and charge exchange between the gate and gate oxide traps at higher temperatures results in ACW hysteresis. Device simulations incorporating experimental intrinsic and oxide trap densities are shown to reproduce temperature dependent hysteresis inversion reinforcing the intrinsic-oxide trap model, which is also consistent with vdP measurements (R A/R C variation with V GS).

The hysteresis in few layer MoS2 can be used to develop a non-volatile memory where its temperature dependence can be used to control the read window and power dissipation, and its inversion can be used to minimize power dissipation for specific digital logic requirements. Similarly, temperature dependent differential conductance arising from the hysteresis can be used to develop temperature sensors where the inversion of hysteresis enables a large working temperature range (100 K). It is important to note that the reversibility of hysteresis with temperature is a must for temperature sensing applications, hitherto undemonstrated in few layer MoS2 devices.

Methods

Gated MoS2 devices were fabricated in vdP configuration (shown in Fig. 1a, c) to eliminate the effects of contact resistance on hysteresis. Device fabrication started with 280 nm thermally grown SiO2 on a degenerately doped p-type Si substrate. Reactive ion etching of the SiO2 surface was carried out to improve MoS2 adhesion on the SiO2 surface. MoS2 was mechanically exfoliated from a molybdenite crystal (from SPI supplies) using scotch tape method similar to graphene. The flakes were then identified using an optical microscope, and their thickness was measured by AFM. Multilayer flakes with ~5–10 nm thickness were selected for ease of device fabrication as well as better electrical conduction as compared with monolayer flakes. Nearly square large area flakes were chosen to make four contacts at the corners. After flake identification, alignment markers were made by standard electron beam lithography (Raith 150-Two) followed by electron beam source/drain patterning using PMMA. Finally, 60 nm of Au was deposited using an electron beam evaporator under high vacuum conditions followed by lift-off. Electrical transport studies were conducted at room temperature using a probe station connected to an Agilent BX-1500 parameter analyzer. Temperature dependent electrical transport measurements were conducted using a Lakeshore low-temperature measurement system (CRX-4K) and Linkam probe station under vacuum and nitrogen ambient conditions.43 The sample was heated by heating the chuck (on which it was placed) and not the entire chamber. Further, the nitrogen gas was flowing continuously between inlet and outlet line of the chamber which assures that nitrogen gas is not at the same temperature as that of the sample, rather it is closer to room temperature.

Data availability

The authors declare that [the/all other] data supporting the findings of this study are available within the paper [and its Supplementary Information files]. Any additional data that supports the findings of this study are available from the corresponding author upon reasonable request.

References

Geim, A. K. Nobel lecture: random walk to graphene. Rev. Mod. Phys. 83, 851 (2011).

Novoselov, K. S. et al. Two-dimensional gas of massless Dirac fermions in graphene. Nature. 438, 197–200 (2005).

Wei, W. & Qu, X. Extraordinary physical properties of functionalized graphene. Small. 8, 2138–2151 (2012).

Ganatra, R. & Zhang, Q. Few-layer MoS2: a promising layered semiconductor. ACS Nano. 8, 4074–4099 (2014).

Geim, A. K. & Novoselov, K. S. The rise of graphene. Nat. Mater. 6, 183–191 (2007).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacomett, iV. & Kis, A. Single-Layer MoS2 Transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Yoon, Y., Ganapathi, K. & Salahuddin, S. How good can monolayer MoS2 transistors be? Nano. Lett. 11, 3768–3773 (2011).

Wang, O., Kalantar–Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat. Nanotechnol. 7, 699–712 (2012).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano. Lett. 12, 4674–4680 (2012).

Butler, S. Z. et al. Progress, challenges, and opportunities in two-dimensional materials beyond graphene. ACS Nano. 7, 2898–2926 (2013).

Perkins, F. K. et al. Chemical vapor sensing with monolayer MoS2. Nano. Lett. 13, 668–673 (2013).

Bertolazzi, S., Krasnozhon, D. & Kis, A. Nonvolatile memory cells based on MoS2/graphene heterostructures. ACS Nano. 7, 3246–3252 (2013).

Wang, H., Wu, Y., Cong, C., Shang, J. & Yu, T. Hysteresis of electronic transport in graphene transistors. ACS Nano. 4, 7221–7228 (2010).

Yin, Z. et al. Single-layer MoS2 phototransistors. ACS Nano. 6, 74–80 (2012).

Giannazzo, F. et al. Effect of temperature–bias annealing on the hysteresis and subthreshold behavior of multilayer MoS2 transistors. Phys. Stat. Solid. 10, 797–801 (2016).

Cho, K. et al. Electric stress-induced threshold voltage instability of multilayer MoS2 field effect transistors. ACS Nano. 7, 7751–7758 (2013).

Shah, P. et al. Analysis of temperature dependent hysteresis in MoS2 field effect transistors for high frequency applications. Solid-State Electron. 91, 87–90 (2014).

Late, D. J., Liu, B., Matte, H. S. S. R., Dravid, V. P. & Rao, C. N. R. hysteresis in single-layer MoS2 field effect transistors. ACS Nano. 6, 5635–5641 (2012).

Li, T., Du, G., Zhang, B. & Zeng, Z. Scaling behavior of hysteresis in multilayer MoS2 field effect transistors. Appl. Phys. Lett. 105, 093107 (2014).

Sangwan, V. K. et al. Low-frequency electronic noise in single-layer MoS2 transistors. Nano. Lett. 13, 4351–4355 (2013).

Jariwala, D. et al. Band-like transport in high mobility unencapsulated single-layer MoS2 transistors. Appl. Phys. Lett. 102, 173107 (2013).

Park, Y., Baac, H. W., Heo, J. & Yoo, G. Thermally activated trap charges responsible for hysteresis in multilayer MoS2 field-effect transistors. Appl. Phys. Lett. 108, 083102 (2016).

Guo, Y. et al. Charge trapping at the MoS2-SiO2 interface and its effects on the characteristics of MoS2 metal-oxide-semiconductor field effect transistors. Appl. Phys. Lett. 106, 103109 (2015).

Zhu, W. et al. Electronic transport and device prospects of monolayer molybdenum disulphide grown by chemical vapour deposition. Nat. Commun. 5, 3087 (2014).

Shu, J. et al. The intrinsic origin of hysteresis in MoS2 field effect transistors. Nanoscale. 8, 3049–3056 (2016).

Pauw, L. V. D. A method of measuring the resistivity and Hall coefficient on lamellae of arbitrary shape. Philips Tech. Rev. 20, 220–224 (1958).

Mackenzie, D. M. A. et al. Quality assessment of CVD graphene: continuity, uniformity and accuracy of mobility measurements. Nano Research 10, 3596–3605 (2017).

KC, S., Longo, R. C., Addou, R., Wallace, R. M. & Cho, K. Impact of intrinsic atomic defects on the electronic structure of MoS2 monolayers. Nanotechnology. 25, 375703 (2014).

He, G. et al. Thermally assisted nonvolatile memory in monolayer MoS2 transistors. Nano. Lett. 16, 6445–6451 (2016).

Kaushik, N. et al. Schottky barrier heights for Au and Pd contacts to MoS2. Appl. Phys. Lett. 105, 113505 (2014).

Bullis, W., of Standards, U. S. N. B., Agency, U. S. D. N., Agency, U. S. D. A. R. P. Semiconductor measurement technology combined quarterly report, October 1, 1973, to March 31, 1974; NBS special publication; The Bureau: for sale by the Supt. of Docs., U.S. Govt. Print. Off., (1974)

Chen, C.-Y. & Kanicki, J. Gated-four-probe a-Si:H TFT structure: a new technique to measure the intrinsic performance of a-Si:H TFT. IEEE Electron. Device Lett. 18, 340–342 (1997).

Mehari, S., Calahorra, Y., Gavrilov, A., Eizenberg, M. & Ritter, D. Role of Transport During Transient Phenomena in AlGaN/GaN Heterostructure FETs. IEEE Electron. Device Lett. 36, 1124–1127 (2015).

Kim, W. et al. Hysteresis caused by water molecules in carbon nanotube field-effect transistors. Nano. Lett. 3, 193–198 (2003).

Bradley, K., Cumings, J., Star, A., Gabriel, J.-C. P. & Grner, G. Influence of mobile ions on nanotube based FET devices. Nano. Lett. 3, 639–641 (2003).

Plummer, J. Silicon VLSI Technology: Fundamentals, Practice and Modeling (Pearson Education, 2009).

McDonnell, S., Addou, R., Buie, C., Wallace, R. M. & Hinkle, C. L. Defect-dominated doping and contact resistance in MoS2. ACS Nano. 8, 2880–2888 (2014).

Lin, H.-C. et al. Origin of hysteresis in current-voltage characteristics of polycrystalline silicon thin-film transistors. J. Appl. Phys. 105, 054502 (2009).

Carrion, E. A. et al. Hysteresis-free nanosecond pulsed electrical characterization of top-gated graphene transistors. IEEE Trans. Electron. Device 61, 1583–1589 (2014).

Forbes, L. & Geusic, J. Memory using insulator traps. US Patent 6,140,181 (2000). http://www.google.me/patents/US6140181

Xie, X. et al. Low-frequency noise in bilayer MoS2 transistor. ACS Nano. 8, 5633–5640 (2014).

Illarionov, Y. Y. et al. The role of charge trapping in MoS2/SiO2 and MoS2/hBN field-effect transistors. 2D Mater. 3, 035004 (2016).

Mackenzie, D. M. A. et al. Fabrication of CVD graphene-based devices via laser ablation for wafer-scale characterization. 2D Mater. 2, 045003 (2015).

Acknowledgements

This work was carried out at the IIT Bombay Nanofabrication Facility and DTU Nanotech. We acknowledge support from “EC Graphene FET Flagship, grant agreement number 604391” and “H2020 European projects number 692527 and 688225”. This work was also supported by the “Danish Agency for Science Technology and Innovation”. We are thankful for fruitful discussions and technical help from Himani Jawa and Mandar M. Deshmukh.

Author information

Authors and Affiliations

Contributions

N.K., D.H.P. and S.L. designed and discussed the project. N.K., K.T. and N.G. carried out the fabrication. N.K. and D.M. performed the variable temperature measurements. P.B. and D.H.P. provided assistance with vdP measurements. B.M. carried out the suspended transistor fabrication. N.K. and K.T. performed the TCAD simulations. All authors discussed the results and N.K. wrote the paper.

Corresponding author

Ethics declarations

Competing interests

The authors declare that they have no competing financial interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kaushik, N., Mackenzie, D.M.A., Thakar, K. et al. Reversible hysteresis inversion in MoS2 field effect transistors. npj 2D Mater Appl 1, 34 (2017). https://doi.org/10.1038/s41699-017-0038-y

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-017-0038-y

This article is cited by

-

Multilayer WS2 for low-power visible and near-infrared phototransistors

Discover Nano (2024)

-

Ionotronic WS2 memtransistors for 6-bit storage and neuromorphic adaptation at high temperature

npj 2D Materials and Applications (2023)

-

Multi-state data storage in a two-dimensional stripy antiferromagnet implemented by magnetoelectric effect

Nature Communications (2023)

-

Ferroelectric transistors based on shear-transformation-mediated rhombohedral-stacked molybdenum disulfide

Nature Electronics (2023)

-

Analog–digital hybrid computing with SnS2 memtransistor for low-powered sensor fusion

Nature Communications (2022)