Abstract

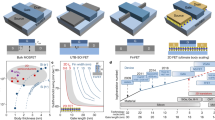

The use of organic, oxide and low-dimensional materials in field-effect transistors has now been studied for decades. However, properly reporting and comparing device performance remains challenging due to the interdependency of multiple device parameters. The interdisciplinarity of this research community has also led to a lack of consistent reporting and benchmarking guidelines. Here we propose guidelines for reporting and benchmarking key field-effect transistor parameters and performance metrics. We provide an example of this reporting and benchmarking process using a two-dimensional semiconductor field-effect transistor. Our guidelines should help promote an improved approach for assessing device performance in emerging field-effect transistors, helping the field to progress in a more consistent and meaningful way.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data used in this paper are available from the corresponding authors upon reasonable request.

Change history

24 August 2022

A Correction to this paper has been published: https://doi.org/10.1038/s41928-022-00839-2

References

Chen, Z. et al. An integrated logic circuit assembled on a single carbon nanotube. Science 311, 1735 (2006).

Franklin, A. D. et al. Sub-10-nm carbon nanotube transistor. Nano Lett. 12, 758–762 (2012).

Geim, A. K. Graphene: status and prospects. Science 324, 1530–1534 (2009).

Ye, P. D. et al. Phosphorene an unexplored 2D semiconductor with a high hole mobility. ACS Nano 8, 4033–4041 (2014).

Tao, L. et al. Silicene field-effect transistors operating at room temperature. Nat. Nanotechnol. 10, 227–231 (2015).

Wang, Y. et al. Field-effect transistors made from solution-grown two-dimensional tellurene. Nat. Electron. 1, 228–236 (2018).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Das, S., Chen, H. Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 13, 100–105 (2013).

English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS2 transistors by ultra-high vacuum metal deposition. Nano Lett. 16, 3824–3830 (2016).

Sirringhaus, H. 25th anniversary article: organic field-effect transistors: the path beyond amorphous silicon. Adv. Mater. 26, 1319–1335 (2014).

Waldrip, M., Jurchescu, O. D., Gundlach, D. J. & Bittle, E. G. Contact resistance in organic field-effect transistors: conquering the barrier. Adv. Funct. Mater. 30, 1904576 (2020).

Li, S. et al. Nanometre-thin indium tin oxide for advanced high-performance electronics. Nat. Mater. 18, 1091–1097 (2019).

Li, M. Y., Su, S. K., Wong, H. S. P. & Li, L. J. How 2D semiconductors could extend Moore’s law. Nature 567, 169–170 (2019).

Datye, I. M. et al. Reduction of hysteresis in MoS2 transistors using pulsed voltage measurements. 2D Mater. 6, 011004 (2019).

Streetman, B. G. & Banerjee, S. K. Solid State Electronic Devices 6th edn (Pearson, 2006).

Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. High-field transport and velocity saturation in synthetic monolayer MoS2. Nano Lett. 18, 4516–4522 (2018).

Pinckney, N. et al. Impact of FinFET on near-threshold voltage scalability. IEEE Des. Test 34, 31–38 (2017).

Ortiz-Conde, A. et al. A review of recent MOSFET threshold voltage extraction methods. Microelectron. Reliab. 42, 583–596 (2002).

Ghibaudo, G. New method for the extraction of MOSFET parameters. Electron. Lett. 24, 543–545 (1988).

Chang, H. Y., Zhu, W. & Akinwande, D. On the mobility and contact resistance evaluation for transistors based on MoS2 or two-dimensional semiconducting atomic crystals. Appl. Phys. Lett. 104, 113504 (2014).

Pang, C. et al. Mobility extraction in 2D transition metal dichalcogenide devices—avoiding contact resistance implicated overestimation. Small 17, 2100940 (2021).

Schroder, D. K. Semiconductor Material and Device Characterization 3rd edn (Wiley, 2015).

Mleczko, M. J. et al. HfSe2 and ZrSe2: two-dimensional semiconductors with native high-k oxides. Sci. Adv. 3, e1700481 (2017).

Nasr, J. R., Schulman, D. S., Sebastian, A., Horn, M. W. & Das, S. Mobility deception in nanoscale transistors: an untold contact story. Adv. Mater. 31, 1806020 (2019).

Bittle, E. G., Basham, J. I., Jackson, T. N., Jurchescu, O. D. & Gundlach, D. J. Mobility overestimation due to gated contacts in organic field-effect transistors. Nat. Commun. 7, 10908 (2016).

Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. Intrinsic electrical transport and performance projections of synthetic monolayer MoS2 devices. 2D Mater. 4, 011009 (2017).

Franklin, A. D. Nanomaterials in transistors: from high-performance to thin-film applications. Science 349, aab2750 (2015).

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Pao, H. C. & Sah, C. T. Effects of diffusion current on characteristics of metal-oxide (insulator)-semiconductor transistors. Solid State Electron. 9, 927–937 (1966).

John, D. L., Castro, L. C. & Pulfrey, D. L. Quantum capacitance in nanoscale device modeling. J. Appl. Phys. 96, 5180 (2004).

Xu, H., Zhang, Z. & Peng, L.-M. Measurements and microscopic model of quantum capacitance in graphene. Appl. Phys. Lett. 98, 133122 (2011).

Appenzeller, J., Zhang, F., Das, S. & Knoch, J. in 2D Materials for Nanoelectronics (eds Houssa, M. et al.) 207–240 (CRC Press, 2016).

Arutchelvan, G. et al. From the metal to the channel: a study of carrier injection through the metal/2D MoS2 interface. Nanoscale 9, 10869–10879 (2017).

Prakash, A., Ilatikhameneh, H., Wu, P. & Appenzeller, J. Understanding contact gating in Schottky barrier transistors from 2D channels. Sci. Rep. 7, 12596 (2017).

Illarionov, Y. Y. et al. Improved hysteresis and reliability of MoS2 transistors with high-quality CVD growth and Al2O3 encapsulation. IEEE Electron Device Lett. 38, 1763–1766 (2017).

IEEE International Roadmap for Devices and Systems (IEEE, 2020); https://irds.ieee.org/

Patel, K. A., Grady, R. W., Smithe, K. K. H., Pop, E. & Sordan, R. Ultra-scaled MoS2 transistors and circuits fabricated without nanolithography. 2D Mater. 7, 015018 (2020).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Ahmed, Z. et al. Introducing 2D-FETs in device scaling roadmap using DTCO. In Proc. 2020 International Electron Devices Meeting, IEDM 22.5.1–22.5.4 (IEEE, 2020); https://doi.org/10.1109/IEDM13553.2020.9371906

Chou, A. S. et al. High on-state current in chemical vapor deposited monolayer MoS2 nFETs with Sn ohmic contacts. IEEE Electron Device Lett. 42, 272–275 (2021).

Sebastian, A., Pendurthi, R., Choudhury, T. H., Redwing, J. M. & Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 12, 693 (2021).

Kumar, A., Tang, A., Philip Wong, H. S. & Saraswat, K. Improved contacts to synthetic monolayer MoS2—a statistical study. In Proc. IEEE International Interconnect Technology Conference 1–3 (IEEE, 2021); https://doi.org/10.1109/IITC51362.2021.9537515

Cheng, Z., Price, K. & Franklin, A. D. Contacting and gating 2-D nanomaterials. IEEE Trans. Electron Devices 65, 4073–4083 (2018).

Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

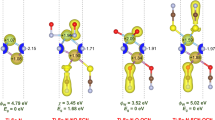

Cheng, Z. et al. Are 2D interfaces really flat? ACS Nano 16, 5316–5324 (2022).

Zhou, J. et al. A library of atomically thin metal chalcogenides. Nature 556, 355–359 (2018).

Liu, Y. et al. Van der Waals heterostructures and devices. Nat. Rev. Mater. 1, 16042 (2016).

Uchida, K., Koga, J. & Takagi, S. Experimental study on electron mobility in ultrathin-body silicon-on-insulator metal-oxide-semiconductor field-effect transistors. J. Appl. Phys. 102, 074510 (2007).

Haratipour, N., Namgung, S., Oh, S. H. & Koester, S. J. Fundamental limits on the subthreshold slope in Schottky source/drain black phosphorus field-effect transistors. ACS Nano 10, 3791–3800 (2016).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Nikonov, D. E. & Young, I. A. Benchmarking of beyond-CMOS exploratory devices for logic integrated circuits. IEEE J. Explor. Solid State Comput. Devices Circuits 1, 3–11 (2015).

Abuzaid, H., Williams, N. X. & Franklin, A. D. How good are 2D transistors? An application-specific benchmarking study. Appl. Phys. Lett. 118, 030501 (2021).

Lemme, M. C., Akinwande, D., Huyghebaert, C. & Stampfer, C. 2D materials for future heterogeneous electronics. Nat. Commun. 13, 1392 (2022).

McClellan, C. J., Yalon, E., Smithe, K. K. H., Suryavanshi, S. V. & Pop, E. High current density in monolayer MoS2 doped by AlOx. ACS Nano 15, 1587–1596 (2021).

Lembke, D. & Kis, A. Breakdown of high-performance monolayer MoS2 transistors. ACS Nano 6, 10070–10075 (2012).

Kumar, A. et al. Sub-200 Ω µm alloyed contacts to synthetic monolayer MoS2. In Proc. IEEE International Electron Devices Meeting (IEDM) 154–157 (IEEE, 2021).

Chou, A. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. In Proc. IEEE International Electron Devices Meeting (IEDM) 150–153 (IEEE, 2021).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Acknowledgements

We acknowledge H. Zhang and A. Davydov from the National Institute of Standards and Technology for their help with the TEM images of the oxide in Fig. 2. We acknowledge G. Li and L. Cao from North Carolina State University for providing the chemical-vapour-deposited MoS2 film. This work is supported by NEWLIMITS, a centre in nCORE, a Semiconductor Research Corporation (SRC) programme sponsored by NIST through award no. 70NANB17H041. A.D.F. acknowledges support from the National Science Foundation under grant no. ECCS 1915814. M.C.L. acknowledges funding from the European Union’s Horizon 2020 research and innovation programme under grant agreements nos. 881603 (Graphene Flagship), 952792 (2D-EPL) and 829035 (QUEFORMAL), as well as the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) through grants nos. LE 2440/7-1 and LE 2440/8-1. Furthermore, support by the Bundesministerium für Bildung und Forschung (BMBF, German Ministry of Education and Research) through grants nos. 03XP0210 (GIMMIK) and 03ZU1106 (NeuroSys) is acknowledged. L.-M.P. acknowledges the National Science Foundation of China under grant no. 61888102. S.J.K. acknowledges support from the NSF through award no. DMR-1921629. Fabrication and measurements were partially performed at the NIST Center for Nanoscale Science and Technology and at Duke Shared Manufacturing and Instrument Facility (SMIF). Certain commercial equipment, instruments, or materials are identified in this paper to specify the experimental procedure adequately. Such identifications are not intended to imply recommendation or endorsement by the National Institute of Standards and Technology (NIST), nor is it intended to imply that the materials or equipment identified are necessarily the best available for the purpose.

Author information

Authors and Affiliations

Contributions

All authors contributed to the preparation of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Han Wang and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Note 1: Rigorously reporting and benchmarking Imax/Imin. Supplementary Note 2: Different methods to extract threshold voltage VT and its uncertainties. Supplementary Note 3: Extracting Rc from TLM. Supplementary Note 4: Additional parameters. Supplementary Note 5: Demonstration of device spread and parameter variations. Supplementary Note 6: Benchmarking devices with different channel thicknesses.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Cheng, Z., Pang, CS., Wang, P. et al. How to report and benchmark emerging field-effect transistors. Nat Electron 5, 416–423 (2022). https://doi.org/10.1038/s41928-022-00798-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-022-00798-8

This article is cited by

-

Graphene nanoribbons grown in hBN stacks for high-performance electronics

Nature (2024)

-

Mobility overestimation in molybdenum disulfide transistors due to invasive voltage probes

Nature Electronics (2023)

-

Low-thermal-budget synthesis of monolayer molybdenum disulfide for silicon back-end-of-line integration on a 200 mm platform

Nature Nanotechnology (2023)

-

Ballistic two-dimensional InSe transistors

Nature (2023)

-

Printed transistors made of 2D material-based inks

Nature Reviews Materials (2023)