Abstract

The continued downscaling of silicon CMOS technology presents challenges for achieving the required low power consumption. While high mobility channel materials hold promise for improved device performance at low power levels, a material system which enables both high mobility n-FETs and p-FETs, that is compatible with Si technology and can be readily integrated into existing fabrication lines is required. Here, we present high performance, vertical nanowire gate-all-around FETs based on the GeSn-material system grown on Si. While the p-FET transconductance is increased to 850 µS/µm by exploiting the small band gap of GeSn as source yielding high injection velocities, the mobility in n-FETs is increased 2.5-fold compared to a Ge reference device, by using GeSn as channel material. The potential of the material system for a future beyond Si CMOS logic and quantum computing applications is demonstrated via a GeSn inverter and steep switching at cryogenic temperatures, respectively.

Similar content being viewed by others

Introduction

The past decades have witnessed an enormous increase in information processing and data transfer fueled by the extraordinary progress of micro- and nanoelectronics devices and circuits. This evolution is accelerated even more currently by the rapid development of the Internet of Things1, neuromorphic computing and quantum computing which require substantially more energy efficient electronics. However, the remarkably successful down-scaling of conventional complementary metal oxide semiconductor (CMOS) technology on silicon is reaching physical and technological limitations. Moreover, Si CMOS devices working at deep cryogenic temperatures, which are used as control and readout circuits of qubits in a quantum computing system face a big challenge of scaling of the subthreshold swing to reduce the applied voltage. All these facts have spurred research towards alternative solutions. While devices relying on a different working principle (e.g., band-to-band tunneling2,3, negative capacitance transistors4) do not yet offer satisfying properties, a larger performance boost of CMOS devices is expected to be obtained by replacing silicon with new, higher carrier mobility semiconductors in order to fulfill the ultra-low power requirements for both high-performance room temperature and cryogenic applications.

A large range of materials including III–V semiconductors5 as well as more exotic materials, such as carbon nanotubes6 and 2D materials7 have been investigated. Among them, indium-based III–V compounds, such as InAs8,9, InGaAs2,10, or InSb9,11, exhibit very high electron mobility of about 105 cm2/Vs and could thus be options for n-channel MOS field effect transistors (MOSFETs). Antimony-based materials, like GaSb and InSb can provide higher bulk hole mobility than silicon12, however, the poor high-k/III–V interface with high density of interface states (Dit) degrades the p-channel MOSFET drastically13. On the other hand, Germanium provides the highest hole mobility among bulk semiconductors14,15,16,17. However, its electron mobility is rather low. In addition, Ge suffers from a reduced maximum possible donor concentration, a high density of interface states at the high-k dielectric/Ge interface and Fermi level pinning at metal/Ge contacts18,19,20,21,22. Hence, heterointegration of III–V semiconductors with Ge has been proposed to simultaneously benefit from high-performance n-/p-channel MOSFETs12,23. This is a formidable task due to the mostly incompatible processing technologies of the two material classes. As a result, CMOS functionality has not yet been demonstrated so far in a new material system that can be integrated monolithically on silicon and provides high mobilities for both electrons and holes. From this point of view, newly developed group IV GeSn alloys are highly attractive for future nanoelectronics since they exhibit a number of unique properties24.

GeSn alloys offer a tunable energy bandgap by varying the Sn content and adjustable band off-sets in epitaxial heterostructures with Ge and SiGe. In fact, a recent report has shown that the use of Ge0.92Sn0.08 as source on top of Ge nanowires (NWs) enhances the p-MOSFET performances25. Lowering the band edge of the conduction band Γ-valley yields the advantage of low effective masses and thus high electron mobilities, as demonstrated in planar long channel GeSn n-FETs26,27,28 and FinFETs29,30. Even more, at about 8 at% Sn composition31 for a cubic lattice, or 5 at% Sn under 1% biaxial tetragonal tensile strain32, the GeSn alloy becomes a direct bandgap semiconductor, a unique property in group-IV semiconductors. This property was recently exploited leading to breakthrough results in photonics, like optically and electrically driven GeSn lasers and mid-infrared imagers integrated on Si32,33,34. Furthermore, pioneering works on spin–orbit coupling, spin transport35, and thermoelectric properties36 of GeSn underline the potential of such alloys. In addition to their unprecedented electro-optical properties, a major advantage of GeSn binaries is also that they can be grown in the same epitaxy reactors as Si and SiGe alloys, enabling an all-group IV optoelectronic semiconductor platform that can be monolithically integrated on Si. However, despite all these advantages and research interests, CMOS functionality has not been demonstrated yet in GeSn semiconductors.

This work presents top-down fabricated vertical GeSn-based gate-all-around (GAA) nanowire MOSFETs (VFETs) with NW diameters down to 25 nm. Two epitaxial heterostructures, GeSn/Ge/Si and Ge/GeSn/Ge/Si, are designed to facilitate the co-optimization of p- and n-VFETs, respectively. The GeSn- based devices are compared with all-Ge devices with identical fabrication and benchmarked against literature data. Finally, CMOS functionality is demonstrated by a GeSn-based hybrid CMOS inverter. Last but not least, the same GeSn n-VFET devices show exciting switching properties at low temperatures closing the requirements for cryogenic quantum computing. The present advances presented here are an important step to bring the GeSn semiconductor into CMOS electronics and, together with the successful research in GeSn-based photonics, may finally lead to the long-desired entirely group-IV monolithically integrated electronic-photonic circuits.

Results and discussion

GeSn/Ge CMOS concept

The CMOS concept discussed in this work, as shown in Fig. 1a, is based on the use of different heterostructures designed to yield high-performance p- and n-type VFETs (Fig. 1b) considering high mobility channels, highly doped source/drain regions, low contact resistance on top of the nanowires, and reduced gate induced drain leakage. For p-VFETs, the channel can be Ge or GeSn. First, a simple design like p+-Ge0.92Sn0.08/Ge is adopted for p-VFETs, where Ge that already provides high hole mobility is used as channel, and the source is the smaller bandgap Ge0.92Sn0.08 alloy in order to improve the carrier injection and reduce the large NW top contact resistance25. The drain region is again Ge to reduce the gate-induced drain leakage by band-to-band tunneling which increases exponentially with the bandgap reduction3. For n-VFETs, n+-Ge1-xSnx/i-Ge1-ySny/n+-Ge1-xSnx (x ≤ y) heterostructures are designed. Here, the Ge1-ySny layer is used as the high electron mobility channel, and the relative larger bandgap Ge1-xSnx layer (x < y) forms the source/drain regions to reduce the gate-induced drain leakage. For a systematic comparison Ge as source/drain regions for n-VFETs were firstly fabricated to underline the GeSn channel electron mobility improvements and to better compare with the later discussed all-GeSn-VFETs. There, the GeSn source/drain regions can have the additional advantage of allowing higher n-type doping thus much lower contact resistance in comparison with Ge source/drain.

a Schematic cross sectional view of GeSn/Ge stacks grown on Si substrates for CMOS processing. b Vertical GeSn/Ge Gate-all-around (GAA) nanowire (NW) CMOS inverter based on stacks in a. c Schematic view of an n-type vertical intrinsic Ge/Ge0.95Sn0.05/Ge NW. d In-plane strain, εxx, variation along the Ge/Ge0.95Sn0.05/Ge NW z-direction for NWs with 20 nm (red dashed line) and 65 nm (blue line) diameters. e Calculated band energies along z-axis for a 20 nm diameter Ge/Ge0.95Sn0.05/Ge NW heterostructure. f Schematic view of an n-type vertical intrinsic Ge1-xSnx/Ge1-ySny/ Ge1-xSnx (x < y) NW. g Calculated band energies along z-axis for a 20 nm diameter Ge0.95Sn0.05/Ge0.92Sn0.08 NW heterostructure. h Calculated band energies along z-axis for a 20 nm diameter Ge0.92Sn0.08/Ge0.90Sn0.10 NW heterostructure. Blue: L valley energy EL; Red: Γ-valley energy EΓ; Dark green: energy for heavy holes (HH); Light green: energy for light holes (LH).

The vertical MOSFET design enables the exploitation of electronic band engineering and in situ doping via epitaxial growth with defect-free source/channel/drain interfaces25. Such GeSn/Ge and Ge1-xSnx/Ge1-ySny/Ge1-xSnx heterostructures can be realized by selective epitaxy, a well-developed process option for Si-based materials. Here, in order to demonstrate the concept easily, the p-VFETs and n-VFETs were fabricated separately on dedicated grown wafers.

The epitaxial stacks are grown by reduced pressure chemical vapor deposition (RP-CVD) method on Ge-buffered 200 mm Si (100) wafers. Details on layers' growth and their characterization are given in Supplementary Note 1 and Figs. S1 and S2. Patterning of GeSn/Ge stacks into thin vertical NWs results in anisotropic strain relaxation, leading to changes in electronic band energies. The lattice strain of as-grown structures was extracted from X-ray diffraction while the tetragonal in-plane and out-of-plane strains in the NW are modeled using finite-element37 and atomistic modeling38. The strain values are then used to calculate the corresponding electronic bands alignment by 8-band k·p method25,39. To simplify the computation, no doping is considered in the NW structures. The calculation results are shown in Supplementary Note 2, Tables S1–S3, and Fig. S3.

While the concept of p-VFET was demonstrated in a previous paper25, here we underline the n-VFETs and the CMOS inverter proof of principle. The in-plane strain, εxx = εyy along the z-direction and band energy for Ge/Ge0.95Sn0.05/Ge vertical NWs (x = 0.0, y = 0.05) with diameters of 20 nm and 65 nm (Fig. 1c) are shown in Fig. 1d, e. While the L-valley energy EL is lower than the Γ-valley energy EΓ, the Ge0.95Sn0.05 NW channel exhibits an indirect bandgap independently of strain relaxation. Energies for heavy holes (HH) and light holes (LH) have only a slight difference at the interface. For such heterostructure, the in-plane strain at the interface is maximum at the center of the NW and decreases along the radius, reaching zero at the NW surface. The carrier transport along the NW surface is thus different from that in the center, especially for NWs with larger diameters. No other induced strain, e.g., arising from the gate stack itself, is considered in the band structure calculation.

Similar band energy calculations for intrinsic Ge1-xSnx/Ge1-ySny vertical NWs (Fig. 1f) with x = 0.05/y = 0.08 and x = 0.08/y = 0.10, and an NW diameter of 20 nm are presented in Fig. 1g, h. The Ge0.95Sn0.05 source still exhibits an indirect bandgap while the fully relaxed Ge0.92Sn0.08 channel has a direct bandgap of 0.62 eV (EΓ) (Fig. 1g). For the Ge0.92Sn0.08/Ge0.90Sn0.10 NW stack both layers are direct bandgap semiconductors, and the lower bandgap of 0.56 eV Ge0.90Sn0.10 channel provides higher electron mobility.

Vertical GeSn/Ge GAA NW CMOS process technology

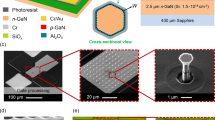

For n-VFET we start with Ge/Ge0.95Sn0.05/Ge (x = 0/y = 0.05) heterostructure as indicated in Fig. 1c. A cross-section transmission electron micrograph (TEM) of the Ge/GeSn/Ge heterostructure used for n-VFETs is shown in Fig. 2a. The Ge layer is phosphorous (P) doped while the GeSn channel layer is intrinsic. Vertical GAA NW transistors were processed using a top-down approach employing standard Si CMOS technology (see Methods). The same processing steps and gate stacks are used for the fabrication of both n- and p-type VFETs. Scanning electron microscopy (SEM) images of etched NWs with a height of about 210 nm and diameters of 25 nm and 65 nm are shown in Fig. 2b, c. A cross-section transmission electron micrograph of a final 80 nm diameter Ge/GeSn/Ge GAA vertical NW n-FET with a wrapped-around TiN/HfO2 gate stack is shown in Fig. 2d. An energy dispersive X-ray spectroscopy (EDX) mapping for Ni, Ti and Sn elements is shown in the inset. The top Al/Ti contact is isolated from the TiN gate by a planarization spin-on-glass (SOG) layer. The gate oxide consists of a ~1 nm Al2O3 interfacial layer and with 5 nm HfO2 (inset). The smoothness of the interfaces with inter-diffusion is seen in the high-resolution (HR) transmission electron micrograph shown in the lower inset in Fig. 2e. An energy-dispersive X-ray spectroscopy mapping of elements and a high-resolution transmission electron micrograph image of the top NiGeSn metal contact are provided in Fig. 2e for a p-VFET. More process details can be found in Supplementary Note 3 and Fig. S4.

a Cross-sectional transmission electron microscopy (TEM) micrograph of the Ge/GeSn/Ge heterostructure used for fabrication of vertical n-FETs (n-VFETs), overlapped with secondary ion mass spectrometry (SIMS) depth profiles of Sn, Ge and P. b 3-D scanning electron microscopy (SEM) image of a top-down n-type nanowire (NW). In the upper inset, the spin-on-glass (SOG) is etched to evidence the gate stack -Ge source region. The lower inset shows the top of the NW after the second SOG planarization prior to NiGe contact formation. c Overlapped SEM images of GeSn/Ge NWs used for p-VFETs. d Cross-sectional TEM image of a vertical Ge0.95Sn0.05/Ge GAA NW n-VFET. Insets of d Energy-dispersive X-ray spectroscopy (EDX) elemental mapping of Ni, Ti, and Sn metals (upper left), High-resolution-TEM (HR-TEM) image showing the sharp interface between GeSn and the GeSnOx/Al2O3/5 nm HfO2 gate stack (bottom left) and the GeSn/Al2O3 interface (bottom right). e EDX elemental mapping of a p-VFET with HR-TEM images for the top NiGeSn/GeSn source contact (left top) and for the GeOx/Al2O3/5 nm HfO2 gate oxides on Ge channel.

Electrical characterization of GeSn/Ge GAA NW p-VFET

A fabricated GeSn/Ge p-VFET is shown schematically in Fig. 3a, where the top GeSn layer is used as source. Different from the previous results25 where 9 nm thick Al2O3 was used as the gate dielectric here we employed a 5 nm HfO2 and 1 nm Al2O3 as the gate oxide to reduce the equivalent oxide thickness (EOT). The ID–VGS transfer and ID–VDS output characteristics of a single vertical Ge0.92Sn0.08/Ge GAA nanowire p-VFET with a diameter of 25 nm are shown in Fig. 3b, c. The drain current, ID, is normalized to the NW perimeter. The low subthreshold swing (SS) of 67 mV/decade, the high on-current/off-current (ION/IOFF) ratio and the good saturation reflect the excellent electrostatic control of the gate. The comparison with a p-VFET with a diameter of 65 nm (Fig. 3a) shows the impact of the NW diameter down-scaling: it improves SS but it reduces the on-current, due to a high contact resistance on top of the NW. A peak Gm of >850 µS/µm, much higher than for state-of-the-art GeSn based devices40,41, is achieved for 65 nm diameter NW p-VFETs (Fig. 3d). The Gm decreases with the decreasing NW diameter, as shown in Fig. 3e, is attributed to contact resistance increase for narrower NW devices. Solutions to further reduce the contact resistance are using selective growth on top of the nanowire, to increase the contact area for small NWs, and to increase the doping of the GeSn layer. The SS improvement by down-scaling the NW diameter (Fig. 3e) confirms the improved gate controllability for smaller-diameter NWs. Compared to devices from the literature, with Al2O3 as gate oxide25, the use of a thin and higher-k HfO2 dielectric reduces EOT, and consequently, offers higher on-currents, larger ION/IOFF ratios and transconductance. A detailed comparison with larger EOT and Ge homojunction NW devices is presented in Supplementary Note 4 and Fig. S5 to further demonstrate the device performance improvements by using GeSn as source and EOT scaling. A SS benchmark for various NW diameters Ge(Sn) NW pFETs is presented in Fig. 3f, showing much better SS than those GeSn devices with a similar NW diameter40,41,42. The present Ge0.92Sn0.08/Ge NW p-FETs are comparable with in-plane (horizontal) NW GeSn channel p-FETs with 1.5 nm and 3.5 nm diameters43. In short, the performance boost of vertical GeSn/Ge NW p-FETs is attributed to the small contact resistance of the GeSn source, 3D nanowire geometry, and excellent surface passivation.

a Schematic of a vertical p-FET (p-VFET) with Ge0.92Sn0.08 source and Ge channel. b ID–VGS transfer characteristics for a p-VFET with NW diameters of 25 nm and 65 nm. c ID-VDS output characteristics for a 25 nm NW diameter p-VFET, showing very good saturation. d Transconductance Gm of p-VFETs with NW diameters of 65 nm and 25 nm. e Subthreshold swing (SS) and peak Gm as a function of NW diameter. The SS improves and the Gm decreases for smaller NW diameters because of the increased top NW contact resistance. f Benchmarking of current GeSn p-VFETs with state-of-the-art published GeSn NW p-FETs in terms of the subthreshold swing SS.

Vertical Ge/GeSn/Ge GAA NW n-FET characteristics

The fabrication of Ge n-MOSFETs, as mentioned in the introduction, is very challenging. Here, we show that the use of GeSn channel considerably improves device performance. The vertical Ge/Ge0.95Sn0.05/Ge NW GAA n-type VFET structure is shown in Fig. 4a. The fabrication methodology uses the same processes as for the GeSn/Ge p-VFETs (see Supplementary Note 3 and Fig. S4 for details).

a Schematic of an n-VFET with a Ge0.95Sn0.05 channel and Ge source and drain. b ID–VGS transfer characteristics for a Ge/Ge0.95Sn0.05/Ge n-VFET in comparison with a Ge homojunction n-VFET, both with an NW diameter of 25 nm. c 2.5 times higher transconductance, Gm, for GeSn channel n-VFET compared to the Ge n-VFET. d Subthreshold swing (SS) measured at VDS = 0.5 V and peak Gm values as a function of NW diameter, showing improved SS and degraded Gm with decreasing NW diameter. The error bars represent the standard deviations of the measured data from 15 transistors. e Plots of the Y-function for the mobility calculation. f SS benchmarking of current n-VFETs with state-of-the-art GeSn n-FETs, mostly taken at VDS = 0.5 V with the exception of the data in ref. 27 which was given at VDS = 0.1 V.

The figures of merit of a vertical Ge0.95Sn0.05 channel GAA NW n-VFET, in comparison with a vertical all-Ge homojunction GAA NW n-VFET, are presented in Fig. 4. Both devices have a NW diameter of 25 nm and a gate length of 100 nm. The homojunction Ge device has a SS of 136 mV/dec and an ION/IOFF ratio of ~1 × 104 at VDS = 0.5 V, which are comparable to those in state-of-the-art horizontal Ge NW n-FETs22,44. Using Ge0.95Sn0.05 channel improves the SS, which drops down to 92 mV/dec, and results in higher ION/IOFF ratio (~1.3 × 104) and larger on-currents (Fig. 4b). The strong enhancement is clearly reflected also in the transconductance characteristics (Fig. 4c) with Gmax ~ 290 µS/µm peak for GeSn which is 2.5 times larger than the 112 µS/µm obtained for the Ge device. The SS decreases by reducing the NW diameter due to the improved gate control for small NWs (Fig. 4d), while the Gm peak value increases with increasing NW diameter, reaching a high value of 640 µS/µm for 65 nm diameter n-VFET (Fig. 4d), similar to the total resistance as displayed in the Supplementary Information Fig. S6. The higher on-current and transconductance are most likely due to the larger electron mobility in the GeSn channel. An estimation of the mobility ratio between GeSn and Ge channels is given by the Y-function45:

Where W and L are the gate width (here, the NW perimeter) and channel length, respectively, Cox the gate oxide capacitance and \({\mu }_{0}\) the intrinsic mobility. For details about the Y-function see Supplementary Note 5. Therefore, plotting Y as a function of VGS yields a line (Fig. 4d) with a slope A of:

The mobility ratio is obtained from the slope of the line, AGeSn for the GeSn device and AGe for the Ge transistor (Fig. 4e), under the reasonable assumption that the device dimensions W, L, and gate oxide thickness are the same for both devices, in line with the fabrication procedure.

It is certainly impressive that a GeSn alloy with just 5 at% Sn improves the electron mobility by 260% compared to the Ge NW device. However, this is in line with the large transconductance improvement. In addition to the higher electron mobility arising from increased electron population of the lower effective mass Γ-valley, the use of GeSn as channel offers a lower density of interface states with HfO2 dielectrics compared to Ge channel26,28. Benchmarking the SS as a function of the ION/IOFF ratio with state-of-the-art GeSn n-FETs26,27,28,29,30,46 (Fig. 4f) indicates that the current GeSn n-VFETs are comparable to 17 nm diameter horizontal Ge0.98Sn0.02 NW n-FETs from ref. 47 with source/drain doping an order of magnitude higher than here.

GeSn CMOS inverter

A CMOS inverter is a basic circuitry of logic integrated circuits (ICs) demonstrating the integration potential of the developed n- and p-VFETs. The GeSn CMOS inverter concept shown in Fig. 1b is experimentally demonstrated using p- and n- VFETs presented above, by externally connecting a GeSn/Ge GAA NW p-VFET and a Ge/GeSn/Ge n-VFET via Al wires, as schematically indicated in the inset of Fig. 5a-3. The ID–VGS and ID–VDS characteristics for both n- and p-VFETs are presented in Fig. 5a-1 and a-2. They are symmetric around −0.3 V in terms of ION, SS, and drain-induced barrier lowering. The performance symmetry can be adjusted to 0 V by a proper choice of gate metals with appropriate work functions, as typically done in Si CMOS inverters47,48. The voltage transfer characteristics of the inverter for supply voltage, VDD, varying from 0.2 V to 1 V, show a very decent transition at around −0.3 V + VDD/2. The shift of −0.3 V is due to the un-matched threshold voltage VTH (cf. Fig. 5b). The apparent degradation in the high VIN regime is caused by the poor saturation of the n-VFET (see ID–VDS characteristics in Fig. 5a) and high off-currents for the pull-up p-VFET. The voltage gain shows a maximum value of ~18 at VDD = 0.8 V (Fig. 5c).

a Drain current ID vs gate voltage VGS (ID–VGS) (a-1) and drain current ID vs drain voltage VDS (ID–VDS) (a-2) characteristics of the GeSn/Ge p-VFET and Ge/GeSn/Ge n-VFET forming the CMOS inverter. The p-VFET characteristics are shown in red on the left side of a-1 and a-2, while the n-VFET characteristics are displayed in blue on the right side of the figures. The inset (a-3) shows the inverter circuit connections of p- and n-VFETs with the supply voltage VDD applied on the drain of the p-VFET. b Voltage transfer characteristics of a hybrid inverter by varying the supply voltage VDD from 0.2 V to 1 V. c Voltage gain versus the input voltage VIN of an inverter extracted from Fig. 5b at various supply voltage VDD from 0.2 V to 1.0 V, showing a maximum gain of 18 V/V at VDD = 0.8 V.

This demonstration of a GeSn CMOS inverter underlines the advantages of GeSn alloys for high-performance nanoelectronics. Further improvements are at hand and include the implementation a self-alignment of gate and channel via an insulating layer between the gate and the substrate, or the use of an all-GeSn heterostructure for the n-type as shown in Fig. 6 and the Supplementary Information Fig. S7 and discussed in the following.

Despite the proof-of-principle for device performance enhancement brought by the GeSn channel, the n-VFET device is still limited by the use of Ge as source and drain (S/D) regions. The high S/D series resistance and super-linear ID–VD characteristics at small VDS (Fig. 5a) originate from the low P solubility in Ge. For the case of chemical vapor deposition growth the maximum active P concentration is limited to ~2 × 1019 cm−3,49,50,, resulting in a Schottky contact and thus, a poor saturation of the ID–VDS characteristics. This disadvantage is alleviated in GeSn alloys to fabricate all-GeSn n-VFET as illustrated in Fig. 1, where a P doping concentration of about 1 × 1020 cm−3 in GeSn is readily achieved. The use of lower Sn content alloys, i.e., Ge0.95Sn0.05, as first epitaxial layer relaxes the growth constraints, allowing a thick GeSn layer with a larger Sn content to be pseudomorphically grown. The sketch of an all- Ge0.922Sn0.078 n-VFET with source/drain layers doped with phosphorous to 7 × 1019 cm−3 is shown in Fig. 6a. The transfer characteristic of the device as displayed in Fig. 6b, measured at 300 K, shows a subthreshold swing of 120 mV/dec, similar to the Ge/Ge0.95Sn0.05/Ge n-VFET discussed above. However, the use of a smaller bandgap drain layer increases the gate-induced drain leakage, due to enhanced band-to-band tunneling, leading to a lower ION/IOFF ratio. This can be solved by using a larger bandgap material, meaning lower Sn content i.e., <5% Sn, while maintaining a high Sn content (>8% Sn) in the channel to improve the electron mobility, as discussed in Fig.1 and Supplementary Information Note 6 and Fig. S7.

Interestingly, the low-temperature measurement shows an additional application direction of the all-GeSn MOSFETs: cryogenic control electronics for quantum computing. Measurements at 12 K not only reduce the off-currents due to the suppressed the trap assisted tunneling and thus, achieve an ION/IOFF ratio of 106, but offer an SS of 20 mV/dec below the threshold voltage, Vth, following the Boltzmann scaling of \(\frac{{kT}}{q}\) without saturation (Fig. 6c inset). The inverse slope Sinf, measured at the inflection region ranging from Vth to Vth + 0.1 V is only 126 mV/dec, much smaller than Sinf = 332 mV/dec reported51, in the same voltage range, for Si nanowire MOSFET with a NW cross-section of 20 × 20 nm2. This makes the GeSn device very interesting while the conventional cryogenic Si CMOS meets a big challenge called “inflection phenomenon”52. In Si CMOS the often-observed saturation of SS in the \(\log {I}_{D} \sim {V}_{{GS}}\) linear region at temperatures <50 K and the large Sinf necessitate higher applied drive voltages prohibiting the low power levels needed for cryogenic control electronics (see Supplementary Note 7 and Figs. S8 and S9), the lower Sinf and no saturation of SS with the temperature in the all- GeSn n-VFET at cryogenic temperature show high potential for quantum computing applications.

Conclusions

Vertical gate-all-around GeSn/Ge p-FETs and Ge/GeSn/Ge n-FETs with nanowire diameters down to 25 nm were fabricated and characterized. The small bandgap GeSn alloy used on top of the nanowire considerably boosts the Ge channel p-VFETs performances, offering subthreshold swings as low as 67 mV/dec and very high transconductances of up to 850 µS/µm. For n-VFETs the Ge0.95Sn0.05 alloy used as a channel material led to an improved SS, a much higher Ion/Ioff ratio, a 2.5 times higher transconductance, and 2.6 times higher electron mobility compared to Ge NW n-VFETs. The symmetry and the high performances of n- and p-VFETs enabled the realization of a GeSn CMOS inverter which showed very good voltage transfer characteristics and high voltage gains. With excellent device performances, high carrier mobilities, band engineering possibilities, steep switching at cryogenic temperatures and Si CMOS compatibility, the GeSn-based CMOS platform provides a path to extend Moore’s law beyond the silicon-based era.

Methods

Ge and GeSn layers were grown by RP-CVD in an industrial cluster tool. Germane, GeH4, was used as precursor gas for pure Ge-epitaxy, and digermane, Ge2H6, together with tin-tetrachloride, SnCl4, as precursors for GeSn epitaxy. More details about the layer growth can be found elsewhere31. The grown layers were examined by Rutherford backscattering spectrometry and X-ray diffraction, in order to obtain information on the Sn-content and the lattice strain, respectively. The high crystalline quality was furthermore confirmed using TEM. Additionally, electrochemical capacitance–voltage measurements were used to obtain the doping concentrations. Further information on material characterization can be found in Supplementary Note 1.

The fabrication of vertical GeSn and Ge nanowire VFETs was performed using standard CMOS processes. After e-beam lithography with Hydrogen Sylsesquioxane as photoresist, reactive ion etching using Cl2/Ar (4/24 sccm) plasma was performed to form vertical NWs. Digital etching consisting of multiple cycles of self-limiting O2 plasma oxidation at room temperature and diluted HCl stripping was used to shrink the GeSn/Ge and Ge/GeSn/Ge NW diameters and smoothen the NW surfaces. More details can be found elsewhere25. Atomic layer deposition was used to wrap HfO2/Al2O3/Ge(Sn)Ox dielectrics around the NWs. The final EOT after post-oxidation process was ~2.4 nm. 40 nm thick TiN deposited by sputtering with argon formed the gate metal. Then, planarization was performed by spin-coated SOG with curing at 350 °C followed by isotropic back-etching in a reactive ion etching chamber with CHF3. The exposed top gate stack was removed by an optimized Cl2/SF6 etching recipe. Subsequently, a second SOG spin-coating and planarization were performed to isolate the gate stack and top contact. Ni was deposited for top contact formation followed by a forming gas annealing step at 300 °C to form NiGe(Sn) and thereby reduce the top contact resistance. Finally, the device fabrication ended with Ti/Al metallization using lift-off technology after contact window opening and post-metallization annealing.

For characterization, the device current–voltage (I–V) characteristics were measured using a Keithley 4200 Semiconductor Characterization System. For low-temperature measurements, a cryogenic probe station from FormFactor was used, together with an Agilent E5270B for current-voltage characteristics measurements. Liquid He was used for cooling.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request. Source data underlying the graphs and charts presented in the main figures are included in “Supplementary Data 1”.

References

The Internet of Things ((MIT Technology Review, 2014). https://go.nature.com/2J2IOYz.

Convertino, C. et al. A hybrid III–V tunnel FET and MOSFET technology platform integrated on silicon. Nat. Electron. 4, 162–170 (2021).

Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011).

Cao, W. & Banerjee, K. Is negative capacitance FET a steep-slope logic switch? Nat. Commun. 11, 196 (2020).

del Alamo, J. A. Nanometre-scale electronics with III–V compound semiconductors. Nature 479, 317–323 (2011).

Han, S. J. et al. High-speed logic integrated circuits with solution-processed self-assembled carbon nanotubes. Nat. Nanotechnol. 12, 861–865 (2017).

Chen, C. et al. Sub-10-nm graphene nanoribbons with atomically smooth edges from squashed carbon nanotubes. Nat. Electron. 4, 653–663 (2021).

Berg, M. et al. InAs nanowire MOSFETs in three-transistor configurations: Single balanced RF down-conversion mixers. Nanotechnology 25, 485203 (2014).

Bouarissa, N. & Aourag, H. Effective masses of electrons and heavy holes in InAs, InSb, GaSb, GaAs and some of their ternary compounds. Infrared Phys. Technol. 40, 343–349 (1999).

Yokoyama, M. et al. III-V/Ge high mobility channel integration of InGaAs n-channel and Ge p-channel metal-oxide-semiconductor field-effect transistors with self-aligned Ni-based metal source/drain using direct wafer bonding. Appl. Phys. Express 5, 1–5 (2012).

Wang, Y. et al. Field effect transistor based on single crystalline InSb nanowire. J. Mater. Chem. 21, 2459–2462 (2011).

Takagi, S. et al. III-V/Ge channel MOS device technologies in nano CMOS era. Jpn. J. Appl. Phys. 54, 06FA01 (2015).

Nishi, K. et al. Operation of the GaSb p-channel metal-oxide-semiconductor field-effect transistors fabricated on (111)A surfaces. Appl. Phys. Lett. 105, 8–12 (2014).

Pillarisetty, R. Academic and industry research progress in germanium nanodevices. Nature 479, 324–328 (2011).

Saito, M., Moto, K., Nishida, T., Suemasu, T. & Toko, K. High-electron-mobility (370 cm2/Vs) polycrystalline Ge on an insulator formed by As-doped solid-phase crystallization. Sci. Rep. 9, 19–24 (2019).

Feng, X., Liu, X. & Ang, K. W. 2D photonic memristor beyond graphene: progress and prospects. Nanophotonics 9, 1579–1599 (2020).

Wen, W. C. et al. Interface trap and border trap characterization for Al2O3/GeOx/Ge gate stacks and influence of these traps on mobility of Ge p-MOSFET. AIP Adv. 10, 065119 (2020).

Kuzum, D. et al. High-mobility Ge N-MOSFETs and mobility degradation mechanisms. IEEE Trans. Electron Devices 58, 59–66 (2011).

Goley, P. S. & Hudait, M. K. Germanium based field-effect transistors: challenges and opportunities. Materials (Basel) 7, 2301–2339 (2014).

Ye, H. Y., Lan, H. S. & Liu, C. W. Electron mobility in junctionless Ge nanowire NFETs. IEEE Trans. Electron Devices 63, 4191–4195 (2016).

Wu, W. et al. RTN and low frequency noise on ultra-scaled near-ballistic Ge nanowire nMOSFETs. Dig. Tech. Pap. Symp. VLSI Technol. 2016, 2015–2016 (2016).

Wu, H., Wu, W., Si, M. & Ye, P. D. First demonstration of Ge nanowire CMOS circuits: Lowest SS of 64 mV/dec, highest gmax of 1057 μs/μm in Ge nFETs and highest maximum voltage gain of 54 V/V in Ge CMOS inverters. Tech. Dig. - Inteernational Electron Devices Meeting IEDM 2016, pp. 2.1.1–2.1.4 (2015).

Liu, B. et al. High performance Ge CMOS with novel InAlP-passivated channels for future sub-10 nm technology node applications. Tech. Dig. - Int. Electron Devices Meet. IEDM 657–659 (2013). https://doi.org/10.1109/IEDM.2013.6724700

Soref, R. A., Buca, D. & Yu, S.-Q. Group IV Photonics- driving integrated optoelectronics. Opt. Photonics News 27, 32–39 (2016).

Liu, M. et al. Epitaxial GeSn/Ge vertical nanowires for p-type field-effect transistors with enhanced performance. ACS Appl. Nano Mater. (2021). https://doi.org/10.1021/acsanm.0c02368

Han, G. et al. Strained germanium-tin (GeSn) N-channel MOSFETs featuring low temperature N+/P junction formation and GeSnO2 interfacial layer. Digest of Technical Papers - Symposium VLSI Technology. pp. 97–98 (2012). https://doi.org/10.1109/VLSIT.2012.6242479.

Liu, T. H. et al. High-mobility GeSn n-channel MOSFETs by low-temperature chemical vapor deposition and microwave annealing. IEEE Electron Device Lett 39, 468–471 (2018).

Fang, Y. C., Chen, K. Y., Hsieh, C. H., Su, C. C. & Wu, Y. H. N-MOSFETs formed on solid phase epitaxially grown GeSn film with passivation by oxygen plasma featuring high mobility. ACS Appl. Mater. Interfaces 7, 26374–26380 (2015).

Chuang, Y., Huang, H. C. & Li, J. Y. GeSn N-FinFETs and NiGeSn contact formation by phosphorus implant. 2017 Silicon Nanoelectronics Workshop (SNW). pp. 97–98 (2017).

Han, K. et al. First demonstration of complementary FinFETs and tunneling FinFETs co-integrated on a 200 mm GeSnOI substrate: a pathway towards future hybrid nano-electronics systems. Dig. Tech. Pap. - Symp. VLSI Technol. 2019, T182–T183 (2019).

Wirths, S. et al. Lasing in direct-bandgap GeSn alloy grown on Si. Nat. Photonics 9, 88–92 (2015).

Elbaz, A. et al. Ultra-low-threshold continuous-wave and pulsed lasing in tensile-strained GeSn alloys. Nat. Photonics 14, 375–382 (2020).

Simola, E. T. et al. Voltage-tunable dual-band Ge/Si photodetector operating in VIS and NIR spectral range. Opt. Express 27, 8529 (2019).

Zhou, Y. et al. Electrically injected GeSn lasers on Si operating up to 100 K. Optica 7, 924 (2020).

Tai, C. et al. Strain effects on rashba spin‐orbit coupling of 2D hole gases in GeSn/Ge heterostructures. Adv. Mater. 33, 2007862 (2021).

Spirito, D. et al. Thermoelectric efficiency of epitaxial GeSn alloys for integrated Si-based applications: assessing the lattice thermal conductivity by Raman thermometry. ACS Appl. Energy Mater 4, 7385–7392 (2021).

Ertekin, E., Greaney, P. A., Chrzan, D. C. & Sands, T. D. Equilibrium limits of coherency in strained nanowire heterostructures. J. Appl. Phys. 97, 114325 (2005).

Swadener, J. G. & Picraux, S. T. Strain distributions and electronic property modifications in Si/Ge axial nanowire heterostructures. J. Appl. Phys. 105, 044310 (2009).

Rainko, D. et al. Investigation of carrier confinement in direct bandgap GeSn/SiGeSn 2D and 0D heterostructures. Sci. Rep. 8, 1–13 (2018).

Huang, Y. et al. First stacked Ge 0. 88 Sn 0. 12 pGAAFETs with cap, L G = 40 nm, compressive strain of 3.3%, and high S/D doping by CVD epitaxy featuring record ION of 58 μA at V OV = V DS = −0. 5V, Record Gm, max of 172 μS at V DS = −0. 5V, and low noise. In Proceedings of IEDM Technical Digest. IEEE International Electron Devices Meeting. 689–692 (2019).

Huang, Y. S. et al. First vertically stacked, compressively strained, and triangular Ge0.91Sn0.09 pGAAFETs with high ION of 19.3 μA at VOV=VDS=−0.5V, Gm of 50.2 μS at VDS = −0.5 V and low SSlin of 84 mV/dec by CVD epitaxy and orientation dependent etching. Dig. Tech. Pap. - Symp. VLSI Technol. 2019-, T180–T181 (2019).

Huang, Y. S. et al. First vertically stacked GeSn nanowire pGAAFETs with Ion = 1850 μA/μm (VOV = VDS = −1 V) on Si by GeSn/Ge CVD epitaxial growth and optimum selective etching. In Proceedings of Technical Digest - International Electron Devices Meeting (IEDM) 37.5.1–37.5.4 (2017). https://doi.org/10.1109/IEDM.2017.8268512.

Kang, Y. et al. Ge0.95Sn0.05gate-all-around p-channel metal-oxide-semiconductor field-effect transistors with Sub-3 nm nanowire width. Nano Lett. 21, 5555–5563 (2021).

Chou, L. et al. Ge N-channel MOSFETs with ZrO2 dielectric achieving improved mobility. Nanoscale Res. Lett. 16, 125 (2021).

Ghibaudo, G. New method for the extraction of MOSFET parameters. Electron. Lett. 24, 543–545 (1988).

Tu, C. Te. et al. First vertically stacked tensily strained Ge0.98Si0.02 nGAAFETs with no parasitic channel and LG = 40 nm featuring record ION = 48 μa at VOV=VDS=0.5 V and record Gm,max(μS/μm)/SSSAT(mV/dec) = 8.3 at VDS = 0.5 V.In Proceedings of Technical Digest—International Electron Devices Meeting (IEDM), 681–684 (2019).

Jena, B., Dash, S. & Mishra, G. P. Improved switching speed of a CMOS inverter using work-function modulation engineering. IEEE Trans. Electron Devices 65, 2422–2429 (2018).

Chang, W. T., Li, M. H., Hsu, C. H., Lin, W. C. & Yeh, W. K. Modifying threshold voltages to n- And p- Type FinFETs by work function metal stacks. IEEE Open J. Nanotechnol 2, 72–77 (2021).

Camacho-Aguilera, R. E., Cai, Y., Bessette, J. T., Kimerling, L. C. & Michel, J. High active carrier concentration in n-type, thin film Ge using delta-doping. Opt. Mater. Express 2, 1462 (2012).

Brotzmann, S. & Bracht, H. Intrinsic and extrinsic diffusion of phosphorus, arsenic, and antimony in germanium. J. Appl. Phys. 103, 033508 (2008).

Habicht, S., Feste, S., Zhao, Q. T., Buca, D. & Mantl, S. Electrical characterization of Ω-gated uniaxial tensile strained Si nanowire-array metal-oxide-semiconductor field effect transistors with <100>- and <110> channel orientations. Thin Solid Films 520, 3332–3336 (2012).

Beckers, A., Jazaeri, F. & Enz, C. Inflection phenomenon in cryogenic MOSFET behavior. IEEE Trans. Electron Devices 67, 1357–1360 (2020).

Acknowledgements

The authors thank the German Federal Ministry of Education (BMBF) for partially supporting the activity via ForMikro - SiGeSn nanoFET project.

Funding

Open Access funding enabled and organized by Projekt DEAL.

Author information

Authors and Affiliations

Contributions

Q.Z. and D.B. planned the device and the experiments. M.F., J.M.H., and D.B. worked on the epitaxy and characterization of the material. M.L. and Y.J. performed the device fabrication and characterization. D.Y. and Y.H carried out part of the device characterization. Z.I. performed the band structure calculation. J.H. B, F.B., and A.M. performed the SEM, TEM, EDX, and SIMS characterization. J.K., D.G., and Q.Z. supervised the work and coordinated device fabrication and data interpretation. D.B., J.K., and Q.Z edited the manuscript and all authors discussed and corrected the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Communications Engineering thanks Zhongyunshen Zhu and the other, anonymous, reviewers for their contribution to the peer review of this work. Primary Handling Editors: [Liwen Sang] and [Miranda Vinay and Mengying Su]. Peer reviewer reports are available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Liu, M., Junk, Y., Han, Y. et al. Vertical GeSn nanowire MOSFETs for CMOS beyond silicon. Commun Eng 2, 7 (2023). https://doi.org/10.1038/s44172-023-00059-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s44172-023-00059-2

This article is cited by

-

Editors’ Choice 2023

Communications Engineering (2023)