Abstract

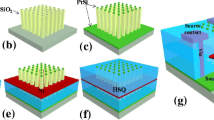

The authors present the technological routes used to build planar and vertical gate all-around (GAA) field-effect transistors (FETs) using both Si and SiGe nanowires (NWs) and the electrical performances of the as-obtained components. Planar FETs are characterized in back gate configuration and exhibit good behavior such as an ION/Ioff ratio up to 106. Hysteretic behavior and sub-threshold slope values with respect to surface and oxide interface trap densities are discussed. Vertical devices using Si NWs show good characteristics at the state of the art with ION/IOFF ratio close to 106 and sub-threshold slope around 125 mV/decade while vertical SiGe devices also obtained with the same technological processes, present an ION/IOFF ratio from 103 to 104 but with poor dynamics which can be explained by the high interface traps density.

Similar content being viewed by others

References

J. C. Johnson, H.-J. Choi, K. P. Knutsen, R. D. Schaller, P. Yang and R. J. Saykally, Nature Materials, 1 (2002), 106–110

B. Tian, X. Zheng, T. J. Kempa, Y. Fang, N. Yu, G. Yu, J. Huang and C. M. Lieber, Nature Letters, 449 (2007), 885–890

B. Hua, J. Motohisa, Y. Kobayashi, S. Hara, and T. Fukui, Nano Letters, 9 (2009), 112–116

H. Ko, Z. Zhang, Y.-L. Chueh, J. C. Ho, J. Lee, R. S. Fearing, and A. Javey, Adv. Funct. Mater. 2009, 19, 3098–3102

Y. Cui, X. Duan, J. Hu, and C. M. Lieber J. Phys. Chem. B, 104 (2000), 5213–5216

N. singh, K. D. Buddharaju, S. K. Manhas, A. Agarwal, S. C. Rustagi, G. Q. Lo, N. Balasubramanian and D.-L. Kwong, IEEE Trans. Elec. Dev. 55 (2008) pp. 3107

R. S. Wagner, W. C. Ellis, Appl. Phys. Lett. 4 (1964), 89

A. Potié, T. Baron, L. Latu-Romain, G. Rosaz, B. Salem, L. Montés, P. Gentile, J. Kreisel and H. Roussel, J. Appl. Phys., 110 (2011), 024311–024311

G. Yu, and C. M. Lieber, Pure Appl. Chem., 82 (2010), 2295–2314

V. Schmidt, H. Riel, S. Senz, S. Karg, W. Riess, and U. Gösele, Small, 2 (2006), 85–88

B. Yang, K. D. Buddharaju, S. H. G. Teo, N. Singh, G. Q. Lo, and D. L. Kwong, IEEE Electron Device Letters, 29 (2008), 791

Tomas Bryllert, Lars-Erik Wernersson, Linus E. Fröberg, and Lars Samuelson, IEEE Electron Device Letters, 27 (2006), 323

T. Tanaka, K. Tomioka, S. Hara, J. Motohisa, E. Sano and T. Fukui, Appl. Phys. Exp. 3 (2010) pp.025003

G Rosaz, B Salem, N Pauc, P Gentile, A Potié, A Solanki and T Baron, Semicond. Sci. Technol. 26 (2011) 085020

G. Rosaz, B. Salem, N. Pauc, P. Gentile, A. Potié, T. Baron, Microelectronic Engineering 88 (2011)3312–3315

G. Rosaz, B. Salem, N. Pauc, P. Gentile, A. Potié, T. Baron, Appl. Phys. Lett. 99 (2011), 193107

D. Kang, J.-H. Ko, E. Bae, J. Hyun, W. Park, B.-K. Kim, J.-J. Kim and C. Lee, J. Appl. Phys. 96 (2004), 7574

S. M. Sze, Physics of semiconductor devices, 3rd Ed., Wiley, New York, 2006

W. Lu and C. M Lieber, J. Phys. D: Appl. Phys. 39 (2006) R387–R406

M. T. Björk, O. Hayden, H. Schmid, H. Riel, and W. Riess, Appl. Phys. Lett. 90, (2007) 142110

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Rosaz, G., Salem, B., Pauc, N. et al. From planar to vertical nanowires field-effect transistors. MRS Online Proceedings Library 1439, 101–107 (2012). https://doi.org/10.1557/opl.2012.1422

Published:

Issue Date:

DOI: https://doi.org/10.1557/opl.2012.1422