Abstract

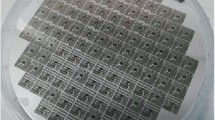

Multiple 50 mm hybrid Si-on-SiC substrates consisting of thin film [100] Si (1 µm) on bulk semi-insulating [0001] 6H-SiC wafers were fabricated using low-temperature (150 °C) wafer bonding and slicing techniques. A set of samples were prepared comparing various thicknesses of SiO2 (60, 120, 190, 240 and 520 nm) as an intermediate bonding layer between the two materials. A variety of test structures such as Van der Pauw structures, linear transfer-length measurement arrays and resistors were fabricated in the Si layers using standard Si processing (such as lithography, B-diffusion, etching and oxidation) in order to characterize the robustness as well as the electrical and thermal properties of the hybrid substrates. Bulk Si and Si-on-insulator (SOI) substrates were used for comparison. We report the Si layers on the hybrid Si-on-SiC substrates to be device-grade in terms of mobility and crystal structure, and that their device-to-device electrical isolation properties are superior to those of bulk Si and comparable to those of SOI. Furthermore, electrical test structures on hybrid Si-on-SiC substrates exhibit vastly superior heat dissipation compared to equivalent devices on bulk Si or SOI. Specifically, the temperature rise can be as much as 102 °C lower in resistor devices made on Si-on-SiC (Tj= 191 °C) compared to on bulk Si (Tj= 293 °C) under high-power density operation (67 kW/cm2). We also describe the effects of intermediate oxide thickness on thermal resistance.

Similar content being viewed by others

References

W.J Choyke and R.P Devaty, Naval Research Reviews, 51, 2–12 (1999)

http://www.cree.com/products/index.htm

http://www.infineon.com/cgi-bin/ifx/portal/ep/home.do?tabId=0

R. Michnowski and W. Wojtasiak, IEEE Proceedings of the 14th International Conference on Microwaves, Radar and Wireless Communications, 1, 89–92 (2002)

S. Pinel, J. Tasselli, J.P. Bailbe, A Marty, P. Puech, and D. Esteve, IEEE Proceedings of the 22nd International Conference on Microelectronics, 2, 443 – 446 (2000)

I.C Kizilyalli, H. Safar, J. Herbsommer, S.J. Burden, P.L. Gammel, IEEE Electron Device Letters, 26, 404–406 (2005).

C.A. Desmond-Colinge and U. Gösele, MRS Bulletin, 23, 30–34 (1998).

http://www.intrinsicsemi.com/

http://www.novasic.com/

M. Bruel, Electon. Lett., 31, 1201 (1995). SmartCut is a registered trademark of SOITEC, Parc Technologique des Fontaines, 38190 Bernin, France.

11. R.C. Jaeger, Introduction to Microelectronic Fabrication, (Addison-Wesley, Reading Mass. 1988) p49–87.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Whipple, S.G., Torvik, J.T., Treece, R.E. et al. Demonstration of Hybrid Silicon-on-Silicon Carbide Wafers and Electrical Test Structures with Improved Thermal Performance. MRS Online Proceedings Library 911, 1013 (2005). https://doi.org/10.1557/PROC-0911-B10-13

Received:

Accepted:

Published:

DOI: https://doi.org/10.1557/PROC-0911-B10-13