A Novel Framework for Testing High-Speed Serial Interfaces in Multiprocessor Based Real-Time Embedded System

Abstract

:1. Introduction

2. High-Speed Interface Overview and Related Works

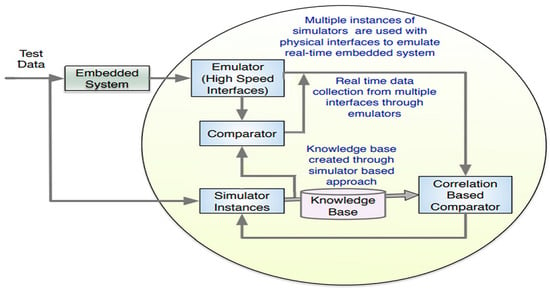

3. The Proposed Framework for Testing

3.1. Simulator Architecture

3.1.1. Multiple Simulator Instances

3.1.2. Sync Bug Generator

- Data received at Rx with delay: delay occurs in receiving data at Rx. Delay can occur at various points during communication, such as at the beginning, in the middle (anywhere between communication), or both.

- Data transmission from Tx with delay: delay occurs in transmitting data from Tx.

- No data received at Rx: Tx sends the data constantly but Rx does not receive it.

- No data transmitted from Tx: Tx does not send the data to Rx.

- Data overriding during communication: Rx overrides some packets of data during communication.

- Out of synchronization: data are not received in a sequence (out of order).

3.1.3. Scenario Based Approach for Test Cases Generator

3.2. High Speed Serial Interface Testing

4. Simulation Results

Test Validity

5. Case Study Settings

Systems under Test

6. Discussion

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Acknowledgments

Conflicts of Interest

Appendix A

Appendix A.1.

Appendix A.2.

| Test Case ID | Test Scenario | Test Case | Pre-Condition(s) | Test Steps | Test Data | Expected Test Result | Post-Condition(s) | Actual Test Result | Status (Pass/Fail) |

|---|---|---|---|---|---|---|---|---|---|

| TC_RX-002-1 | Verify receiving data | Tx send the data and Rx receives the data | 1. Tx should be in place. 2. Rx should be in place. 3. There must be a test vector available. | 1. It begins when Tx sends the data. 2. If data received at the Rx end without any disruption then plot the Ram Else Wait for definite amount of time (Counter updated after timeout) End if | Normal Communication on both Tx and Rx end <Tx transmit the data> <Rx receives the data> | Successful Communication | Rx receive the data | Successful Communication | Pass |

| TC_RX-002-2 | Verify Receiving data | Tx send the data but Rx does not receive them due to some reasons | 1. Tx should be in place. 2. Rx should be in place. 3. There must be a test vector available. | 1. It begins when Tx sends the data. 2. If data received at the Rx end without any disruption then plot the Ram Else Wait for definite amount of time (counter updated after timeout) End if | <Tx transmit the data> <Rx does not receive the data> | Unsuccessful Communication | No data receive at Rx | - | |

| TC_RX-002-3-1 | Verify receiving data | Tx send the data to the Rx, but with (In) delay | 1. Tx should be in place. 2. Rx should be in place. 3. There must be a test vector available. | 1. It begins when Tx sends the data. 2. If data received at the Rx end without any disruption then plot the Ram Else if Data received at the beginning but after some times, the delay comes in communication (when delay comes, wait for a definite amount of time) then plot the Ram Else Wait for definite amount of time (counter updated after timeout) End if | <Tx transmit the data> <Rx receives the data but with delay anywhere in the middle.> | Communication take place (time constraint) | Data receive at Rx but with In delay | - | |

| TC_RX-002-3-2 | Verify receiving data | Tx send the data to the Rx, but with (start and In) delay | 1. Tx should be in place. 2. Rx should be in place. 3. There must be a test vector available. | 1. It begins when Tx sends the data. 2. If data receive at the Rx end without any disruption then plot the Ram Else if Data received after some delay (wait for definite amount of time) then plot the Ram Else Wait for definite amount of time (counter updated after timeout) End if | <Tx transmit the data> <Rx receives the data but with delay both at the beginning and anywhere in the middle> | Communication take place (time constraint) | Data receive at Rx but with (start and In) delay | - | |

| TC_RX-002-4 | Verify receiving data | Tx send the data and Rx receives the data | 1. Tx should be in place. 2. Rx should be in place. 3. There must be a test vector available. | 1. It begins when Tx sends the data. 2. If data are received at the Rx end, plot the Ram. Else Wait for definite amount of time (counter updated after timeout) End if | Normal communication on both Tx and Rx end <Tx transmit the data> <Rx overrides some packet of data > | Communication take place (overriding) | Rx receive the data but with data over riding at Rx | - | |

| TC_RX-002-5 | Verify receiving data | Tx send the data and Rx receives the data | 1. Tx should be in place. 2. Rx should be in place. 3. There must be a test vector available. | 1. It begins when Tx sends the data. 2. If data receive at the Rx end without any disruption then plot the Ram Else Wait for definite amount of time (Counter updated after timeout) End if | Normal communication on both Tx and Rx end <Tx transmit the data> <Rx receives the data> | Communication take place (out of sequence) | Rx receives out of sequence data | - |

| Test Case ID | Test Scenario | Test Case | Pre-Condition(s) | Test Steps | Test Data | Expected Test Result | Post-Condition(s) | Actual Test Result | Status (Pass/Fail) |

|---|---|---|---|---|---|---|---|---|---|

| TC_TX-001-2-1 | Transmitting data from the Tx | Tx send the data with delay (In) to the Rx | 1. Tx should be in place. 2. Rx should be in place. 3. There must be a test vector available. | 1. It begins when Tx sends the data. 2. If data received at the Rx end without any disruption then plot the Ram Else if Data received at the beginning but after some times, the delay comes in communication (when delay comes, wait for a definite amount of time) then plot the Ram Else Wait for definite amount of time (counter updated after timeout) End if | <Tx transmit the data with delay (anywhere between transmission)> <Rx receives the data but with delay (anywhere between the transmission)> | Communication take place (time constraint) | Rx receive the data but with In delay | - | |

| TC_TX-001-2-2 | Transmitting data from the Tx | Tx send the data with delay (start and In) to the Rx | 1. Tx should be in place. 2. Rx should be in place. 3. There must be a test vector available. | 1. It begins when Tx sends the data. 2. If data received at the Rx end without any disruption then plot the Ram Else if Data received after some delay (wait for definite amount of time) then plot the Ram Else Wait for definite amount of time (counter updated after timeout) End if | <Tx transmit the data with delay both at the beginning and in the middle> <Rx receives the data but with delay both at the beginning and anywhere in the middle> | Communication take place (time constraint) | Rx receive the data but with delay (start and In) | - |

References

- Lande, M.R.S.; Ali, D.M.S. Synchronization in Embedded Real-Time Operating Systems. Int. J. Adv. Eng. Res. Dev. 2014, 1. [Google Scholar] [CrossRef]

- Akesson, B.; Nasri, M.; Nelissen, G.; Altmeyer, S.; Davis, R.I. An Empirical Survey-based Study into Industry Practice in Real-time Systems. In Proceedings of the Proceedings-Real-Time Systems Symposium, Houston, TX, USA, 1–4 December 2020. [Google Scholar]

- Walters, S.A. Practical objected-oriented approach for distributed real-time simulation. In Proceedings of the IEEE/AIAA 12th Digital Avionics Systems Conference, Piscataway, NJ, USA, 25–28 October 1993. [Google Scholar]

- Nelson, A.; Goossens, K.; Akesson, B. Dataflow formalisation of real-time streaming applications on a Composable and Predictable Multi-Processor SOC. J. Syst. Archit. 2015, 61, 435–448. [Google Scholar] [CrossRef]

- Tsao, S.L.; Lee, S.Y. Performance evaluation of inter-processor communication for an embedded heterogeneous multi-core processor. J. Inf. Sci. Eng. 2012. [Google Scholar] [CrossRef]

- Gill, S. The diagnosis of mistakes in programmes on the EDSAC. Proc. R. Soc. London. Ser. A. Math. Phys. Sci. 1951. [Google Scholar] [CrossRef]

- Engblom, J.; Girard, G.; Werner, B. Testing Embedded Software using Simulated Hardware. In Proceedings of the 3rd European Congress on Embedded Real Time Software, Toulouse, France, 25–27 January 2006. [Google Scholar]

- Gabauer, J. Test and Validation of the Integrity and Performance of High Speed Interfaces; Course: ENGG7290; The University of Queensland: St Lucia, Australia, 27 June 2019. [Google Scholar]

- Gude, L. High speed digital interface for radar applications. In Proceedings of the International Automatic Testing Conference AUTOTESTCON, Dayton, OH, USA, 21–24 September 1992; pp. 203–205. [Google Scholar] [CrossRef]

- Shen, Y.T.; Freibert, A.; Stergiopoulos, S.; Plataniotis, K. Computing architecture for the portable four-dimensional ultrasound diagnostic imaging system. In Proceedings of the IEEE International Ultrasonics Symposium, IUS, Dresden, Germany, 7–10 October 2012. [Google Scholar] [CrossRef]

- Tan, K.; Liu, H.; Zhang, J.; Zhang, Y.; Fang, J.; Voelker, G.M. Sora: High-performance software radio using general-purpose multi-core processors. Commun. ACM 2011. [Google Scholar] [CrossRef]

- Bandiziol, A.; Grollitsch, W.; Brandonisio, F.; Nonis, R.; Palestri, P. Design of a transmitter for high-speed serial interfaces in automotive micro-controller. In Proceedings of the 2016 39th International Convention on Information and Communication Technology, Electronics and Microelectronics, MIPRO 2016-Proceedings, Opatija, Croatia, 30 May–3 June 2016. [Google Scholar]

- Ruiz-Rosero, J.; Ramirez-Gonzalez, G.; Khanna, R. Field programmable gate array applications-A scientometric review. Computation 2019, 7, 63. [Google Scholar] [CrossRef] [Green Version]

- Patra, P. On the cusp of a validation wall. IEEE Des. Test Comput. 2007. [Google Scholar] [CrossRef]

- Hyunjin, K.; Abraham, J.A. On-chip source synchronous interface timing test scheme with calibration. In Proceedings of the 2012 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 12–16 March 2012; pp. 1146–1149. [Google Scholar]

- Meixner, A.; Kakizawa, A.; Provost, B.; Bedwani, S. External loopback testing experiences with high speed serial interfaces. In Proceedings of the Proceedings-International Test Conference, Austin, TX, USA, 28–30 October 2008. [Google Scholar]

- Yesobu, M. Testing and Debugging of High Speed Serial Interfaces. Int. J. Elec. Comm. Comp. Eng. 2012, 3, 438–441. [Google Scholar]

- Arora, S.; Aflaki, A.; Biswas, S.; Shimanouchi, M. SERDES external loopback test using production parametric-Test hardware. In Proceedings of the International Test Conference, Fort Worth, TX, USA, 15–17 November 2016. [Google Scholar]

- Ichiyama, K.; Kusaka, T.; Ishida, M. A jitter injection module for production test of 52-Gbps PAM4 signal interfaces. In Proceedings of the International Test Conference, Washington, DC, USA, 9–15 November 2019. [Google Scholar]

- Ahn, S.U.; Seo, B.K.; Kim, H.W.; Shin, Y.S.; Kim, H.T.; Oh, G.G.; Kim, Y.D. Cost-Effective Test Method for screening out Unexpected Failure in High Speed Serial Interface IPs. In Proceedings of the International Test Conference, Washington, DC, USA, 26–28 October 2020. [Google Scholar]

- Perrella, S. Development of FPGA-Based, High-Speed Serial Links for High Energy Physics Experiments. EWSHM-7th Eur. Work. Struct. Health Monit. 2014, 3, 443–450. [Google Scholar]

- Mishra, S.; Singh, N.K.; Rousseau, V. System on Chip Interfaces for Low Power Design, 1st ed.; Imprint; Morgan Kaufmann: Waltham, MA, USA, 2015. [Google Scholar]

- Lomaro, S. Testing High-Speed Serial Interface Technology: Is Your Test Solution in Synch? In Proceedings of the Proceedings of the IEEE/CPMT International Electronics Manufacturing Technology (IEMT) Symposium, San Jose, CA, USA, 16–18 July 2003. [Google Scholar] [CrossRef]

- Hong, D.; Cheng, K.T. Efficient Test Methodologies for High-Speed Serial Links; Series: Lecture Notes in Electrical Engineering; Imprint; Springer: Dordrecht, The Netherland; London, UK, 2010; Volume 51. [Google Scholar] [CrossRef]

- Fan, Y.; Zilic, Z. Accelerating Test, Validation and Debug of High Speed Serial Interfaces; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2011; ISBN 9789048193974. [Google Scholar]

- Hoefflinger, B. ITRS: The International Technology Roadmap for Semiconductors. In Chips 2020; Springer: Berlin/Heidelberg, Germany, 2011; pp. 161–174. [Google Scholar]

- Cases, M.; De Araujo, D.N.; Matoglu, E. Electrical design and specification challenges for high speed serial links. In Proceedings of the Proceedings of 7th Electronics Packaging Technology Conference, EPTC 2005, Singapore, 7–9 December 2005. [Google Scholar]

- Global Printed Circuit Board (PCB) Market 2012–2017 and 2018–2023-Growing Demand for High Speed Data and Signal Transmission, and Development of Green PCBs; PR Newswire: Dublin, Ireland, 2018.

- Kandalaft, N.; Attaran, A.; Rashizadeh, R. High speed test interface module using MEMS technology. Microelectron. Reliab. 2015. [Google Scholar] [CrossRef] [Green Version]

- Pcie, University of New Hampshire Inter Operability Laboratory, 2019. Available online: https://www.iol.unh.edu/sites/default/files/brochures/PCIe-Brochure.pdf (accessed on 4 March 2019).

- Test and Certification, Allion, 2019. Available online: https://www.allion.com/logo-certification/ (accessed on 4 March 2019).

- Moreira, J.; Werkmann, H. An Engineer’s Guide to Automated Testing of High-Speed Interfaces, 2nd ed.; Artech House, Inc: Canton St. Norwood, MA, USA, 2016; p. 685. ISBN 9781608079865. [Google Scholar]

- Fan, Y.; Zilic, Z. A versatile scheme for the validation, testing and debugging of high speed serial interfaces. In Proceedings of the IEEE International High-Level Design Validation and Test Workshop, HLDVT, San Francisco, CA, USA, 4–6 November 2009. [Google Scholar]

- Abdennadher, S.; Meixner, A. Why defect based testing works for high-speed I/O interfaces. In Proceedings of the DTS 2020-IEEE International Conference on Design and Test of Integrated Micro and Nano-Systems, Hammamet, Tunisia, 7–10 June 2020. [Google Scholar] [CrossRef]

- Abdennadher, S.; Shaikh, S.A. Practices in High-Speed IO testing. In Proceedings of the European Test Workshop, Amsterdam, Netherlands, 24–27 May 2016. [Google Scholar]

- Fan, Y.; Zilic, Z. BER testing of communication interfaces. IEEE Trans. Instrum. Meas. 2008. [Google Scholar] [CrossRef] [Green Version]

- Arora, H.; Jaliminche, L.N. Design and implementation of test harness for device drivers in SOC on mobile platforms. In Proceedings of the 2015 International Conference on VLSI Systems, Architecture, Technology and Applications (VLSI-SATA), Bengaluru, India, 8–10 January 2015. [Google Scholar] [CrossRef]

- Lee, S.S. External loopback testing on high speed serial interface. In Proceedings of the Proceedings of the 5th Asia Symposium on Quality Electronic Design, ASQED 2013, Penang, Malaysia, 26–28 August 2013. [Google Scholar]

- Ergenc, D.; Onur, E. Poster Abstract: ISDR: SDR-in-the-loop Simulation. In Proceedings of the INFOCOM 2019-IEEE Conference on Computer Communications Workshops, INFOCOM WKSHPS 2019, Paris, France, 29 April–2 May 2019. [Google Scholar] [CrossRef]

- Masood, S.; Khan, S.A.; Hassan, A. Simulating Synchronization Issues on a Multiprocessor Embedded System for Testing. In Proceedings of the 2021 IEEE International Conference on Information Communication and Software Engineering, Chengdu, China, 19–21 March 2021. [Google Scholar]

- Mark Strembeck, U.Z. Scenario-based Component Testing Using Embedded Metadata. In Proceedings of the Testing of Component-Based Systems and Software Quality, Erfurt, Germany, 30 September 2004. [Google Scholar]

- Cockburn, A. Structuring use cases with goals. J. Object Oriented Program. 1997, 10, 356–362. [Google Scholar]

- Fleisch, W. Applying use cases for the requirements validation of component-based real-time software. In Proceedings of the 2nd IEEE International Symposium on Object-Oriented Real-Time Distributed Computing (ISORC’99), Saint-Malo, France, 2–5 May 1999. [Google Scholar] [CrossRef]

- Fleisch, W. Simulation and validation of component-based automotive control software. In Proceedings of the 12th European Simulation Symposium (ESS 2000), Hamburg, Germany, 28–30 September 2000. [Google Scholar]

| Sr. | Identified Synchronization Bugs |

|---|---|

| 1 | Data received at Rx (receiver) with delay. |

| 2 | Data transmission from Tx (transmitter) with delay. |

| 3 | No data transmitted from Tx. |

| 4 | No data received at Rx. |

| 5 | Data overriding during communication |

| 6 | No synchronization |

| ID | Usecase2-3_ IPC _Data Received at Rx with Start Delay |

|---|---|

| Name | Verify receiving data |

| Rationale | The Rx receives the same data as the Tx sends. |

| Actor | System |

| Goal | Check whether or not the data received at the Rx end. |

| Pre-condition(s) | - Tx should be in place—Rx should be in place—There must be a test vector available. |

| Flow of Event | 1. It begins when Tx sends the data. 2. If data receive at the Rx end without any disruption then plot the Ram Else if Data received after some delay (wait for definite amount of time) then plot the Ram Else Wait for definite amount of time (Counter updated after timeout) End if |

| Post-condition(s) | - Rx receives the data but with a delay at the beginning. |

| User Interface | - Two simulators instances |

| Notes | - |

| Data Implications | - Test vectors (Transfer of data from the Tx to the Rx interface (PE 1 to PE2)) |

| Scenario | Data received at Rx with delay. |

| Test Case ID | TC_RX-002-3 |

| Test Scenario | Verify receiving data |

| Test Case | Tx send the data to Rx, but with start delay |

| Pre-Condition(s) | 1. Tx should be in place. 2. Rx should be in place. 3. There must be a test vector available |

| Test Steps | 1. It begins when Tx sends the data. 2. If data receive at the Rx end without any disruption then plot the Ram Else if Data receive after some delay (wait for definite amount of time) then plot the Ram Else Wait for definite amount of time (counter updated after timeout) End if |

| Test Data | <Tx transmit the data> <Rx receives the data but with delay at the beginning> |

| Expected Test Result | Communication take place (time constraint) |

| Post-condition(s) | Data receive at Rx but with start delay |

| Actual Test Result | - |

| Status(Pass/Fail) | - |

| Test Case ID | Test Scenario | Test Case | Pre-Condition(s) | Test Steps | Test Data | Expected Test Result | Post-Condition(s) | Actual Test Result | Status (Pass/Fail) |

|---|---|---|---|---|---|---|---|---|---|

| TC_TX-001-1 | Transmitting data from the Tx | Tx does not send the data to Rx due to some reasons | 1. Tx should be in place. 2. Rx should be in place. 3. There must be a test vector available. | 1. Tx does not transmit the data. 2. If data are not received at the Rx end then Wait for definite amount of time (counter updated after timeout) End if | <Tx does not transmit the data> <Rx does not receives the data> | Unsuccessful Communication | No data receive at Rx | - | - |

| TC_TX-001-2 | Transmitting data from the Tx | Tx send the data with delay (start) to the Rx | 1. Tx should be in place. 2. Rx should be in place. 3. There must be a test vector available. | 1. It begins when Tx sends the data. 2. If data receive at the Rx end without any disruption then plot the Ram Else if Data are not received at the beginning but after some times, data receive (when delay comes, wait for a definite amount of time) then plot the Ram Else Wait for definite amount of time (ounter updated after timeout) End if | <Tx transmit the data with delay (at the beginning)> <Rx receives the data but with delay (at the beginning)> | Communication take place (time constraint) | Rx receive the data but with delay | - | - |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Masood, S.; Khan, S.A.; Hassan, A.; Fatima, U. A Novel Framework for Testing High-Speed Serial Interfaces in Multiprocessor Based Real-Time Embedded System. Appl. Sci. 2021, 11, 7465. https://doi.org/10.3390/app11167465

Masood S, Khan SA, Hassan A, Fatima U. A Novel Framework for Testing High-Speed Serial Interfaces in Multiprocessor Based Real-Time Embedded System. Applied Sciences. 2021; 11(16):7465. https://doi.org/10.3390/app11167465

Chicago/Turabian StyleMasood, Sabeen, Shoab Ahmed Khan, Ali Hassan, and Urooj Fatima. 2021. "A Novel Framework for Testing High-Speed Serial Interfaces in Multiprocessor Based Real-Time Embedded System" Applied Sciences 11, no. 16: 7465. https://doi.org/10.3390/app11167465